AVE you ever tackled a digital design project with vim and vigor—only to find yourself entangled in a morass of logic ones and zeros and a "this goes up, and that goes down" nightmare? If you have, don't despair. There is a much neater, much simpler method than the brute force approach. This article provides a coherent approach to digital design. The method is not a substitute for intuition and practical seat-of-the-pants experimentation, but a tool for getting the end results quickly.

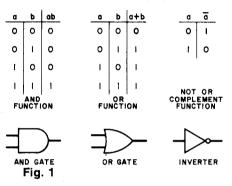

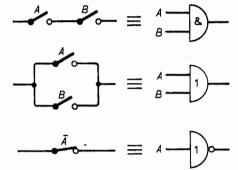

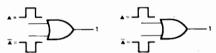

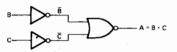

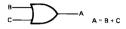

Before getting down to actual techniques, it might be wise to do a little reviewing. The truth tables for the AND, OR, and NOT (or COMPLE-MENT, or INVERTER) functions are shown in Fig. 1. The function a AND b is written ab; a OR b is written a + b; and NOT a is written  $\overline{a}$ . Note that + as defined here is different from ordinary addition, and merely symbolizes

the function defined by the truth table of Fig. 1. A truth table is simply an array, one side of which contains all possible combinations of the input variables and the other side of which contains the corresponding values of a logic function—or output. Figure 1 also shows the digital logic gate symbols for the three functions.

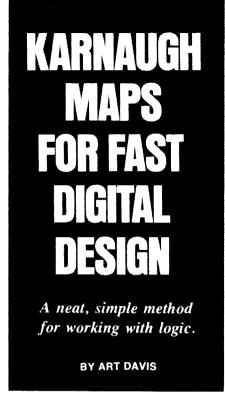

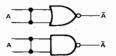

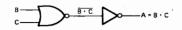

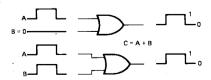

Any logic function can be constructed from these three basic types of functions or gates. It is often convenient, though, when working with a particular type of logic family (TTL, DTL, etc.) to use two other types of function, the NAND and the NOR. The NAND function of a and b is written  $\overline{ab}$ , and the NOR function,  $\overline{a+b}$ . Their truth tables and logic symbols are illustrated in Fig. 2. All of these functions except the NOT, or INVERTER, can be extended in an obvious way to include more than two inputs. With these functions at hand, it becomes possible to construct any logic function desired.

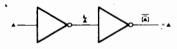

In manipulating the basic functions

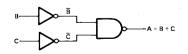

to form more complex ones, it is expedient to have available two important, yet simple, rules of basic logic theory known as DeMorgan's Laws. Figure 3 contains truth tables for the logic functions  $\overline{ab}$ ,  $\overline{a} + \overline{b}$ ,  $\overline{a} + \overline{b}$ , and  $\overline{ab}$ . Comparing them yields the formulas of DeMorgan's Laws:

1)

$$\overline{ab} = \overline{a} + \overline{b}$$

2)  $\overline{a + b} = \overline{ab}$

These formulas are useful in implementing digital functions using only NAND or only NOR gates.

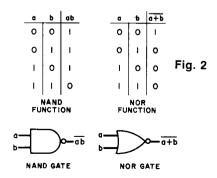

Why Map Techniques? A truth table is one way of specifying a logic function—the Karnaugh map (pronounced Kar-no) is another. To get an idea of what such a map is, and why it is a convenient tool, let's look at a practical digital design problem.

Suppose we are faced with designing the digital black box of Fig. 4, which has three inputs a, b and c, and a single output f(a,b,c). The black box is to provide a logic one output under the following input conditions:

a=b=c=1, a=c=1 and b=0, a=0 and b=c=1, or a=b=0 and c=1. How can we manufacture the digital logic inside the box from this specification?

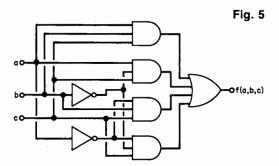

One possible answer is to be methodical. A person unfamiliar with map techniques—but very methodical—might reason in the following way.

'The output function f(a,b,c) is logic one whenever a=b=c=1. An AND gate puts out a one whenever all inputs are logic one, so let's use an AND. But the AND output is zero for all other input combinations, and f(a,b,c) is a one for several other input conditions.

"Well, the AND gate did pretty well for the first input combination, so why not try it for the second? Let's take the complement of b by passing it through an INVERTER and run it into an AND gate with a and c. This AND will put out a one when a=c=1 and b=0, as desired. This seems to be working well, so let's do the same with each of the other two combinations."

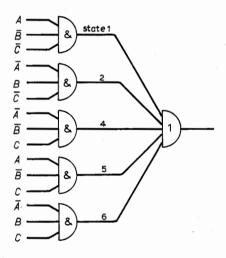

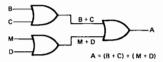

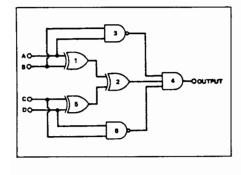

With all the AND gates and INVER-TERs arranged as above, our methodical experimenter will then observe that, since f(a,b,c) is to be a logic one whenever the input variables form the first combination, or the second, or the third, or the fourth, all he has to do is OR the outputs of the four ANDs to generate f(a,b,c). The resulting logic is shown in Fig. 5.

Now this logic design works. It will do the digital job, but it is inefficient. It requires four AND gates, one OR, and two INVERTERs. This is costly, and it would cause quite a few layout problems because of the numerous interconnections. In addition, the design procedure outlined above is slow and, for more complicated circuits, error prone. What can be done to streamline the procedure?

| a     | b                                             | ab  | a   | b | ā+b           |  |

|-------|-----------------------------------------------|-----|-----|---|---------------|--|

| 0     | 0                                             | 1   | 0   | 0 | ı             |  |

| 0     | 1                                             | 1   | 0   | 4 | ı             |  |

| 1     | 0                                             | ı   | ı   | 0 | 1<br>0        |  |

| 1     | ı                                             | 0   | ı   | ı | 0             |  |

|       | $\overline{ab} = \overline{a} + \overline{b}$ |     |     |   |               |  |

|       |                                               |     |     |   |               |  |

| _ a   | ь                                             | a+b | _ a | ъ | αb            |  |

| 0     | 0                                             | ı   | 0   | 0 | $\overline{}$ |  |

| 0     | 0                                             | ı   |     | 0 | $\overline{}$ |  |

| 0 0 1 | 0                                             | ı   | 0   | 0 | $\overline{}$ |  |

| 0     | 1                                             | ı   | 0   | 0 | -             |  |

POPULAR ELECTRONICS

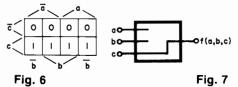

The answer is the Karnaugh map. This is just a rectangle divided up into a number of squares, each square corresponding to a given input combination. The Karnaugh map of our function f(a,b,c) is shown in Fig. 6. The right half of the map corresponds to a=1, the left half to a=0 ( $\overline{a}=1$ ), the middle half to b=1, and so on. The basic idea is that there is one square for each input combination. If we write into that square the value of the output function for that particular input combination, we will have completely specified the function. The ones and zeros in Fig. 6 are the values which f(a,b,c) assumes for the associated input variable combinations.

Now recalling our methodical design procedure, it is easy to see that each square which has a one in it corresponds to the AND function of those input variables, and f(a,b,c) can be generated as the OR function of all of the ANDs.

A key factor arises here. It isn't necessary to include all of these AND functions, and the Karnaugh map tells us how to eliminate some of the terms. For example, looking at Fig. 6, we see that f(a,b,c) is a one for four adjacent boxes forming the bottom half of the map. (We will consider squares on opposite edges to be adjacent.) It is also easy to see the following: The only variable which does not change as we go from one square with a one to another with a one is c. It remains at one. What this means is that f(a,b,c) cannot depend on a and b because, regardless of their values, f(a,b,c) is a one as long as c=1. Therefore we can forget about a and b, and

implement our black box as shown in Fig. 7. We have grouped together the four adjacent squares to eliminate a and b. Notice that we have simplified things a great deal, since we now need no gates at all.

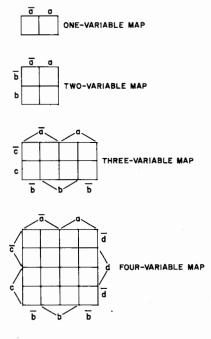

Using a Karnaugh Map. Maps of one, two, three, and four variables are shown in Fig. 8. Maps of one variable are rarely used, and maps with more than four variables are seldom needed—even if such a problem were to chance along, the Karnaugh map would not be the tool to use. Its value depends on the pattern recognition capability of the user, and it becomes hard to recognize pattern groupings in maps of more than four variables.

Using the three-variable map as an example, note that there is one box for abc, one for abc, another for abc, and so on, with abc corresponding to the input combination a=1, b=1c=1;  $a\overline{b}c$  to a=1, b=0, c=1; and  $\overline{a}b\overline{c}$ to a=0, b=1, c=0; etc. Each box, then, corresponds to a single row in the truth table. The map is arranged in such a way that half of it corresponds to the uncomplemented form of a given variable and the other half to its complemented form; and the variables are interleaved so that every input combination corresponds to exactly one square, and conversely. Usually only the uncomplemented form of each variable is written-it being clear that the other half of the map corresponds to the complemented form.

Now, a logic function is displayed by placing ones and zeros in the boxes on the map. If a given input combination produces an output, or function value, of one, a one is placed in the corresponding square on the map. If the output is zero, a zero is placed in the square. As an example, look at the logic function in Fig. 9. On the Karnaugh map, the box given by abc has a 1 in it. This means that f is a logical one when the input variables have the value a=1, b=1, and c=1. The box given by  $ab\overline{c}$  has a 0 in it. This means that f=0 when a=1, b=1, and c=0. These entries, as well as all the others, can be verified by looking at the truth table.

The logic function in Fig. 9 is not at all simple looking. The question is, how can the function be reduced to its simplest form? Variables can be eliminated from the function by use of the following definition and rules:

Definition: Two boxes are adjacent if the corresponding variables differ in only one place, for example if one box corresponds to  $a\overline{b}\overline{c}$  and the other to  $a\overline{b}c$ . Notice that boxes on opposite edges of the map are adjacent under this definition.

Rule 1: If two boxes containing ones are adjacent, the single variable which differs between the two (uncomplemented for one, complemented for the other) can be eliminated and the two boxes combined. These two boxes correspond to the AND function of all the variables except the one eliminated.

Rule 2: If four boxes containing ones are adjacent in such a way that each box is adjacent to at least two others, these boxes can be combined and the two variables eliminated—those two which appear in both complemented and uncomplemented form somewhere within the group. The group of four corresponds to the AND function of all the variables except for the two which have been eliminated.

Rule 3: The same procedure holds for eight, sixteen, and so on, adjacent boxes. Each box in a grouping must be adjacent to three, four, etc., others within that group.

Rule 4: The various AND functions produced by the above groupings are "ORed" together to yield the simplest function.

It should be noted that a given box can be included in more than one grouping if that will simplify the overall function, but each grouping should contain at least one box which doesn't belong to an existing group-

Fig. 8

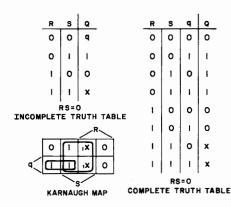

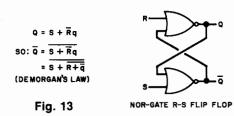

keep from violating the condition that R=S=1 must never occur. Figure 13 also shows how DeMorgan's Law is used to get the function into a form requiring only NOR gates for its construction. By assuming all three possible combinations of input variables (remembering the R=S=1 is disallowed from ever occurring) and computing outputs, the truth table can easily be verified. It is also easy to show in this way that the output labeled Q is, indeed, the complement of the output labeled Q for all input conditions except the disallowed R=S=1.

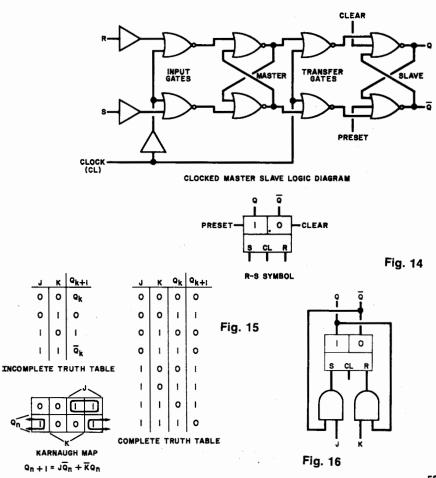

The Clocked R-S Master-Slave Flip-Flop. It is often desirable to have available an R-S flip-flop which changes state only on, for example, the trailing edge (or 1-0 transition) of a clock signal. It is possible to use the Karnaugh map to derive the form of such a flip-flop, but the end result, although economical in number of gates and number of inputs per gate, would not shed much light on the internal workings.

This type of sequential machine is depicted in Fig. 14. When the clock goes high, the R and S inputs are passed through the input gates and stored in the master. When the clock goes low, the input gates are disabled, and the information is coupled through the transfer gates into the slave flip-flop. The function of the preset and clear inputs is evident. Try assuming a set of input values for R and S, and trace the information flow, letting the clock change as described

above, to convince yourself that the unit performs the R-S function.

**The J-K Flip-Flop.** Let's return to our newly developed map technique now and develop the (clocked) J-K flip-flop as a last example. For convenience, since output changes are allowed only on clock transitions, let's denote the unstable state q by  $Q_n$  and the stable state Q by  $Q_{n+1}$ . This is reasonable, because  $Q_n$  is the stable state just prior to the  $n^{th}$  1-0 clock transition, and is the unstable state just afterward, with the flip-flop settling down into the stable state  $Q_{n+1}$  before the next clock transition occurs.

The incomplete and complete truth tables are shown in Fig. 15, along with the Karnaugh map and the resulting simplified function. The J serves as the S and K as the R, respectively, of an R-S flip-flop. The only difference is that the J=K=1 output is now defined  $(\overline{Q}_n)$ .

Let's use the clocked R-S flip-flop to build the J-K from our derived equation. For this purpose, let  $S=J\overline{Q}_n$  and  $R=KQ_n$  be the inputs to the clocked R-S. According to the R-S equation,

$Q_{n+1}=S+\overline{R}Q_n=JQ_n+(\overline{KQ}_n)Q_n$ Now, applying DeMorgan's law to  $\overline{KQ}_n$ , we get  $Q_{n+1}=J\overline{Q}_n+(\overline{K}+\overline{Q}_n)Q_n=J\overline{Q}_n+\overline{K}Q_n+\overline{Q}_nQ_n$ But  $\overline{Q}_nQ_n=0$  always, so  $Q_{n+1}=J\overline{Q}_n+\overline{K}Q_n$  which is the J-K flip-flop equation. Notice that the R-S constraint is satisfied, since

$RS = (J\overline{Q}_n)(KQ_n) = JK(\overline{Q}_nQ_n) = 0$  Fig. 16 shows the construction of the J-K from the R-S using two AND gates. Again, test the operation by assuming a set of conditions for J and K and tracing the logic flow. A glance back at the incomplete truth table will reveal that if J=K=1 (J and K inputs tied to a logic one) the J-K forms a toggle flip-flop.

The preceding examples have been intended to accomplish two things. In the first place, knowledge of the logical operation of the various types of flip-flops is essential in order to use them intelligently in an original design. As a second objective, they have provided an effective demonstration of the economy of thought which results when the Karnaugh may is used in a digital design effort.

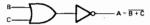

## exclusive-OR gate detects state changes

Signal-driven

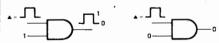

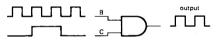

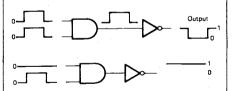

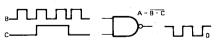

conveniently than can a one-shot, says N. Ghani of the Computer Laboratory at Newcastle University, Newcastle-upon-Tyne, England. A one-shot can directly sense state changes in only one direction, so additional circuitry is needed to handle both positive and perative changes. But a

An exclusive-OR gate can detect a change in state of a logic signal more

circuitry is needed to handle both positive and negative changes. But a quad 7486 exclusive-or gate, driven by the signal and its delayed version, can sense both types of changes. Ghani says. Three of the gates can be used as inverters producing a delay. The fourth is in the exclusive-or mode, taking in the signal and its delayed counterpart. Whenever the input changes state—whether it is positive- or negative-going—the 7486 will produce a narrow negative pulse with a width equal to the delay. If no inverters are used in producing the delay,

then a positive pulse will be generated.

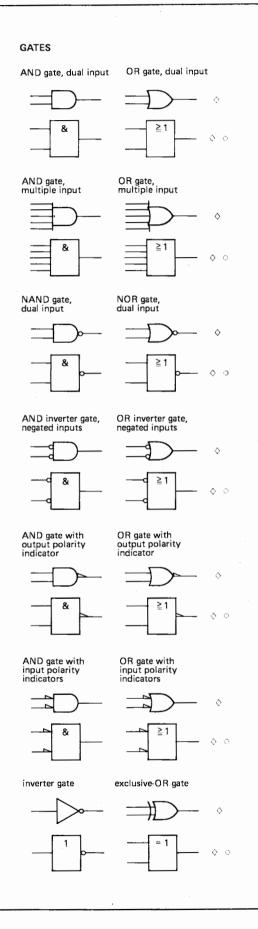

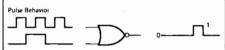

### **Graphic symbols clarified**

A number of readers were apparently confused by the gates section of two-state logic devices in the "Graphic Symbols for Electronics Diagrams," April 3, 1975. To clear up this confusion, the gates section has been modified and reproduced here. It can be clipped out and placed over the original section for an instant revision. To summarize, the revision includes changes in the labels for the inverting-type gates, and the symbols showing polarity indicators (small right triangles) or negation indicators (small open circles) have been separated.

One source of confusion, as a number of readers pointed out, is that either polarity indicators or negation indicators, but not both, should be used on a drawing. The polarity triangle inverts only voltage level and does not invert logic state. The negation circle, on the other hand, inverts only logic state, not voltage level. When the polarity triangle is placed on a line, that line is associated with a logic 1 when the voltage is low.

If a logic drawing makes use of the polarity indicators, there is no need for a statement as to whether the design is based on positive logic or negative logic. However, when negation circles are used, the drawing must state whether the design is employing positive or negative logic.

One other symbol should be modified. The labels for the input terminals to the upper R-S flip-flop are transposed. The letter S should designate the top input line, and the letter R the bottom input line.

Again, as indicated in the introductory comments to the original symbols guide, it is a compilation of those symbols most often needed by today's designer. It is not meant to be a complete listing of all possible symbols and their applications. For such thorough documentation, the standards published by the Institute of Electrical and Electronic Engineers should be consulted. They are: "Graphic Symbols for Electrical and Electronics Diagrams" [IEEE No. 315, 1971]/[ANSI Y32.2, 1970] and "Graphic Symbols for Logic Diagrams (Two-State Devices)," [IEEE Std. 91, 1973]/-[ANSI Y32.14, 1973].

### Engineer's notebook

## DIPs verify strobe within time window

by Robert A. Dougherty

RAD Technical Consulting, Dunedin, Fla.

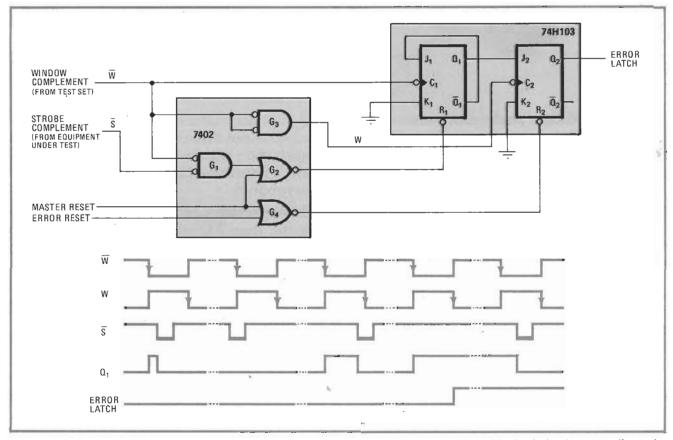

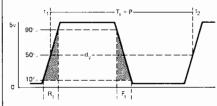

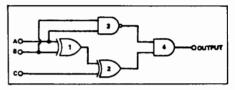

It is often necessary, in testing digital equipment, to ascertain that the equipment under test can deliver a pulse (strobe) during a particular time interval (window). The circuit shown here can verify the presence of a strobe pulse coming from equipment under test during a window pulse from the test set; if the strobe does not appear, an error signal goes high. This circuit operates with no external clock, and uses only two dual-in-line-packaged integrated circuits.

As shown in the diagram, one of the ICs is a dual edge-triggered J-K flip-flop; the other is a quad NOR gate. Assume that both J-Ks are initially in the reset condition—that is,  $Q_1$  and  $Q_2$  are both low. In this case the falling leading edge of a window complement pulse,  $\overline{W}$ ,

sets  $Q_1$  high. Also, the low condition of  $\overline{W}$  enables gate  $G_1$ . Therefore if a strobe complement pulse,  $\overline{S}$ , appears while  $\overline{W}$  is low,  $G_1$  goes high and resets J-K<sub>1</sub> through  $G_2$ .

The output from inverter  $G_3$  is the window pulse, W. Its falling trailing edge clocks the condition of  $Q_1$  (which is also  $J_2$ ) to  $Q_2$ , which is the error latch. Therefore, if  $Q_1$  is low, the error latch stays low. If  $Q_1$  is high, the error latch goes high and remains high until cleared by the error reset or the master reset.

The master reset initializes both J-Ks. The error reset clears the error latch through G<sub>4</sub>.

The timing diagram illustrates the operation of the circuit. Note that the error latch stays low if a strobe is totally within the window, or if it overlaps the beginning and/or end of the window. But if a strobe does not coincide with any portion of the window, the latch goes high; it can ring a bell, light a light, or otherwise indicate that the equipment under test has failed to deliver a pulse when one was required.

Engineer's Notebook is a regular feature in Electronics. We invite readers to submit original design shortcuts, calculation aids, measurement and test techniques, and other ideas for saving engineering time or cost. We'll pay \$50 for each item published.

Checking the windows. Indicating whether digital equipment can deliver a pulse at the proper time, this circuit signals an error if a strobe pulse does not coincide with a window pulse generated by the test station. Note that 74H103 J-K flip-flops are clocked by falling edge of pulse. Gates in the 7402 quad NOR are drawn to indicate their function; by DeMorgan's Theorem, a negative NAND is equivalent to a NOR. Timing diagram shows that error latch goes high on falling edge of window pulse (W) unless strobe pulse has occurred some time during W.

### Designer's casebook

## Circuit adds BCD numbers faster with less hardware

by Dharma P. Agrawal

Federal Polytechnic Institute of Lausanne, Switzerland

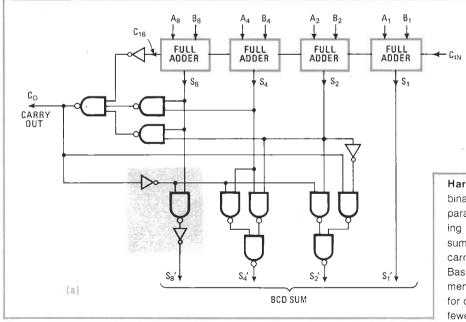

To add two binary-coded decimal numbers, at least four full adders are needed, not to mention the gates and inverters that correct the sums from each adder and generate the decimal carry-out. But this extra logic hardware can be simplified, as has already been shown ["Simplifying sum-correction logic for adding two BCD numbers," by Robert D. Guyton: *Electronics*, May 30, 1974, p. 108], and the new approach proposed here economizes on hardware and improves speed still further.

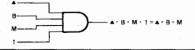

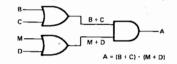

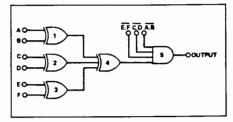

The circuit in the accompanying diagram uses a neat dodge to reduce the number of logic elements required to add the two BCD numbers  $A_8A_4A_2A_1$  and  $B_8B_4B_2B_1$ . The dodge is to obtain the decimal carry-out,  $C_0$ , from the uncorrected sums  $S_2$ ,  $S_4$ , and  $S_8$ , and the uncorrected carry  $C_{16}$  first, and only then to use  $C_0$  to obtain the corrected sums  $S_1'$ ,  $S_2'$ ,  $S_4'$ , and  $S_8'$ .

The boolean expression for the decimal carry-out can be written as

$$C_0 = C_{16} + S_8 S_4 + S_8 S_2$$

The circuit schematic shows how to obtain this value for  $C_0$  by using just three NAND gates and one inverter.

The truth table for the corrected sums  $S_8$ ',  $S_4$ ',  $S_2$ ', and  $S_1$ ' as functions of  $C_0$ ,  $S_8$ ,  $S_4$ ,  $S_2$ , and  $S_1$  can be pre-

pared, and their boolean expressions can be obtained as

$$S_{8}' = \overline{C}_{0}S_{8}$$

$$S_{4}' = S_{4}S_{2} + \overline{C}_{0}S_{4}$$

or

$$= S_{4}S_{2} + \overline{S}_{8}S_{4}$$

$$S_{2}' = C_{0}\overline{S}_{2} + \overline{C}_{0}S_{2}$$

or

$$= C_{0}\overline{S}_{2} + \overline{S}_{8}S_{2}$$

and  $S_{1}' = S_{1}$

The circuit diagram clearly indicates the hardware accomplishment of each of these corrected sums. Note that the portion of (a) that is inside the shaded box can be replaced by the arrangement (b) to produce  $S_8$ ' with one less gate and implement the alternative expressions for  $S_4$ ' and  $S_2$ '.

The numbers in the accompanying table demonstrate how effectively this BCD adder reduces parts count and time delay, compared with some earlier circuits.

|                                   | Excess-3<br>adder | Guyton's adder | Proposed<br>adder (a)<br>shown here | Proposed added<br>(a), partially<br>replaced by (b) |

|-----------------------------------|-------------------|----------------|-------------------------------------|-----------------------------------------------------|

| Number of full adders             | 5                 | 4              | 4                                   | 4                                                   |

| Number of half adders             | 2                 | -              | _                                   | _                                                   |

| Number of 3-input<br>NAND gates   | ]                 | 4              | 1                                   | 1                                                   |

| Number of 2-input<br>NAND gates   | } 20              | 10             | 9                                   | 8                                                   |

| Number of 2-input<br>NOR gates    | -                 | -              | _                                   | 1                                                   |

| Number of inverters               | 9                 | -6             | 4                                   | 3                                                   |

| Time delay in terms of number of: |                   |                |                                     |                                                     |

| Full adders                       | 5                 | 4              | 4                                   | 4                                                   |

| Half adders                       | 2                 | -              | -                                   | -                                                   |

| Gates                             | ?                 | 6              | 5                                   | 4                                                   |

(b)

Hardware economy. Circuit adds two binary-coded decimal numbers with comparatively few logic elements by first obtaining decimal carry-out from uncorrected sums and uncorrected carry, then using this carry-out to obtain the corrected BCD sum. Basic circuit (a) shows fundamental implementation of this method; refinement of logic for corrected sum  $S_8{}'$  (b) saves a gate. With fewer devices, computation is faster.

### Designer's casebook

## NAND gates and inverter synchronize control signal

by Robert L. White

Applied Research Laboratories, University of Texas, Austin, Texas

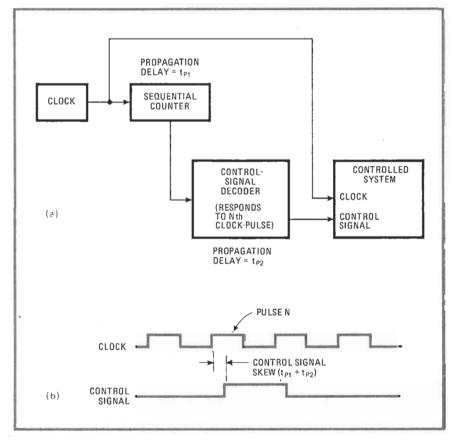

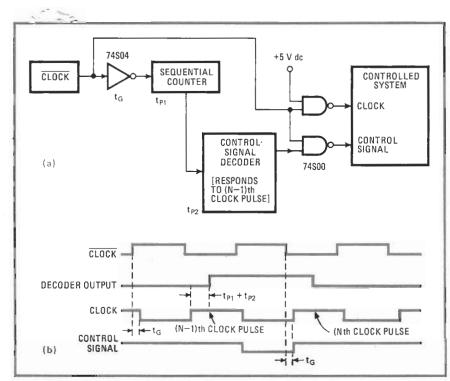

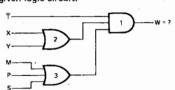

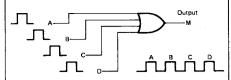

In many sequential digital systems that respond to a rising pulse edge, control signals must be synchronized to the clock pulses. These control signals are usually obtained by decoding the desired states of a sequential counter that is driven by the system clock (Fig. 1a). Since the counter and decoder have propagation delays, the decoded control signal is delayed or skewed relative to the system clock, as illustrated in Fig. 1b. But as the clock frequency of the system gets higher, the skew time may become a significant portion of the clock cycle and cause erratic circuit operation.

One example of this problem is encountered with an accumulator operating with a 15-megahertz clock. On the rising edge of every 40th clock pulse, a control signal transfers data from the accumulator to a data register. The control-signal skew causes the data to be transferred at some instant between the clock edges, rather than at the edges. Since the accumulator output is

changing between clock edges, its value is uncertain at the instant of data transfer, and the system's operation is erratic.

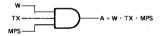

But the skew of the control signal can be reduced to a negligible value by configuring the sequential system as shown in Fig. 2a. The clock of Fig. 1 becomes clock, and inverters are added to the clock line. One inverter is shown as a 74S04, but it could be one gate of a 74S00 IC. The other inverter is the top NAND gate in the 74S00. Also, clock drives an input of a NAND gate in the control-signal line. The decoder in Fig. 2 responds one clock-pulse sooner than the one in Fig. 1.

The synchronizing effect of the inverter and NAND gates can be seen in Fig. 2b. Line 3 shows that the control signal waveform is in the high state until the decoder output goes high. This event occurs at the (N-1)th clock pulse, i.e., one clock period before the rising edge of the control signal.

After the decoder output goes high, the control signal remains high until clock also goes high. After clock goes high, the inputs of the two NAND gates are the same. Therefore, the control-signal and clock waveforms are

alike; their falling edges and the subsequent rising edges virtually coincide at the leading edge of the Nth clock pulse. The only skew remaining is the difference between the propagation delays in the two NAND gates.

With a 74S00 IC, the difference between the delays in

1. Skewed up. In a digital system that requires synchronization of clock and control signal, propagation delays in counter and decoder cause erratic circuit operation. Block diagram (a) shows how control signal is delayed relative to clock pulse, and timing diagram (b) shows waveforms for clock and control signal.

2. Squared away. By adding inverter and NAND gates to circuit and changing decoder to respond one pulse earlier than in Fig. 1, the control signal and clock pulse are synchronized accurately. After rising, the control signal is always high except for the half clock period before its next rising edge.

the two NAND gates was less than 1 nanosecond.

The circuit discussed above provides a control signal with a rising edge that is closely synchronized with the rising edge of the clock. Its applications involve the

transfer of data in high-speed digital systems. The circuit can be used for any application requiring a precisely timed signal transition that does not occur on every edge of the clock pulse.

### **How to Simplify Logic Circuits**

### Introducing the decision-accounts table

by N. Darwood\*

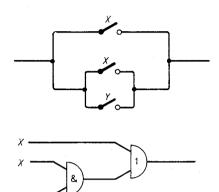

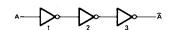

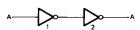

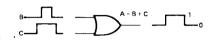

The theory of logical circuits is sometimes called switching logic. This is because the function of a combination of switches, such as is shown in Fig. 1(a), is easily described. Whether the components of which it is finally built are NAND, AND or OR gates or switches, the description of a logical circuit is the same. To explain: two switches in series make an AND gate, Fig. 2(a); two switches in parallel make an OR gate, Fig. 2(b). A switch which is short-circuit when 'on' and open-circuit when 'off' makes a logical inverter, Fig. 2(c).

Although the individual switches of a circuit may switch at electronic speeds, the function, i.e. the logic of the circuit, is described as though it is static and such that there is continuity across the circuit; the circuit is then said to be 'on'. For

Fig. 1. All the possible switch states in these two (equivalent) combinations are shown in the truth table (first two tables in the text).

example, the logic of Fig. 1(a) is: either (A and B) or (A and C) which is written in shorthand as AB+AC. An instance of the usefulness of switching theory is to factorize AB+AC into A(B+C), which is simpler to construct—Fig. 1(b).

In the paper and pencil analysis of a logic circuit, it is sometimes useful to consider all the possible combinations of states of the switches. In the circuit of Fig. 1(b) there are three switches, A, B and C. All the possible states are shown below. Also shown is the condition of the circuit in Figs 1(a) and (b).

| A   | В   | $\boldsymbol{C}$ | AB+AC |

|-----|-----|------------------|-------|

| off | off | off              | off   |

| on  | off | off              | off   |

| off | on  | off              | off   |

| on  | on  | off              | on    |

| off | off | on               | off   |

| on  | off | on               | on    |

| off | on  | on               | off   |

| on  | on  | on               | on    |

Rather than having to write many 'on's and 'off's, it is usual<sup>1</sup> to use 1 for 'on' and 0 for 'off'. Whence the above table becomes

### Truth table for circuits of Fig. 1

| State | A | В | C | AB + AC |

|-------|---|---|---|---------|

| 0     | 0 | 0 | 0 | 0       |

| 1     | 1 | 0 | 0 | 0       |

| 2     | 0 | 1 | 0 | 0       |

| 3     | 1 | 1 | 0 | 1       |

| 4     | 0 | 0 | 1 | 0       |

| 5     | 1 | 0 | 1 | 1       |

| 6     | 0 | 1 | 1 | 0       |

| 7     | 1 | 1 | 1 | 1       |

|       |   |   |   |         |

From the above table we can describe the logic of Fig. 1 as being on when the switches are in state 3 (i.e. 110 in binary form where the least significant bit is on the left), state 5 or state 7. This is the truth-table. One way of designing a logic circuit is to write out the truth-table which shows all the possible states of the switches, then to enter the required 'on' or 'off' circuit condition. Suppose a table as shown below is required.

Truth table 2

| State | A | В | С   |   |

|-------|---|---|-----|---|

| 0     | 0 | 0 | 0   | 0 |

| 1     | 1 | 0 | 0   | 1 |

| 2     | 0 | 1 | 0   | 1 |

| 3     | 1 | 1 | 0   | 0 |

| 4     | 0 | 0 | - 1 | 1 |

| 5     | 1 | 0 | 1   | 1 |

| 6     | 0 | 1 | 1   | 1 |

| 7     | 1 | 1 | 1   | 0 |

|       |   |   |     |   |

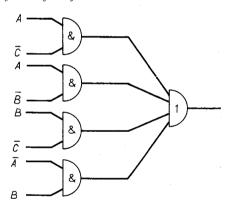

The first step would be to derive a logical expression by extracting the states of the switches A, B and C that will produce an 'on' condition. From the table the circuiton conditions are

states: 1 or 2 or 4 or 5 or 6 logical expression:  $A\overline{B}\overline{C} + \overline{A}B\overline{C} + \overline{A}\overline{B}C + \overline{A}BC$

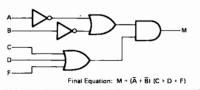

Armed with this expression we can draw the logic diagram. There are five terms in the expression, hence five AND gates which feed into a five input OR gate are needed. The logic diagram is shown in Fig. 3. The logic diagram may now be converted into some other type of logic using, say, NAND

Fig. 2. In writing the logic diagram equivalent of switch diagrams, the notation shown is used.

Fig. 3. To draw a logic circuit, the 'on' condition is normally written from the desired truth table. Truth table 2 gives an expression with five 'on' terms, realised by the logic gates shown.

gates. The conversion technique is a separate branch of logic circuit theory.

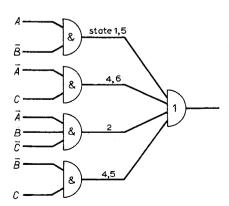

Returning to the logic diagram of Fig. 3, the circuit uses six logical elements. Using the truth-table or the rules of Boolean algebra (for example AB+AC=A(B+C);  $A+\bar{A}=1$ , A+A=A) the full expression can be simplified, for example, to  $A\bar{B}+\bar{A}C+\bar{A}B\bar{C}+\bar{B}C$ . The logic diagram of this expression, logically equivalent to Fig. 3, is shown in Fig. 4. Thus we can have two different, but logically equivalent, expressions one of which is simpler to construct than the other.

The question can be asked—are there other different ways a logical circuit can be built? Many methods exist for finding if a

<sup>\*</sup>Decca Navigator Co. Ltd.

simpler logical expression is possible, e.g. the Harvard method<sup>2</sup>; but they require a knowledge and a skill of Boolean algebra which usually only professional logic designers, or logicians, attain through constant practice.

### **Decision-accounts table**

However, a new approach to the problem is being made, whereby not only are simpler expressions derived but also all the other equivalent expressions can be listed. This gives a complete analysis of the circuit. A table lists all the states to which a particular logic term, such as AC, applies—in this instance states 4 and 6. (See logic tables opposite for three factors.) The table does not contain the states to which expressions apply, found by looking up the states for each term. To illustrate: the expression derived for Fig. 4 is

$$A\overline{B} + \overline{A}C + \overline{A}B\overline{C} + \overline{B}C$$

Enter the tables at the section for three factors A, B and C, with each term, and extract the corresponding state, thus

$$A\overline{B} = 1.5$$

$\overline{A}C = 4.6$

$\overline{A}B\overline{C} = 2$

$\overline{B}C = 4.5$

Therefore the expression, when implemented in hardware, will be on for states 1, 2, 4, 5 or 6, see Fig. 3.

Having found the states that apply to the circuit, to find logically equivalent expressions reverse the procedure by entering the tables with the states 1, 2, 4, 5 and 6, and extract all the terms that apply, as shown below.

### Decision-accounts table 1

|   | Sta          | ate 1        | 10.          |              |            |

|---|--------------|--------------|--------------|--------------|------------|

| 1 | 2            | 4            | 5            | 6            | term found |

| ✓ |              |              | <b>√</b>     |              | ĀB         |

|   | $\checkmark$ |              |              | $\checkmark$ | ĀВ         |

|   |              | $\checkmark$ | $\checkmark$ |              | ВС         |

|   |              | $\checkmark$ |              | $\checkmark$ | ĀC         |

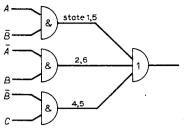

Now as long as we take a combination of these terms that account for all the required states, then that combination will suffice. For example, the three terms AB, AB and BC suffice. The circuit, Fig. 5, uses less hardware than Fig. 4.

The above table is called a decision-

Fig. 4. The logic circuit of Fig. 3 could be simplified by using the rules of Boolean algebra on the logic expression of truth table 2, resulting in five instead of six gates.

Fig. 5. To find other equivalent expressions or logic circuits of Fig. 3, a 'decision-accounts' table is compiled using logic tables which show all the terms that account for the required states. This allows the simpler circuit shown to be drawn.

accounts-table. In conjunction with the logic table, they form a Boolean expression simplification method<sup>3</sup>. The tables are easily derived<sup>4</sup>. This same decision procedure is useful also to programmers and systems analysts who have to formulate and programme complex logical decisions.

By extending the method we look for other expressions, perhaps simpler or perhaps just as simple but different, that will produce the same output for the same combinations of switch states. Because this is a new procedure it may be a little difficult to grasp. One logical law need be used to perform the manipulation. The law is X + XY= X, which allows us to eliminate a term if it is ORed with a factor of itself. The logic diagram of this law is shown in Fig. 6, in terms of switches and gates. If, for clarity, we label the rows of the decision-accounts table P, O, R and S, then a more complex instance of the absorption law, as it is called, could be

$$PQS + PQ = PQ$$

Having drawn up the accounts table, we can now calculate the different ways of constructing the logic of Fig. 3. (The example is purposely obvious to show the reasoning). The accounts table, re-labelled, is

|     |   | 5        | Stat         | e            |   |

|-----|---|----------|--------------|--------------|---|

| Row | 1 | 2        | 4            | 5            | 6 |

| P   | _ |          |              |              |   |

| Q   |   | <b>V</b> |              |              | V |

| R   |   |          | $\checkmark$ | $\checkmark$ |   |

| S   |   |          | <b>V</b>     |              | V |

The first column is accounted for by row P, the second by Q the third by R or S (= R+S)

the fourth by P+R and the fifth by Q+S.

Also we have to account for the first column and the second and the third, and so on. Hence an expression for this par-

ticular decision-accounts table could be

$$P\cdot Q\cdot (R+S)(P+R)(Q+S)$$

which can be expanded to  $(PQR + PQS)(PQ + PS + RQ + RS) = \\ PQR + PQRS + PQRS + PQRS + PQS \\ + PQS + PQRS + PQRS$

= PQR + PQS (by application of the absorption law, X + XY = X). The final expression PQR + PQS shows that either rows P, Q and R or rows P, Q and S may be used to construct the initial logic expression.

Because  $P = A\overline{B}$ ,  $Q = \overline{A}B$  and  $R = \overline{B}C$ , then one expression that could be used is

$$A\bar{B} + \bar{A}B + \bar{B}C$$

or, alternatively, because  $S = \overline{A}C$ , the following expression could be used

$$A\bar{B} + \bar{A}B + \bar{A}C$$

That the alternatives are equivalent to the original may be proved by the truth table,

Fig. 6. In extending the decision-accounts technique the basic Boolean absorptive law X+XY=X is used, which allows elimination of a term which is ORed with a factor of itself.

Fig. 7. In finding equivalent expressions for this circuit, the decision-accounts table 2 shows it can be achieved in either of two ways with one gate less.

or by showing via the logic tables that the three expressions produce the same states, which is the same thing.

### Further example

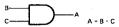

Suppose the example is the circuit shown in Fig. 7; the Boolean expression is derived from the circuit as

$$A\bar{C} + A\bar{B} + B\bar{C} + \bar{A}B$$

Enter the logic tables at the section for three factors A, B and C to extract the states to which each term applies

$$A\bar{C} = 1,3$$

$A\bar{B} = 1,5$

$B\bar{C} = 2,3$

$\bar{A}B = 2,6$

Therefore the expression is ON for states 1, 2, 3, 5 or 6. Next draw up an accounts table. To ease the working the rows are labelled P, Q, R and S.

### Logic tables

| two factors                       |                        |

|-----------------------------------|------------------------|

| $0 = \bar{A}\bar{B}$              | $0, 1 = \overline{B}$  |

| $1 = A\overline{B}$               | $0, 2 = \overline{A}$  |

| $2 = \bar{A}B$                    | 1, 3 = A               |

| 3 = AB                            | 2, 3 = B               |

| three factors                     |                        |

| $0, 1 = \overline{B}\overline{C}$ | $2, 6 = \overline{A}B$ |

| $0, 2 = \overline{A}\overline{C}$ | 3, 7 = AB              |

| $0, 4 = \overline{A}\overline{B}$ | $4, 5 = \overline{B}C$ |

| $1, 3 = A\overline{C}$            | $4, 6 = \overline{AC}$ |

| $1, 5 = A\overline{B}$            | 5, 7 = AC              |

| $2, 3 = B\overline{C}$            | 6, 7 = BC              |

| $0 = \bar{A}\bar{B}\bar{C}$       | $0, 1, 2, 3 = \bar{C}$ |

| $1 = A\overline{B}\overline{C}$   | $0, 1, 4, 5 = \bar{B}$ |

| $2 = \bar{A}B\bar{C}$             | $0, 2, 4, 6 = \bar{A}$ |

| $3 = AB\overline{C}$              | 1, 3, 5, 7 = A         |

| $4 = \overline{A}\overline{B}C$   | 2, 3, 6, 7 = B         |

| $5 = A\overline{B}C$              | 4, 5, 6, 7 = C         |

| $6 = \overline{A}BC$              |                        |

| 7 = ABC                           |                        |

|                                   |                        |

### Decision-accounts table 2

| State |              |              |              |              |   |                 |

|-------|--------------|--------------|--------------|--------------|---|-----------------|

| Row   | 1            | 2            | 3            | 5            | 6 | Term            |

| P     |              |              |              |              |   | ΑĒ              |

| Q     | $\checkmark$ |              |              | $\checkmark$ |   | $A\overline{B}$ |

| R     |              | $\checkmark$ | $\checkmark$ |              |   | ВŌ              |

| S     |              | $\checkmark$ |              |              | ✓ | ĀΒ              |

The accounts table expression is

$$(P+Q)(R+S)(P+R) QS$$

$$= (R+S) QS (P+QR)$$

$$= QS (P+QR) = QSP+QRS$$

The final expressions show we can construct the circuit by either rows Q, R or S, i.e.

$$A\overline{B} + B\overline{C} + \overline{A}B$$

or, alternatively, from rows Q, S and P, i.e.

$$A\overline{B} + A\overline{C} + \overline{A}B$$

On looking back at the accounts table, it is intuitive that to account for each column ('on' state of the switches) at least once, then rows Q and S are essential (called prime-implicants in the literature). Rows Q and S account for states (columns) 1, 5, 2 and 6, leaving state 3 outstanding. With the prime implicants we may choose either

Readers may like to simplify and/or find alternative expressions for the following

row P or row R. Hence Q & S & (P or S) is

the choice of decisions.

### References

- Boole, G. Mathematical Analysis of Logic (1847). Blackwell, 1965.

Bowran, A. P., Boolean Algebra, Macmillan 1965.

- Hohn, F. E. Applied Boolean Algebra, Macmillan, 1966.

- Darwood, N., Representation of Logic Tables, Electronic Engineering, Jan. 1971.

Darwood, N., Simplification of Decision

- 4. Darwood, N., Simplification of Decis Tables, Computer Weekly, 29 July 1971.

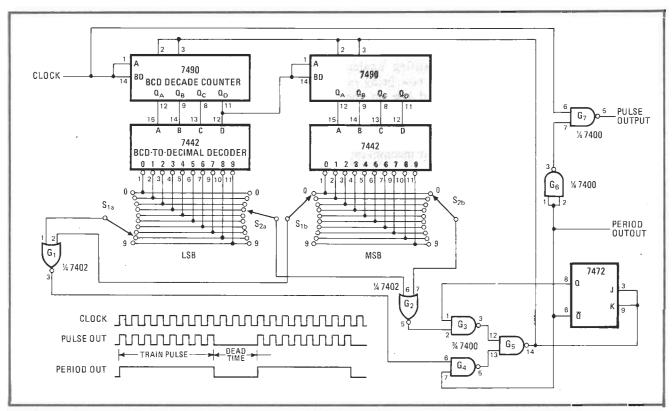

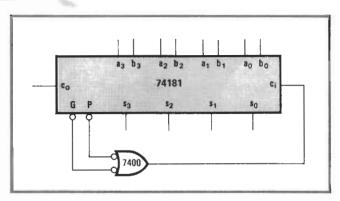

## Counter and switches select pulse-train length and dead time

by Héctor Gellón and Enrique Marcoleta San Luis, Argentina

Only the more expensive pulse generators can repeatedly generate a pulse train of selectable length followed by an off time also of selectable length. But this common requirement is easily met by one cascaded counter, two switches, and some logic. The number of pulses in the train is selectable from 1 to 99, and irrespective of the number of pulses delivered to the output, the off, or dead, time can also be varied between 1 and 99 clock periods. The lengths of both the pulse train and the off time may be extended by adding to the number of stages in the counter.

As shown in the figure, a system clock drives two cascaded 7490 binary-coded-decimal decade counters, and their outputs are converted to a decimal equivalent by the 7442 BCD-to-decimal decoders. The decoded outputs are active low, and when the count reaches the

pulse-train length desired (preset in this case to 8 by switches  $S_{1a}$  and  $S_{1b}$ ), gate  $G_1$  moves high.

If the  $\overline{Q}$  output of the 7472 flip-flop is high, as it will be once the circuit settles after initialization,  $G_4$  moves low. This causes  $G_5$  to assume a high state, resetting the counter and toggling the flip-flop, which in turn disables  $G_4$  and output gate  $G_7$ .

There is no output until the counter reaches the number set by switches  $S_{2a}$  and  $S_{2b}$ .  $G_2$  moves high, causing  $G_3$  to move low and  $G_5$  to go high. The counter is reset, and the flip-flop is toggled, thus once more enabling  $G_4$  and  $G_7$ . The pulse train now appears at the output until the settings of switches  $S_{1a}$  and  $S_{1b}$  are reached, and the cycle repeats.

The  $\overline{Q}$  output of the flip-flop is a signal having a duty cycle that may be anything from 1 to 99 times the period of the system clock. It is essentially an ungated version of the signal at the pulse-output port.

Cascading additional BCD counters and decoders to the circuit will extend its pulse-counting and dead-time limits. Of course, more switches and gates must also be added, to accommodate a greater number of inputs.

Designer's casebook is a regular feature in *Electronics*. We invite readers to submit original and unpublished circuit ideas and solutions to design problems. Explain briefly but thoroughly the circuit's operating principle and purpose. We'll pay \$50 for each item published.

**Selectable.** Generator produces train of N pulse lengths followed by dead time of M clock pulses, set by 2-pole, 10-position switches  $S_{1a}$  through  $S_{2b}$ . N and M may assume any value of from 1 to 99. Switches are shown set for pulse train of 8, dead time of 3.

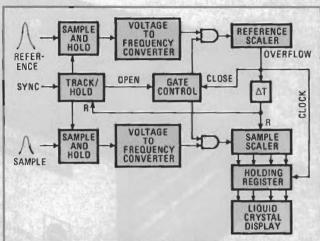

## Digital normalizer derives ratio of two analog signals

by James H. McQuaid University of California, Lawrence Livermore Laboratory, Livermore, Calif.

The absolute value of a voltage or current at a circuit point is frequently less important than the ratio of that quantity to a reference. This circuit compares two analog signals by using a high-accuracy digital technique for normalizing the reference voltage, thus simplifying circuitry and avoiding the use of analog dividers or microprocessors. It is invaluable in many light-chopping applications, such as lasers, where the measurement of light intensity at a specific frequency must take into account total source-intensity variations. It is also useful in atmospheric physics when measuring the concentration of a specific gas in a mixture by infrared techniques in which the intensity of the beam is subject to drift.

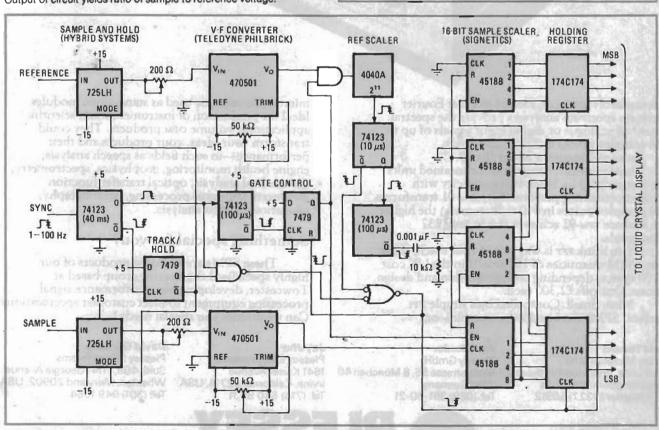

As shown in the block diagram (Fig. 1), the reference and sample signals are each introduced to a sample-andhold circuit. Peak-detection circuitry in this device, in

Ratio meter. Voltage comparison of analog sample to timedependent reference uses analog-to-digital converters. Voltages are converted to frequency and counted. Reference count normalized to unity serves as gating signal to count number in sample counter. Output of circuit yields ratio of sample to reference voltage. conjunction with track-and-hold logic, which controls the sample rate, produces a voltage output that is presented to their respective voltage-to-frequency converters. Each converter's output is a pulse train with a frequency directly proportional to the input voltage.

The track-and-hold logic and associated gating circuits simultaneously initialize both scalar circuits and allow the output pulse train of both converters to be counted. When the count in the reference scaler exceeds its capacity, an overflow pulse is generated that closes the gating circuit; at this time, the contents of the sample scaler are clocked into the holding register and then sent to the display. The contents of the reference scaler are regarded as a unit voltage, and the reference scaler

2. Digital normalization. Circuit detects relationship of analog sample amplitude to reference voltage by digital means. Several one-shots are used to obtain proper timing and gating. Circuit uses C-MOS devices where possible to reduce power consumption.

controls the gating time to the sample scaler. Thus the contents of the holding register will normally be some fraction of the unity-set voltage. The sample scaler and sampling circuits are then reset, ready to process the next sample.

As shown in Fig. 2, the sample-and-hold devices are Hybrid Systems 725LH devices, which are accurate to within 0.01% and have a droop rate of 15 millivolts per second using their internal holding capacitor. The sync input used to control the sampling period is a 5-volt, 1-to-100-hertz pulsed voltage. The converters are Teledyne Philbrick 470501 devices with an upper limiting frequency of about 1 megahertz. This frequency is produced at an input of 10 v, and the device's voltage-frequency characteristic is linear to 0.005%. The converter may be easily calibrated with its 50-kilohm trimmer potentiometer and the 200-ohm rheostat at the output of the 725LH device.

The 4040 reference scaler is a 12-bit binary counter.

After reaching its counting capacity (1,024) during a given sampling period, it clocks the contents of the Signetics 4518B into the 174C174 C-MOS holding register while resetting the gating circuits. The sample scaler capacity (16 bits) and the large reference scaler capacity (12 bits) ensure a high counting accuracy, typically to within 0.1%. In addition, the larger capacity of the sample scaler allows the signal amplitude to exceed the reference amplitude while the correct ratio is still displayed.

The ΔT function in the block diagram is a small but important part of the circuit. It is implemented as shown in Fig. 2 with a number of one shots to achieve correct timing and edge triggering for data transfer. The digitizing time for the circuit shown is 4 milliseconds. Greater speed (with less accuracy) can be easily achieved by reducing the number of bits in the reference scaler. For instance, a digitizing time of 250 microseconds may be achieved with an 8-bit reference scaler.

# Experimenter's Corner

By Forrest M. Mims

### **THREE-STATE LOGIC**

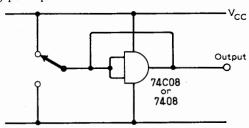

F YOU want to stay abreast of the latest developments in digital logic and microprocessor technology, you need to know something about three-state logic. This month, we're going to experiment with circuits that will teach you the basics of three-state logic in an hour.

Suppose you need to connect the outputs from two or more gates to a common terminal, perhaps the input to another gate. This is OK in the unlikely event *all* the outputs are consistently low or high; but what happens if the outputs are at different logic states? Obviously, it's not possible to place logic 0's and 1's on a common terminal without creating mass confusion—and possibly damaging one or more gates.

Three-state logic provides an efficient solution to this design problem. The output of a conventional logic gate is always low or high as long as power is applied. A three-state gate, however, employs a clever circuit that effectively isolates the gate from the output terminal. This requires that a special control terminal called the enable input be added to the gate.

Figure 1 shows two buffers with threestate outputs. When their enable inputs are activated, these buffers pass the logic state of their inputs to their outputs. When the buffers are not enabled, the outputs enter a high-impedance state. This high-impedance output state means the outputs of a dozen or more buffers (or any other three-state logic gate) can be connected to a common terminal if only one is enabled at any one time.

Many digital circuits, particularly microprocessors and memories, use common terminals called *buses* to transmit binary bits or words (a group of bits). Thanks to three-state logic it's possible to connect many different circuits to a common bus so long as one simple rule is followed: The output of only *one* circuit connected to a bus can be enabled at any one time. If more than one output is enabled, logic 0's and 1's will be placed on the bus at the same time, and we're back to the problem that first caused us to employ three-state logic.

We'll look at three-state buses again later. First, let's get some hands-on experience with a three-state buffer.

### Three-State Buffer Demonstra-

tor. Figure 2 shows a simple circuit you can quickly build on a solderless breadboard to demonstrate how three-state logic works. It uses one of the gates in a 74125 quad three-state buffer. The two LED's indicate the logic state applied to the input of the buffer when the enable input is at logic 0. When LED1 is on, the input is low. When LED2 is on, the input is high.

When the enable input is high, the output of the buffer enters and remains in the high-impedance state irrespective of the logic state at the buffer's input. Both LED's will then glow at about half

Fig. 1. Two three-state buffer configurations (left). Fig. 2. Three-state buffer demonstrater (right).

their normal brightness, conducting a limited amount of current along the path between 5 volts and ground through the series resistors and the LED's.

Here's a truth table that sums up the operation of the demonstrator circuit:

| Enable | Input | Ou   | put  |  |

|--------|-------|------|------|--|

|        |       | LED1 | LED2 |  |

| 0      | 0     | ON   | OFF  |  |

| 0      | 1     | OFF  | ON   |  |

| 1      | 0     | *    | *    |  |

| 1      | 1     | •    | *    |  |

\*Both LED's at half brightness.

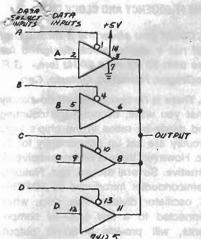

Three-State Multiplexer. A multiplexer is a data selector. Apply an appropriate input select signal and one of several inputs will be applied to a single output. Figure 3 shows how you can make a 4-to-1-line multiplexer from a quad, three-state buffer like the 74125. The enable inputs of the buffers are used as the data select inputs. Remember, only one buffer can be enabled at any one time. With that in mind, here's the truth table for the multiplexer:

| Da | ta l | np | uts | Da | ıta | Se | lect | Output |

|----|------|----|-----|----|-----|----|------|--------|

| A  | В    | Ċ  | D   | A  | В   | С  | D    | •      |

| 0  | Х    | X  | Χ   | 0  | 1   | 1  | 1    | 0      |

| 1  | X    | Х  | Х   | 0  | 1   | 1  | 1    | 1      |

| Χ  | 0    | Х  | Χ   | 1  | 0   | 1  | 1    | 0      |

| Χ  | 1    | Х  | Χ   | 1  | 0   | 1  | 1 .  | 1      |

| Х  | Х    | 0  | Χ   | 1  | 1   | 0  | 1    | 0      |

| Χ  | Х    | 1  | Х   | 1  | 1   | 0  | 1    | 1      |

| X  | Х    | Х  | 0   | 1  | 1   | 1  | 0    | 0      |

| X  | Х    | Χ  | 1   | 1  | 1   | 1  | 0    | 1      |

Note: The  $\chi$  means "don't care"; the input can be either a 0 or 1.

If you build the circuit in Fig. 3, you can apply the data select inputs with a 4-position rotary switch (rotating contact connected to ground) or a 1-of-4 decoder like half of a 74139. The decoder will condense the data select inputs to four 2-bit addresses.

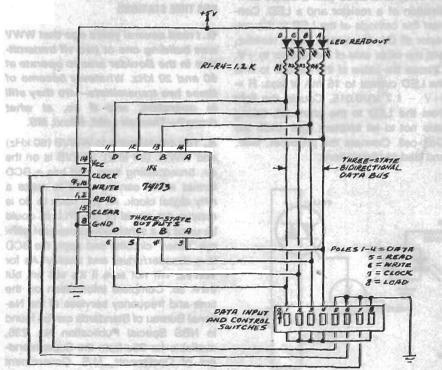

### Three-State Bus Demonstrator.

Figure 4 shows a simple circuit that will teach you how a three-state bus works. The circuit uses a 74173 4-bit data register with a built-in, three-state output buffer. This means you can connect both the inputs and outputs of the register to the same bus (!) and control the transfer of data into and out of the register by applying appropriate signals to the register's read and write inputs.

For best results, build this circuit on a solderless breadboard. Use four rows of adjacent terminal receptacles for the bus and an 8-position DIP switch for the data input and control switch. To write a data word into the register, place the word on the bus by loading it into the first

Fig. 3. Three-state multiplexer.

four poles of the DIP switch (let on = 1 and off = 0) and turning switch 8 on. The LED's will display the word you've switched into the input (LED one = logic 1 and LED off = logic 0).

The register will accept a data word from the bus when the WRITE input is low and the positive edge of a clock pulse arrives at pin 7. Prepare to load the data word into the register by turning switches 6 and 7 on. Then apply a clock pulse by turning switch 7 off. This disconnects the CLOCK input of the 74173 from ground, which is the equivalent of applying a positive pulse (unconnected TTL inputs go high). Don't worry about extra clock pulses from the bouncing that occurs when you throw the switch. The data word is copied on the first ris-

ing bounce, and any subsequent bounces simply recopy the same word.

After the data word is written into the 74173, turn switch 8 off to remove the input data from the bus. Then turn switch 6 off. To see the word stored in the register, just turn switch 5 on. This will activate the READ input of the 74173 and connect the register's output to the bus. This will display the stored word.

Going Further. You can expand the three-state demonstrator by adding a second 74173 to the data bus. You can connect the CLOCK input of the new register to the CLOCK input of the original 74173, but you'll need a couple of switches on a second DIP switch for the additional READ and WRITE inputs.

Can you think of a practical use for the three-state bus demonstrator? A bus system like this can send data between registers in either direction. Therefore, it's often called a bidirectional data bus. If that rings a bell, it's because the bidirectional data bus is used in most microprocessors. In fact the simple three-state bus demonstrator we've been experimenting with is functionally equivalent to part of a microprocessor.

In a real microprocessor, of course, the signals that activate the control inputs of the various registers and circuits are automatically supplied by a circuit called a *controller*. The signals from the controller are binary bit patterns called *microinstructions*.

Fig. 4. Three-state bus demonstrater. MARCH 1978

### Sol small computer systems. They're the real thina.

Use Sol computer systems for scientific and business applications—not just entertainment.

Visit your Sol dealer soon. He can show you how the Sol in conjunction with our new Helios II Floppy Disk System can often do the same job as fast or faster than typical minicomputers at about one-third the price.

Sol systems are complete. Keyboard, interfaces, RAM and ROM memory, and a complete, well written manual are all there. As a standard software package, each Sol comes with our own BASIC/5 language. At modest extra cost, Extended BASIC, Assembler, PILOT, FORTRAN, and FOCAL as well as game software are also available. Processor Technology backs up its products with an excellent warranty and support program after they're out in the field.

Sol 20/8 Terminal Computer with 8192 bytes of RAM memory and SOLOS module (ROM).

Factory Assembled/Tested \$1850 Kit \$1350

Sol System II includes Sol-20/16 with 16,384 bytes of RAM memory and SOLOS module (ROM), video monitor, cassette recorder, and BASIC/5 cassette.

Factory Assembled/Tested \$2250 kit \$1825

Sol System III includes Sol-20 with

49,152 bytes of RAM memory and BOOT-LOAD module (ROM), Helios II Model

2 Floppy Disk System with Extended

Disk BASIC, and video monitor.

Factory Assembled/Tested ..... \$5750

\*Available soon.

### **Processor** Technology

Processor Technology Corporation,

Box 1, 7100 Johnson Industrial Drive,

Pleasanton, CA 94566. Phone (415) 829-2600.

CIRCLE NO 411 ON FREE INFORMATION CARD

### Engineer's notebook

## Capacitance-coupled logic fills unusual jobs

by Stephen R. Pareles

Cook College of Environmental Science, New Brunswick, N.J.

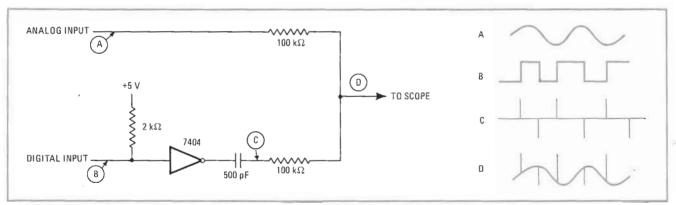

Capacitively coupling logic signals may prove to be a simple way to do several not-so-simple jobs. For instance, capacitive coupling can make short work of bidirectional pulse-edge detection, as well as comparison of an analog signal and a digital signal.

With the circuit of Fig. I and a single-trace oscilloscope, an analog signal and a digital signal can be displayed at the same time, allowing the two signals to be compared or synchronized. The circuit's output is the analog signal with superimposed digital cursors.

The capacitor serves as a bidirectional edge-detector for the buffered arbitrary logic train. Analog-level transients are produced by the capacitor from this input logic train. They are positive for leading pulse edges and negative for trailing pulse edges.

These transients are then cross-coupled with the analog signal through resistors that provide cross-current isolation (100-kilohm resistors are sufficient for most applications). A capacitance of 500 picofarads is ideal for slow horizontal sweep rates of up to about 100 hertz. Smaller capacitance values should be used for faster sweep rates to prevent the trailing edges of the transients from becoming observable.

Capacitive coupling can also be used to perform bidirectional edge-detection when a logic-level output is desired. The detector circuit, which is drawn in Fig. 2, can even handle variable pulse widths.

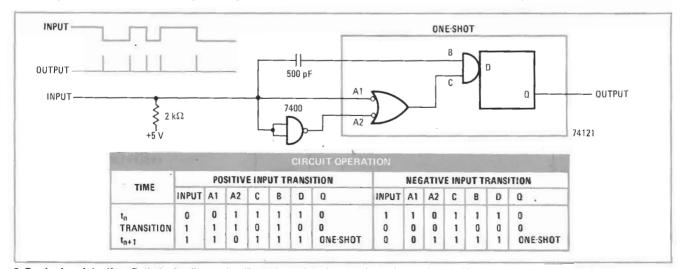

Normally, a 74121-type one-shot is only triggered by a positive transition at point D, following a low condition at points D and Q. When the input first goes high, point A1 goes high. Since point A2 is still high, point C momentarily remains low. When A2 goes low and C high, the one-shot is triggered by the positive edge at D. Point B is kept high throughout.

When the input goes low, A1 goes low before A2 goes high, so that C remains high. Point B, however, is momentarily low. When B goes high again, the one-shot is triggered by the positive edge at C, as before. The tables in Fig. 2 detail the circuit's operation at key points.

1. Two-signal display. A capacitor simplifies the task of observing two signals on a single-trace oscilloscope. The circuit's output becomes the analog input with superimposed digital timing cursors. The two 100-kilohm resistors provide the necessary cross-current isolation.

2. Dual edge-detection. Both the leading and trailing edges of the input-pulse train are detected by this capacitively coupled circuit.

## Appropriate biasing mates ECL and TTL families

by William A. Palm Magnetic Peripherals Inc., Minneapolis, Minn.

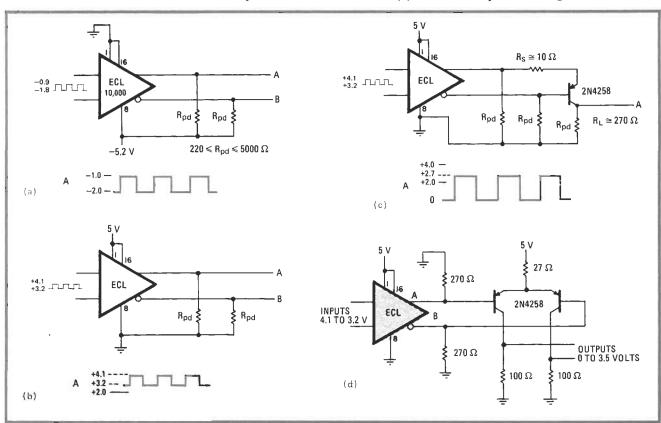

The speed and flexibility of emitter-coupled logic can be combined with the convenience of transistor-transistor logic in circuits that work over a wide range of frequencies. The easiest and most economical way to mate the two logic families is to adapt ECL to the 5-volt operation of TTL, since the rebiasing of ECL elements is easily accomplished. Then the circuits can be powered by a single supply voltage.

Emitter-coupled logic is costly and draws considerable power at higher frequencies. So there is little sense in using it throughout in such a circuit as a 100-megahertz counter/divider, for example, when the part of the circuit that operates at lower frequencies could be implemented with TTL. As shown in (a), the typical dual-output logic gate in the Motorola 10,000 series requires a supply voltage of -5.2 V, conventionally wired as shown in (a). ECL circuitry is so configured that such a

**Evolution of an interface.** Standard emitter-coupled logic is powered by at least one negative voltage, cannot drive or be driven by TTL (a). Re-biased ECL device generates positive output voltage, but not within proper TTL switching threshold range (b). Adding a transistor enables 0-2.7-V swing, suitable for TTL (c). Five-volt ECL gate and two transistors drive 100-ohm TTL loads at 0-3.5 V (d).

gate will operate if there is a supply voltage differential of 5 v between pin 8 and pins 1 and 16, independent of the actual values as long as they are within device limits. Thus, it is permissible to place a 5-v supply voltage at pins 1 and 16 and to ground pin 8 as shown in (b).

This arrangement is not suitable for driving TTL because an input of 3.2 to 4.1 v results in an output voltage swing at point A of only 3.2 v (logic 0) to 4.1 v (logic 1). But note that the voltage at B is the inverted output of A. By using both outputs and adding a transistor to shift the output swing levels (c), approximately 10 milliamperes is made to flow through the 270-ohm collector resistor at point A when the transistor is saturated. Thus there will be a 2.7 v drop across  $R_{\rm L}$  when the

transistor is on, and the voltage will go to zero when the transistor is off, enabling TTL elements (or any other elements, for that matter) to be driven.

The fourth circuit (d) is useful in applications where considerable speed and output current are required to drive a balanced load. There will be a 1-v drop across the  $27-\Omega$  resistor during the time each transistor conducts, and so 35 mA will flow through the  $100-\Omega$  collector resistors. Thus 3.5 v will be developed at each output. This circuit is suitable for driving a  $100-\Omega$  twisted-pair cable.

Engineer's notebook is a regular feature in *Electronics*. We invite readers to submit original design shortcuts, calculation aids, measurement and test techniques, and other ideas for saving engineering time or cost. We'll pay \$50 for each item published.

### Calculator notes

# Standard symbols let designers grasp logic operation quickly and easily

ANSI Y32.14 specifies set of symbols for clearly depicting logic, from gates to systems

by Bill King, Hewlett-Packard Co., Santa Clara (Calif.) Division

The more complex integrated circuits become, the greater the detail in which designers and technicians need to understand their workings. To give them that information at a glance, manufacturers must depict the logic operation of their chips clearly and concisely.

In 1973, therefore, the American National Standards Institute approved and published ANSI Y32.14, which set the logic-symbol specifications for most devices—notably gates, flip-flops, and counters—and for systems containing them. But few users are familiar with the standard, because so far it has been adopted by only two manufacturers—by Hewlett-Packard Co. and, to some extent, by Texas Instruments Inc. Nonetheless, since ANSI does set standards for IC makers, its symbolism is likely to become widely accepted.

| TABLE 1: BASIC LOGIC ELEMENTS |              |                                                                                                                                                 |  |  |  |  |  |

|-------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                        | Function     | Description                                                                                                                                     |  |  |  |  |  |

| <b>→</b>                      | amplifier    | The output will be active only when the input is active (can be used with polarity or logic indicator at input or output to signify inversion). |  |  |  |  |  |

| or &                          | AND          | The output will assume its indicated active state only when all its inputs assume their indicated active levels.                                |  |  |  |  |  |

| → → Or → 1 → 1 → 1            | ÓВ           | The output will assume its indicated active state only when any of its inputs assume their indicated active levels.                             |  |  |  |  |  |

| or = 1                        | exclusive OR | The output will assume its indicated active level if, and only if, only one of the inputs assumes its indicated active level.                   |  |  |  |  |  |

|                               | wired-AND    | This is a connection of outputs of two or more elements that are joined together to achieve the effect of an AND function.                      |  |  |  |  |  |

| <b>D</b>                      | wired OR     | This is a connection of outputs of two or more elements that are joined together to achieve the effect of an QR function.                       |  |  |  |  |  |

ANSI Y32.14 specifies:

Definitions for the basic logic elements.

Logic symbols, which show the defining shapes corre-

sponding to the logic function performed.

Qualifiers, which consist of letters, numbers, or arrows placed inside the logic-device symbol to indicate its logic function or special properties.

Indicators, which show primarily if the input and

output are active high or low.

Dependency notation, which defines the logic-state relationship between the inputs required to activate the device.

Control and contiguous blocks, which integrate with gates, flip-flops, and other elements to form shift registers, counters, and other commonly used devices.

| TABLE 2: SE | LECTED QUALIFIER DESIGNATIONS                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Description                                                                                                                         |

|             | Bilateral switch: a binary-controlled circuit that acts as an on-off switch to analog or binary signals flowing in both directions. |

| > m         | Logic threshold: output will assume its active state if m or more inputs are active.                                                |

| = m         | m and only m: output will be active when m and only m inputs are active (for example, exclusive-OR).                                |

| >n/2        | Majority function: output will be active only if more than half the inputs are active.                                              |

| mod 2       | Odd function: output is active only if an odd number of inputs are active.                                                          |

| 00          | Even function: output is active only if an even number of inputs are active.                                                        |

| x/y         | Signal-level converter: linput llevels are different from output llevels.                                                           |

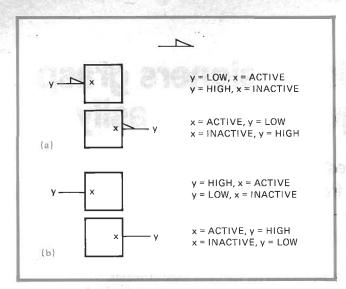

1. Polarity convention. Indicator symbol (top) signifies that corresponding inputs or outputs are active low (a), thereby characterizing circuit operation without use of labeled outputs. The absence of the symbol (b) indicates inputs and outputs are active high.

Table 1 gives the definitions of the basic elements—the amplifier, AND, OR, exclusive-OR, wired-AND, and wired-OR circuits—and their logic symbols. Note that the AND, OR, and exclusive-OR can be shown by their assigned shape or by a rectangle, since the presence of an identifying symbol within those elements specifies the device function. The inverting function for these elements (that is, inverter, NAND, or NOR) is indicated by placing the negation symbol (a small circle) at the corresponding output ports of the devices—the same symbol used currently. In addition to specifying the function of a logic element, qualifier symbols are used for classifying logic blocks. Table 2 shows the symbols

2. Dependency notation. Block-diagram equivalent of two-input AND gate (a), which drives one-shot, provides quick overview of circuit operation. Identifier indicates dependency between inputs a and b, showing data on b is gated in by a. Approach to coding up three-input AND gate follows logical extension of method (b).

for some of the most widely used ones.

The polarity indicator symbol, shown in Fig. 1 (top), establishes the active states of the input leads required to switch on the logic element or indicates whether the output leads are active high or low. Any input or output so labeled is active low (a). Otherwise, the inputs or outputs are active high (b).

Although this symbol provides the same information as the negation symbol, it offers the advantage of visually representing the signal polarity required to activate the device. Furthermore, it eliminates the inconsistent labeling of logic devices. For example, the inverted

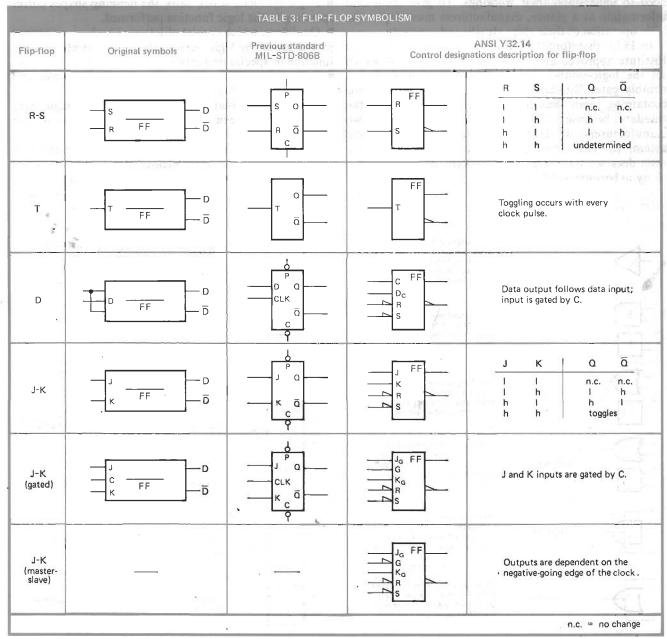

output of a flip-flop is normally designated  $\overline{Q}$ , and the inverted R and S inputs have negation symbols at their ports, rather than being labeled  $\overline{R}$  and  $\overline{S}$ . These ports will now be labeled Q, R, and S with appropriate polarity indicators. This change can be seen in Table 3, which shows the development of flip-flop symbolism.

### **Block form**

By providing for dependency symbols and one-block devices, ANSI Y32.14 makes it easier for system designers to understand the operation of large circuits. So-called control blocks, which group the common control inputs, can be joined to contiguous blocks, which depict the remainder of the circuit (an array of gates, flip-flops, etc.). A combination of control and contiguous blocks forms a device block.

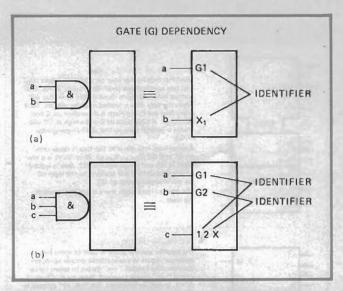

Figure 2 shows the application of dependency symbols. Dependency is indicated by subscripts, prefixes, or suffixes. For example, in the case of  $D_1$ , the 1 indicates a logic connection between the input, D, and a control line assigned the numeral 1. In prefix form, the notation becomes 1D; in suffix form, D1.

In the simple example of Fig. 2a, a two-input AND gate

drives a one-shot multivibrator. The equivalent dependency for the gate is shown to the right. G1 is an input, through which data on line b is gated into the device. The 1 identifies the existence of the relationship between lines a and b, with the letter G defining the type of relationship (AND-gate dependency). The appropriate letter identifies other relationships: A (address), C (control), F (free, or three-state), or V (OR-gate).

Figure 2b, an extension of Fig. 2a, shows how a circuit having a three-input AND gate is coded. G1 and G2 are the gating inputs for data on line c, as indicated by the 1,2 of the input 1,2 X.

### Symbol buildup

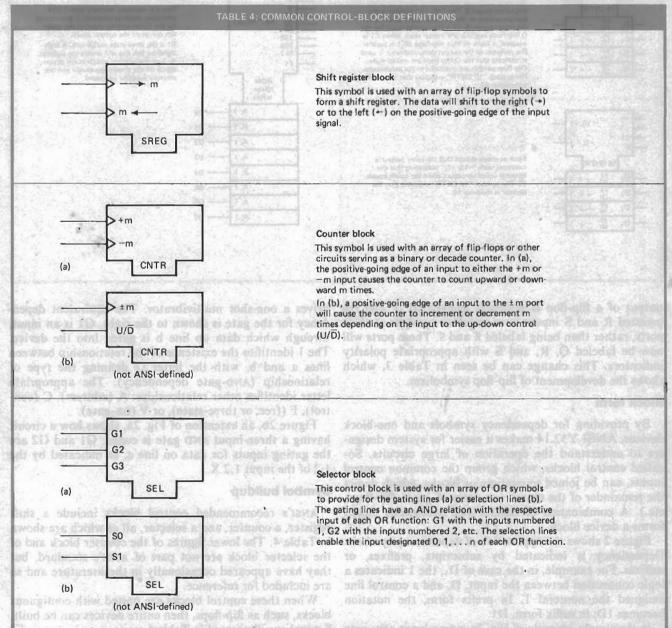

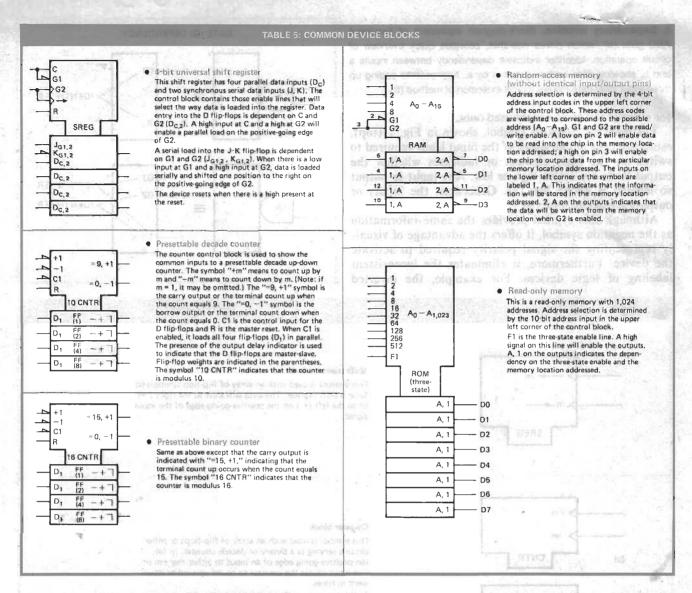

ANSI's recommended control blocks include a shift register, a counter, and a selector, all of which are shown in Table 4. The lower figures of the counter block and of the selector block are not part of ANSI's standard, but they have appeared occasionally in the literature and so are included for reference.

When these control blocks are united with contiguous blocks, such as flip-flops, then entire devices can be built. Several are illustrated in Table 5.

By Forrest M. Mims

### Do-It-Yourself Logic Chips

IN THIS day of ultra-sophisticated semiconductor technology, large-scale and very-large-scale integrated circuits (LSI and VLSI respectively) containing hundreds or even thousands of logic gates have become common-place. Nevertheless, examine any board containing one or more LSI or VLSI chips and you'll probably find an assortment of small- and medium-scale integrated circuits (SSI and MSI) with relatively few gates or flip-flops package.

Circuit designers have long wanted to combine in a few packages the relatively small number of gates and flip-flops required to support most LSI and VLSI chips. Custom ICs are usually out of the question because of their high price and long development time. And what happens if a design change is necessary?

Semi-custom integrated circuits are a better choice. These chips contain arrays of gates which have not been metalized. In other words, the gates are independent of one another since they've not yet been connected together electrically by a metalization pattern on the top surface of the chip. The customer tells the custom IC house how he wants the gates interconnected, and the gate chips are

then metalized according to the customer's specifications and installed in DIPs.

This procedure is faster and cheaper than the custom IC route, but it's still relatively expensive since the customer usually must agree to buy a thousand or more chips. And as in the case of the custom IC, what happens if a design change is necessary?

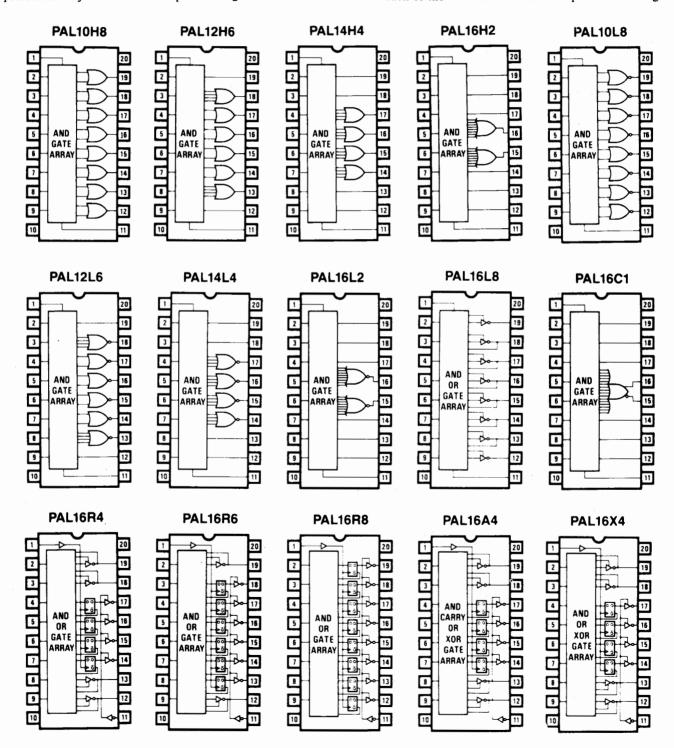

A third alternative is the do-it-your-self logic chip. Included in this category are field programmable logic array (FPLA) and programmable array logic (PAL, a trademark of Monolithic Memories, Inc.) chips. These chips contain arrays of logic gates interconnected via the same kind of fusible links used to make programmable read-only memories (PROMs). By selectively applying high-current pulses to the programming pins of an FPLA or PAL, fusible links can be opened in various patterns to produce a customized integrated circuit.

The PROM is itself a versatile do-ityourself logic chip since it can be used to implement any truth table for which it has sufficient inputs and outputs.

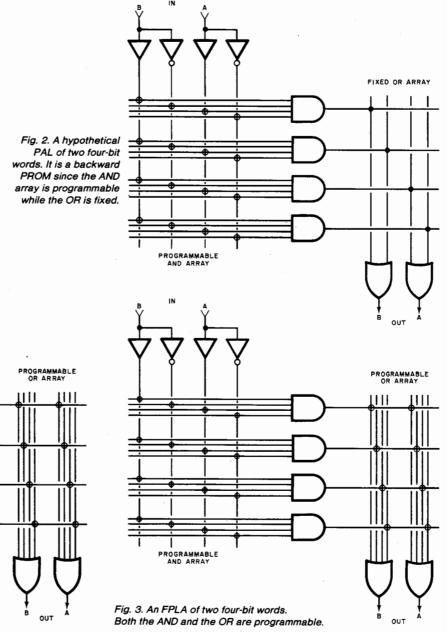

You can better understand the operation and compare the differences of PROMs, FPLAs and PALs be referring to Figs. 1, 2 and 3. They show the internal circuitry of ultra-simple, hypotheti-

80

FIXED AND ARRAY

Fig. 1. A PROM of four two-bit words

The AND array is fixed; the OR is programmable.