## Single hex-inverter IC makes four test gadgets

Raju Baddi, Tata Institute of Fundamental Research, Pune, India

This Design Idea describes a simple way that you can use one hex-inverter package of an unbuffered HD14069UB CMOS (Reference 1) to make four test gadgets: a logic probe with well-defined logic-voltage windows and with an input impedance of approximately 1 M $\Omega$ ; a continuity tester whose upper limiting resistance can be tens of ohms to tens of megohms; a single or train pulse injector or a modest signal generator; and a high-impedance audio probe. You can assemble these gadgets using the six inverter gates of a 4069, two or three transistors, and a few passive components.

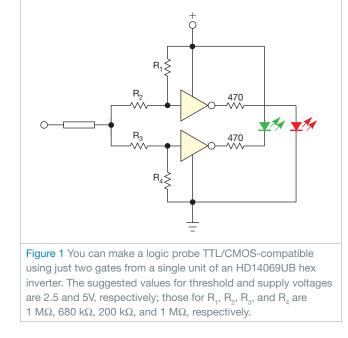

In a two-gate CMOS/TTL-compatible probe, the resistor network comprising  $R_1$  through  $R_4$  biases the inverter's inputs (**Figure 1**). Because of the gates' high input impedance,  $R_1$ through  $R_4$  can have values of approximately 100 k $\Omega$  to 1 M $\Omega$ . The probe's source/sink current is small at the probe tip because of the high resistances of  $R_1$  through  $R_4$ ; as a result, the probe tip essentially does not affect the logicvoltage level at the test point. Knowing the gates' input threshold voltage, you can calculate the required values of resistors  $R_1$  through  $R_4$ .

The upper gate detects logic zero, and the lower gate detects logic one. Set an upper limit to the logic-zero voltage and calculate the values of  $R_1$  and  $R_2$ . Arbitrarily select  $R_1=1 M\Omega$  and seek a value for R<sub>2</sub> such that the voltage at the input of the upper gate is just the threshold voltage. Thus,  $R_2 = R_1(V_T - V_I)/$  $(V_s - V_T)$ , where  $V_T$  is the threshold voltage,  $V_1$  is the logic-zero voltage, and  $V_s$ is the supply voltage. Similarly, set a lower limit on the logic-one voltage  $V_T$ and seek a value for  $R_4$  in terms of  $R_3$ . By appropriately selecting  $R_{1}$ , keeping in mind the quiescent biasing of the gates to keep both the LEDs off in the probe's suspended condition, you can obtain the value of  $R_4$ :  $R_4 = R_3 V_T / (V_H - V_T)$ .

The following equation calculates the probe current:  $I_p=[-(V-V_1)(R_3+R_4)+V_1(R_1+R_2)]/(R_1+R_2)(R_3+R_4)$ , where  $I_p$  is the probe current and  $V_1$  is the probe-tip voltage. It thus follows that the probe impedance for any voltage at the probe tip is greater than 1 M $\Omega$ . For packages of 4069 that exhibit a larger threshold voltage, such as 3V, you can help reduce it by including a diode followed by a 10-k $\Omega$  load resistor to ground in the positive supply rail to the chip.

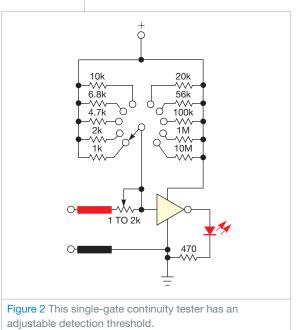

Developers often use continuity testers (Figure 2 and Reference 2) as elementary test gadgets; such testers are indispensable on a work bench. One of the 4069's gates, with its high input impedance and with a threshold voltage for the transition of the output of the gate, allows you to build the continuity tester with an upper limit on the resistance of the test circuit. The total of the resistance between the probes and the resistance in the switching arrangement forms a voltage-divider network, producing a voltage at the input of the gate. When the two resistances are equal, the voltage at the gate input is half the supply voltage. The transition threshold voltage of the gate is also nearly half the supply voltage; therefore, the selected resistor in the switching branch sets the approximate threshold-continuity resistance.

A useful alternative arrangement is to have a variable resistor in place of the switchable resistors. This approach allows you to set the threshold-continuity resistance arbitrarily by adjusting this resistor after including the desired resistance between the probe tips and observing the LED's glow. The variable resistor

## designideas

should be set so that the LED just goes off. This method results in a compact arrangement, which a small package can accommodate. Another variable resistor (1 to 2 k $\Omega$ ) is included in series with the negative probe to make it possible to have a threshold-continuity resistance of approximately  $100\Omega$  or less. You can also use a lower transition threshold voltage for the gate by including a couple of diodes followed by a 10-k $\Omega$  load resistor to ground in series with the positive supply rail. This arrangement can also be used to test for live ac-mains lines (Reference 3) with suitable modification, virtually making five gadgets.

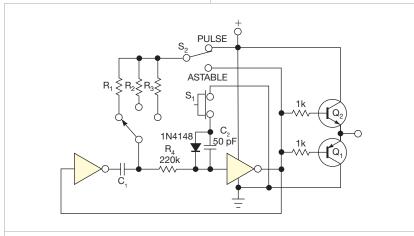

Three gates still remain in the 4069 package; you can use two of them to make an astable oscillator/monostable single-pulse-generator circuit, which a complementary bipolar pair buffers to

increase the drive current (Figure 3). You select between a single pulse or a pulse train with an SPDT (single-pole/ double-throw) switch set to P (pulse) or A (astable). In pulse mode, pressing the switch produces a brief negativegoing pulse at the input to the second gate as C<sub>2</sub> begins charging. The resulting high at the gate output causes a positivegoing pulse at the junction of  $Q_1$  and  $Q_{\gamma}$ . It also is latched, and the switch is debounced by the positive feedback through capacitor  $C_1$ , which begins charging at a time constant that the selection of R<sub>1</sub>, R<sub>2</sub>, or R<sub>3</sub> determines. When the voltage across  $C_1$  equals the threshold voltage, the second gate output returns low, again with positive feedback through C1, driving the second gate input high and ending the pulse.

The diode in parallel with  $C_2$  is

Figure 3 A complementary bipolar pair boosts the output current of the oscillator and the single-pulse generator.

always reverse-biased and serves as a very large-value resistor to discharge C<sub>2</sub>. Assuming a typical diode leakage of 1 nA, the equivalent resistance at 2.5V is about 2.5 G $\Omega$ . The RC discharge time constant of approximately 125 msec is suitable for the human rate of pushing the button.

The values of R<sub>1</sub> through R<sub>3</sub> set the astable frequency or the one-shot's pulse width. The 220-k $\Omega$  resistor at the input of the second gate is included to limit the leakage of current from the capacitor into the gate input when its voltage is below that of ground or higher than V<sub>DD</sub> by 0.6V. The astable produces a frequency of approximately 1/(2.2RC), whereas the threshold voltage of the gate determines the pulse width of the one-shot, which is approximately 0.7 to 1.1RC.

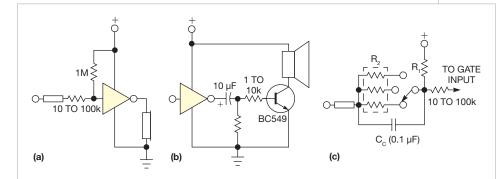

It is sometimes useful to listen to an audio signal at a test-circuit point. The 4069, with its high input impedance and sufficient output drive current of approximately 6.8 mA, can drive a small PCB-mountable speaker. That approach lets you build a simple audio probe (Figure 4). The resistor at the gate input of Figure 4a protects the gate if the unit under test has voltages higher than the gate supply voltage.

Two methods of driving the acoustic transducer are shown, depending on the loudness requirements. Figure 4a shows a direct connection to a piezo transducer. For the louder sound of a speaker, a small resistor can be added in series with the speaker of Figure 4b to control volume and prevent possible speaker or transistor

damage. **Figure 4c** shows an optional method of biasing the gate input for enhanced sensitivity.

The biasing voltage is given by the voltage divider network using this equation:  $V_B = R_2 V_S / (R_1 + R_2) - R_2 V_L (1-\xi) / (R_1 + R_2) - R_2 V_H \xi / (R_1 + R_2)$ , where  $V_S$  is the supply voltage,  $\xi$  is the duty cycle  $(T_H / (T_H + T_L))$  of the input signal (assumed to be a rectangular wave),  $V_H$  is the logic-high voltage, and  $V_L$  is the logic-low voltage. A suggested value for  $R_1$  is 1 M $\Omega$ ; the user can choose  $R_{2}$  (suggested to be 1 M $\Omega$ ) according to the equation for biasing voltage. Various R, values are possible, as the switching arrangement in Figure 4c shows. Capacitor  $C_{c}$  (suggested to be 0.1  $\mu$ F) acts in series with the signal to be investigated and supplies the biasing voltage in series with the signal. The minimum strength of the signal is limited by the input threshold window of the gate and is different for different logic gates. For a rectangular signal changing between zero and the signal voltage, for example, the biasing voltage should be below the threshold window, and the value of the biasing voltage plus the signal voltage should be above the threshold window.

A stringent situation exists when those two values lie just at the edge of the window. So, for a rectangular or attenuated digital signal,  $V_{SIG}=\Delta V_T$  is the minimum required signal strength. In general, gates differ in  $\Delta V_T$ ; some have wide widths (CD4069) and others narrow widths (CD4011). When an ac signal such as a sine wave is applied, however, the negative phase of the signal reduces the biasing voltage by its strength to  $V_B - V_{SIG}$ . It is thus sufficient that one phase produces a change equal to half of the window width. For ac signals, therefore, the minimum signalstrength criterion is  $V_{SIG}=\Delta V_T/2$ . Finally, for an inverting gate,

Finally, for an inverting gate,  $\Delta V_T = V_{T2} - V_{T1}$ , where  $V_{T2}$  is the input voltage at which the output of the gate has completely settled to logic zero, and  $V_{T1}$  is the input voltage at which the output of the gate has completely settled to logic one.  $R_1$  and  $R_2$  help in choosing the critical signal strength above the minimum that the threshold window of the gate has set. If  $R_2$  is approximately 1 M $\Omega$ , then the  $R_2C_C$  time constant is 0.1 sec, which corresponds to 10 Hz and seems to be adequate.

For plain digital signals, it is enough to omit  $R_2$  and  $C_{\rm C}$ ; in other words, both  $R_2$  and  $C_{\rm C}$  equal zero. It should be noted that this coupler does not remedy the stagnant signal condition, preventing a constant drain current at the output. It is intended to provide a typical transistor amplifier kind of biasing for the audio probe gate. The stagnant signal condition is taken care of with a series 10- $\mu F$  capacitor at the gate output of Figure 4b.

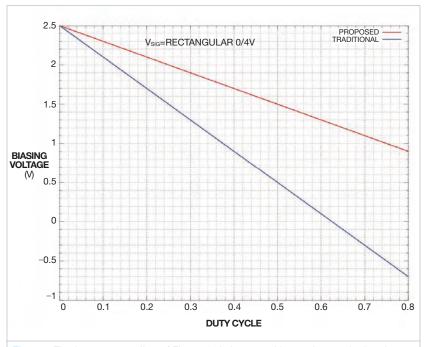

Figure 5 The input ac coupling of Figure 4c is less sensitive to duty cycle than is traditional series-capacitor ac coupling.

Readers interested in using the traditional ac coupling (with the left terminal of R<sub>2</sub> connected to ground instead of the probe tip) RC circuit may use the following formula to calculate the expected  $V_B^{'}$  as a function of various parameters:  $V_B^{'}=V_SR_2/(R_1+R_2)-\xi(V_H-V_L)-V_L$ , where all of the terms have the usual meaning.

Compare this **equation** with the previous **equation**. Whereas the biasing voltage in the **equation** for  $V'_{B}$  depends on  $V_{H}$  or  $V_{L}$  through a single multiplicative factor of the duty cycle, in the **equation** for the biasing voltage it depends on another multiplicative factor,  $R_2/(R_1+R_2)<1$ , thus reducing the dependence and producing a flatter profile with a duty cycle as shown in **Figure 5** for a rectangular wave of  $V_L/V_H=0/4V$  and a varying duty cycle.

You can assemble all of these gadgets in a small container, such as a glue-stick tube, and use the probe for a variety of tests (**Reference 4**). You can power the probe using two 3V CR2032 lithium cells; the CMOS 4069 is a low-power device. Note, however, that 4069 devices from different manufacturers differ widely in their threshold voltages, so you should check that value before selecting a device to make the test gadgets, especially the first three.

The key to these test gadgets is the high input impedance of the CMOS gates. Other packages, such as the CD4011/4001, can also yield multiple gadgets because what matters is the use of the inverter gate.

Editor's note: In all of the circuits discussed here, the probe ground should be connected directly to the unit-under-test ground. Although the Design Idea does not discuss it, some readers might want to add CD4011/4001 NAND/NOR logic to combine the continuity tester, astable oscillator, and audio probe to provide an audio tone for the continuity tester.EDN

## REFERENCES

Funk, RE, "Understanding Buffered and Unbuffered CD4xxxB Series Device Characteristics," Texas Instruments, 2002, http://bit.ly/LJbG5Y.

Baddi, Raju, "Test continuity with an LED," *EDN*, Jan 6, 2011, pg 47, http:// bit.ly/LkaWyk.

Baddi, Raju, "Detect live ac-mains lines," *EDN*, Nov 4, 2010, pg 48, http:// bit.ly/KOCErf.

Baddi, Raju, "Probing system lets you test digital ICs," *EDN*, June 21, 2012, pg 48, http://bit.ly/NhOPgz.