## Add margining capability to a dc/dc converter

Brian Vasquez, Maxim Integrated Products, Dallas, TX

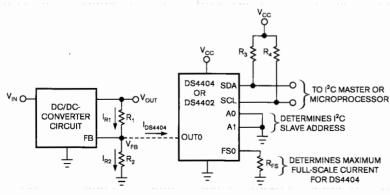

You can easily add margining capability—that is, the ability to digitally adjust the output voltage to a dc/dc converter by making a single connection to the circuit (Figure 1). The dashed line in the figure shows the connection. The extra IC is a twoor four-channel, I2C (inter-integratedcircuit)-adjustable-current DS4402 or DS4404 DAC. Because each DAC output is 0 mA at power-up, the extra circuitry is essentially transparent to the system until you write a command using the I<sup>2</sup>C bus.

For example, assume that the input voltage is 3 to 5.5V; the output voltage is 1.8V, which is the desired nominal output voltage; and the feedback voltage is 0.6V. You can obtain the feedback voltage from the dc/dc converter's data sheet; be sure to verify that it is within the output-voltage range that the current DAC's data sheet specifies as sinking or sourcing voltage depending on whether you are sinking or sourcing current. You should also verify the input impedance of the dc/dc

converter's feedback pin. The circuit in Figure 1 assumes a high impedance.

Assume that you want to add a  $\pm 20\%$ margining capability to the dc/dc converter's output so that the maximum, nominal, and minimum output voltages would be 2.16, 1.8, and 1.44V, respectively. First, determine the necessary relationship between R, and R, which yields the nominal output when the current of the DS4404 DAC is 0 mA:

$$V_{FB} = V_{OUTNOM} \left( \frac{R_2}{R_2 + R_1} \right), \quad (1)$$

where  $V_{FB}$  is the feedback voltage and  $V_{\text{OUTNOM}}$  is the nominal output voltage. Solving for  $R_1$ ,

$$R_1 = R_2 \left( \frac{V_{OUTNOM}}{V_{FB}} - 1 \right).$$

(2

For this example,

$$R_1 = R_2 \left( \frac{1.8V}{0.6V} - 1 \right) = 2 \times R_2.$$

(3)

Summing the currents at the feedback node derives the current to make the output voltage increase to the maxi-

Figure 1 The circuitry to the right of the dashed line adds margining capability.

## DIs Inside

- 56 A better approach to designing an RTD interface with a spreadsheet

- 58 Shunt regulator monitors battery voltage

- 60 Power supply meets automotive-transient-voltage specs

- 60 Locked-sync sine generator covers three decades with low distortion

What are your design problems and solutions? Publish them here and receive \$150! Send your Design Ideas to edndesignideas@ reedbusiness.com.

To see all of EDN's Design Ideas, visit www.edn.com/design ideas.

mum output voltage:

$$I_{R1} = I_{R2} + I_{DS4404},$$

(4)

where  $I_{\rm R1}$  is the current through  $R_{\rm 1}$  ,  $I_{\rm R2}$  is the current through  $R_{\rm 2}$  , and  $I_{\rm DS4404}$  is the current into the DAC.

$$I_{DS4404} = I_{R1} - I_{R2}$$

. (5)

$$I_{R1} = \left(\frac{V_{OUTMAX} - V_{FB}}{R_1}\right); I_{R2} = \left(\frac{V_{FB}}{R_2}\right), (6)$$

where  $V_{OUTMAX}$  is the maximum output

$$I_{DS4404} = \left(\frac{V_{OUTMAX} - V_{FB}}{R_1}\right) - \left(\frac{V_{FB}}{R_2}\right).$$

(7)

You can simplify Equation 7 by solving Equation 1 for R, and then substituting, which yields:

$$I_{DS4404} = \frac{V_{OUTMAX} - V_{OUTNOM}}{R_1}.$$

(8)

In margin percentage, you can express Equation 8 as:

## designideas

$$I_{DS4404} = \frac{V_{OUTNOM} \times MARGIN}{R_1}, (9)$$

where the margin is 0.2 to implement  $\pm 20\%$  margining in this case. Before you can use this relationship to calculate  $R_1$  and  $R_2$ , you must select the full-scale current.

According to the DS4404's data sheet, the full-scale current must be 0.5 to 2 mA to guarantee the specifications for accuracy and linearity. Unfortunately, no formula is available for calculating the ideal full-scale current. The desired number of steps, the step size, and the values for  $R_1$  and  $R_2$  influence that value. Another factor affecting the full-scale current value is whether there is a requirement that a particular register setting corresponds to a particular margin percentage.

In any case, your selection of a full-scale current will likely require several iterations, in which you select an arbitrary value within the range and then calculate R<sub>1</sub>, R<sub>2</sub>, R<sub>FS</sub> (full-scale resistance), and step size. When you've determined an acceptable full-scale-current value, you may want to further adjust it or some of the resistor values to ensure that the resistor values you finally specify are commonly available.

To calculate R<sub>1</sub> for the original example, make the full-scale current equal to the current of the DS4404. This step gives you 31 equal increments, or steps, from the nominal output voltage to the maximum output voltage, as well as 31 steps from the nominal output voltage to the mini-

mum output voltage. This resolution is more than adequate for this example.

You could, for instance, begin by arbitrarily choosing the full-scale current in the center, or 1.25 mA, of the specified range and then performing all the calculations. Instead, for illustrative purposes, the calculations are shown for the endpoints of the range: 0.5 and 2 mA. Analyzing the 0.5-mA case first, you perform the following calculations and then repeat for the 2-mA case.

Using Equation 9 and solving for  $R_1$  yields:

$$R_1 = \frac{V_{OUTNOM} \times MARGIN}{I_{DS4404}} = (10)$$

$$\frac{1.8 \times 0.2}{0.5 \times 10^{-3}} = 720\Omega.$$

$$R_2 = \frac{R_1}{2} = \frac{720}{2} = 360\Omega.$$

(11)

To calculate the full-scale resistance, use the formula and the reference voltage in the DS4404's data sheet:

$$R_{FS} = \frac{V_{REF}}{I_{FS}} \times \frac{31}{4} = \frac{1.23}{0.5 \times 10^{-3}} \times \frac{31}{4} = 19,065\Omega \approx 19 \text{ k}\Omega.$$

$$STEP SIZE = \frac{I_{FS}}{NO. \text{ OF STEPS}} = \frac{1.23}{1.23} \times \frac{1.23}{1.23}$$

$\frac{0.5 \times 10^{-3}}{31} = 16.1 \,\mu\text{A/STEP},$

where  $R_{\rm FS}$  is the full-scale resistance,  $V_{\rm REF}$  is the reference voltage, and  $I_{\rm FS}$  is the full-scale current.

Finally, for completeness, you deter-

mine the DS4404's output current as a function of register setting:

$$I_{OUT}(REGISTER SETTING) =$$

(14)

STEP SIZE × REGISTER SETTING.

Note that this register setting does not include the sign bit, which selects sink or source. The DS4404 sinks current when the sign bit is zero, making the output voltage increase to the maximum output voltage. It sources current when the sign bit is one, making the output voltage decrease toward the minimum output voltage.

Now, you can repeat the calculations for the 2-mA case.

$$R_1 = \frac{V_{OUTNOM} \times MARGIN}{I_{DS4404}} = \frac{1.8 \times 0.2}{2 \times 10^{-3}} = 180\Omega.$$

(15)

$$R_2 = \frac{R_1}{2} = \frac{180}{2} = 90\Omega.$$

(16)

$$R_{FS} = \frac{V_{REF}}{I_{FS}} \times \frac{31}{4} = \frac{1.23}{2 \times 10^{-3}} \times \frac{31}{4} = 4766\Omega \approx 4.7 \text{ k}\Omega.$$

(17)

STEP SIZE=

$$\frac{I_{FS}}{NO. \text{ OF STEPS}} = \frac{2 \times 10^{-3}}{31} = 64.5 \,\mu\text{A/STEP}.$$

(18)

Comparing  $R_1$  and  $R_2$  for the two cases—with a full-scale current of 0.5 or 2 mA—0.5 mA is the more attractive value because the resistances are higher. Edn