### Set 21: Voltage-to-frequency converters.

You may not find many voltage-to-frequency converter circuits classified as such. They are likely as not to be found under such headings as voltage-controlled oscillators, frequency modulators, astable circuits, and even waveform generators, as the following article—an elementary introduction to their operation—points out. Decisions on which kind to use may often centre on linearity. The closed loop designs generally have better linearity, typically 0.1 to 0.5%, than the simpler openloop designs, especially the "charge dispensing" kind, discussed in the article (see, for example, page 19). The unijunction type, page 10, also crops up on pages 116 & 130, and a further  $\Delta\Sigma$  circuit on page 117.

Background article 8 Unijunction converter 10 Multiplier converter 11 Delta-sigma converter 12 Sinewave converter 13 Multiphase converter 14 Monolithic converters 15 Linearized converter 16 Linear converters 17 Diode-pump converter 18 Differential input converter 19 Up-date circuits 20

# Voltage-to-frequency converters

Voltage-controlled oscillators—astable multivibrators—waveform generators frequency modulators: under each of these headings one finds circuits that have an important common property, that the output frequency is a function of some reference or control signal. Such circuits are multi-variable systems in which several parameters of the output waveform are controlled singly or in various combinations by other parameters at the input. Thus the same circuit can appear under different headings depending on which input/output relationship is of priority concern.

8

As an example, some recent integrated circuits have been designed as waveform generators with square/triangle/sine wave outputs. If the output waveform is of no particular concern, the fact that the frequency of each output is proportional to a direct control voltage assumes a greater importance. The circuit can then be called a voltage-controlled oscillator. Now assume that the control voltage is set to a particular quiescent value with a smaller alternating voltage superimposed. Then the output frequency is modulated by the a.c. input, with the carrier frequency corresponding to the quiescent value of control voltage. The label for this circuit is frequency modulator.

In set 21 of Circards the primary property of interest is the relationship between an input voltage or current and the frequency of the output, with much less importance being attached to the wave shape or amplitude. A particularly desirable property is that the voltage-to-frequency relationship be linear, and in extreme cases departures from linearity of as little as 0.01% may be desired. In the process of achieving this, the output pulse height and width may have to be equally well controlled but these are a means to the end and not an end in themselves. There are other cases where the frequency needs to be varied only over a limited range, demanding only a small linear region to the V/f characteristic. A good example is found in the design of v.c.os for high-frequency phase-locked loops. Restriction of the frequency range and of linearity is a compromise accepted more or less willingly in exchange for a speed capability that matches that of the associated digital circuits.

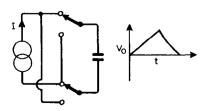

In nearly all of these examples, the basic timing mechanism is that of charging a capacitor from a control voltage or current. The voltage change across the capacitor is sensed by some level-detecting circuit which activates an electronic switch

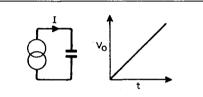

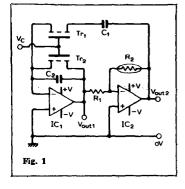

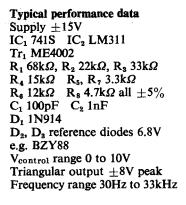

Fig. 1. Constant charging current allows repetition frequency to be made proportional to current.

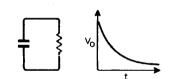

Fig. 2. To cause charging cycle to recommence, a low-value resistor is switched across the capacitor to discharge it quickly.

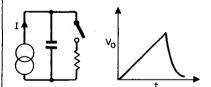

Fig. 3. If discharge time is made small enough the charging current can remain connected. Level of capacitor voltage is used to operate discharge switch.

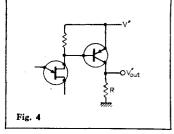

Fig. 4. Triangular waves with repetition frequency proportional to current are produced by reversing capacitor charging current.

to discharge the capacitor and restart the cycle. Two categories of circuit can be clearly distinguished:

• where the discharge time of the capacitor is made short compared with the shortest charging time and need not be under the control of the input voltage, and

• where both charge and discharge times are controlled in common by the input. The first-mentioned circuits produce sawtooth waveforms across the capacitor and short duration output pulses, while the lastmentioned commonly develops a triangular wave across the capacitor, in association with a square wave at a separate output.

These ideas are illustrated in Figs 1 to 4. In Fig. 1, constant current results in a constant rate-of-change of voltage across the capacitor, i.e. the time taken to charge to a given p.d, will be inverse to the charging current. If that level can be sensed and caused to end the cycle or half-cycle, then the repetition frequency (being inverse to the period of the waveform) will be proportional to the current and a linear I/f converter results. The simplest way of causing the cycle to recommence is to place a lowvalue resistor across the capacitor to discharge it in the shortest possible time. If the discharge current is large compared to the charging current, then it is immaterial whether the charging current is disabled or not and Fig. 3 represents the basic principle of many V/f converters, with the switch periodically closing at the instant when the p.d. across the capacitor reaches a defined value.

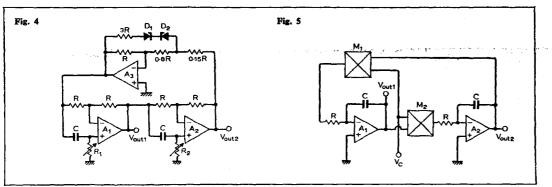

An alternative principle is shown in Fig. 4. The current generator is applied to the capacitor in the reverse direction giving an opposing slope to the ramp but of equal magnitude. The resulting waveform is triangular with the repetition frequency linearly related to the current if the points at which switching is initiated are defined. The provision of a purely electronic two-pole change-over switch is difficult, and the reversal of current direction is more often achieved by using a single-pole switch or its equivalent to control the current generator directly.

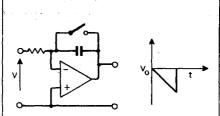

A second problem that often arises is that the changing p.d. across the capacitor affects the nominally constant current. This is obvious in terms of the non-linearity of the ramp, but may not affect the linearity of the

Fig. 5. Using the charging capacitor in an op-amp integrator ensures current is independent of capacitor p.d.

Fig. 6. Simple form of triangularwave generator uses principle of Fig. 5.

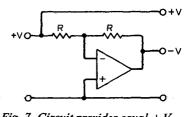

Fig. 7. Circuit provides equal +Vand -V inputs for Fig. 6 with an op-amp of -1 gain.

V/f function provided the waveshape is well controlled, e.g. accurate V/f conversion is possible with simple *R*-*C* charge and discharge circuits though the wave shape is highly non-linear. Where waveshape is also of importance, the capacitor forms part of an operational amplifier integrator circuit, with the virtual earth action ensuring that the charging current is independent of the p.d. The discharge element now has no point connected to ground which can raise problems in activating it. (Fig. 5.)

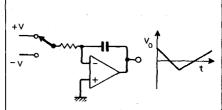

This technique leads to a simple form of triangular-wave generator shown in Fig. 6 where both the +V and -V inputs have to vary together if the slopes are to remain of equal magnitude. By using both the input and the output of an amplifier with a voltage gain of -1 this is readily achieved (Fig. 7). Alternative methods include the design of amplifiers whose voltage gain is switched from +1 to -1, and of integrators in which the direction of capacitor current is reversed by a switch while the magnitude is controlled by a single input voltage.

In all of these circuits there remains the problem of the level sensing circuitry that is to determine the instant of switching; both switching speed and accuracy of level are important making the design of a fast, accurate V/f converter a difficult one.

The term charge-dispensing is a big one in the literature on precision V/f converters. A feedback system is set up in which the output pulses from a generator (basically monostable in form) are arranged to feed back a constant amount of charge for each output pulse. If these units of charge are combined at the input of the system with the control signal, and the overall feedback is negative, then the pulse rate will be proportional to the control signal.

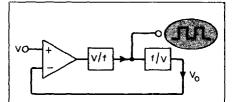

In block-diagram form in Fig. 8, the principle is illustrated by a combination of V/f and an f/V converter. Assuming that the amplifier gain is high, and that the f/V convertor is very linear then the feedback overcomes any non-linearities in the V/f converter, i.e.  $V_o = V$  to a high accuracy because of the feedback while  $V_o \propto f$  ensuring that  $f \propto V$  without reference to the linearity of the V/f converter. The f/V converter might be of the diode-pump variety which with suitable design can transfer a fixed charge into a load for each output pulse rate.

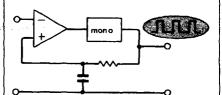

A level-sensing monostable gives an output pulse when the input level rises above a critical value. If the input then falls a second pulse is generated on the next excursion through the set level in the same sense. An important restriction is that the capacitor shall have been completely discharged prior to the second pulse—otherwise the time taken for recharging will be shortened and the output pulse-width reduced. The output of such a monostable would ideally be a train of constant-amplitude constantwidth pulses, which could be smoothed and fed back to the input amplifier as in Fig. 9.

Fig. 8. In this "charge-dispersing" system, a constant amount of charge for each output pulse is fed back so that pulse rate can be proportional to the control signal.

Fig. 9. Monostable circuit produces output pulse when input exceeds a certain level, in either sense.

Fig. 10. An alternative arrangement is to dispense charge into a summing integrator. Output pulse rate is a linear function of control voltage or current.

Fig. 11. Technique of using two current sources, but switching only the one having twice the value of the other, is used in some i.cs.

Fig. 12. Triangular wave generator using technique of Fig. 11. Comparator reference inputs are set to 2V/3 and V/3, the capacitor voltage ranging between these limits.

A better arrangement dispenses these units of charge into a summing integrator— Fig. 10. For positive pulses a negative control voltage is required, the integrator output ramping up until a pulse is produced from the monostable. The charge dispensed into the summing junction causes the output of the integrator to fall, again rising slowly under the action of the control current. On average, the net charge inflow has to be zero, the charge dispensed per pulse is constant and hence the pulse-rate is a linear function of the control voltage/ current.

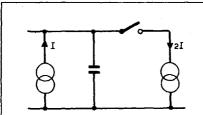

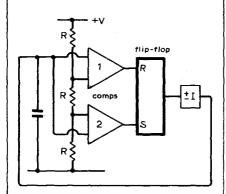

Other recent i.cs revert to the separate constant current circuit for timing circuits and waveform generators, and the resulting I/f linearity can be accurate enough for many applications. One technique is to have two current sources one set by the external control voltage, the other of opposite polarity but of twice the magnitude—Fig. 11. Keeping the former permanently on and switching the latter on and off makes the net current in the capacitor change from +I to -I. A circuit configuration to use this technique to produce a triangular-wave generator is shown in Fig. 12.

Two comparators sense the capacitor voltage, their reference inputs being set to +V/3 and +2V/3 by an internal potential divider. Assume the current at *I*; the capacitor charges until its p.d. reaches +2V/3. Comparator 1 changes its output and resets the flip-flop. This reverses the direction of current flow until the capacitor discharges to +V/3. The comparator 2 operates setting the flip-flop into its original state and restarting the cycle.

9

## Set 21: V to f converters—1

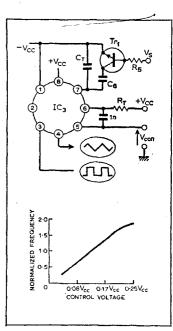

### Unijunction voltage-to-frequency converter

#### **Circuit description**

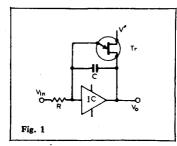

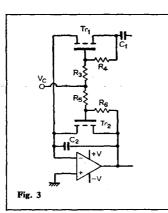

With the removal of the unijunction transistor the circuit of Fig. 1 is simply an integrator which, with a positive  $V_{1n}$ , gives a negative-going ramp  $V_0$ . If the i.c. gain is sufficiently high then  $V_0$  is  $-V_{1nt}/RC$ . The unijunction serves to discharge the capacitor each time the voltage between e and  $b_1$  reaches the unijunction trigger voltage. The circuit therefore

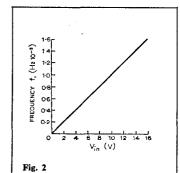

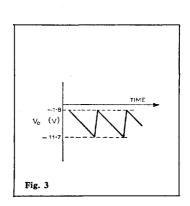

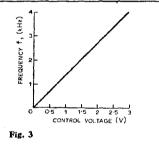

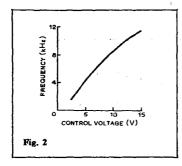

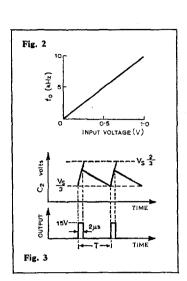

goes through the cycle shown right. Upper limit of -1.8V is the voltage at which the unijunction reverts to being an open circuit. Lower limit of -11.7V is arbitrary and is the result of choosing V', R and C so that  $V_{in} = 10V$  gave a frequency of 1kHz. With  $\pm 15V$ supplies this obviously cannot be extended beyond 15V. The degree of linearity in the plot of frequency against Vin shown in Fig. 2 is quite high e.g. 10V gave 1kHz, 5V gave 498Hz, 1V gave 96Hz and 0.15V gave 16Hz. Rise time of the output waveform (Fig. 1 circuit gave the waveform of Fig. 3) corresponding to the time when C is discharging, was  $15\mu$ s i.e. 1.5% of the period at 1kHz, so the circuit cannot be recommended for much higher frequencies.

But from the expression for the downward ramp it is clear that the same frequency range can be achieved by the use of different values of R and C, and also of V'. It will, of course, be generally desirable to keep R relatively high to give high input impedance. Components IC 741,  $\pm 15V$  supplies Tr 2N2646 C 10nF R 100k $\Omega$ V' 3.3V V<sub>in</sub> see graph V<sub>0</sub> see graph

#### **Circuit modifications**

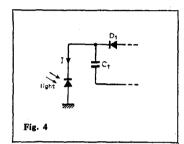

The modification shown in Fig. 4 to the circuitry around the unijunction transistor will provide a pulse train at V'<sub>0</sub>, the frequency being the same as that of the main circuit. The leading edge of this pulse train will correspond to the rising edge of V<sub>0</sub> shown in Fig. 3. This V'<sub>0</sub> will, of course, have the advantage of going much closer to zero in the time between the pulses.

#### An alternative

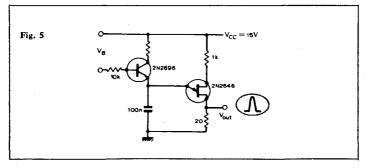

voltage-to-frequency converter reported by Swarup and Banerjee is shown in Fig. 5. It is basically a unijunction oscillator with constant-current drive to the capacitor, this current being proportional to the voltage  $V_B$ . A linear relationship between  $V_B$ and the output frequency is claimed in the range 0 to 500Hz. The basic action of the unijunction oscillator and modifications to reduce the discharge time of C are fully described in Circards set 3 (waveform generators) card 4.

#### Reference

Swarup & Banerjee, Linear voltage to frequency and voltage to pulse width converters using unijunction transistors. *Int. J. Electronics*, vol. 32, 1972, pp. 377-81.

## Multiplier voltage-to-frequency converter

#### Circuit description

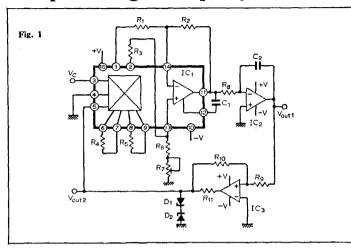

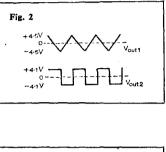

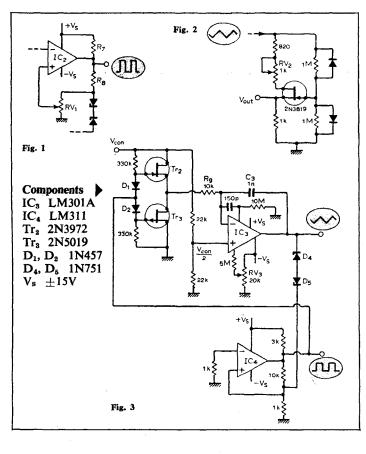

The circuit of Fig. 1 is basically a closed-loop integrator-comparator square-triangle generator, comprising IC<sub>2</sub> and IC<sub>3</sub>, with a multiplier  $(IC_1)$  inserted in the loop to provide control of frequency. The value of the output voltage from the multiplier is a scaled version of the product  $V_{out_2}$  and the control voltage V<sub>c</sub>. Thus the amplitude of the signal to be integrated is directly proportional to a scaled value of the control voltage. A positive voltage applied to the inverting integrator charges C<sub>2</sub> with its output end negative relative to the input end (held close to 0V by negative feedback through C2 and the high gain of IC<sub>2</sub>). Thus, Vout1 goes negative until the current it feeds through R<sub>9</sub> exceeds the positive current in R<sub>10</sub>, resulting in a negative current to the non-inverting input of the Schmitt comparator. Vouta then rapidly switches to a negative value due to positive feedback applied to IC<sub>3</sub>, causing the multiplier output to go negative (V<sub>c</sub> is always positive). The output from the integrator then starts rising until it reaches a positive voltage sufficient to make the comparator change its state again, returning Vout2 and the multiplier output to their original positive values. Hence, Vout1 is a triangular

wave and  $V_{out_2}$  a square wave with frequency linearly dependent on the control voltage

#### **Component changes**

Useful range of supplies:  $\pm 7$  to  $\pm 16V$ . Increase  $C_2$  to reduce upper frequency limit. Useful range of  $V_c$  is about 0 to  $\pm 11V$ . Changing IC<sub>3</sub> to a 301 type op-amp increases slew-rate capability. R<sub>9</sub> can have a wide range of values the lower limit being imposed by heavy loading of IC<sub>2</sub> and the upper limit by the failure of IC<sub>3</sub> to switch before it saturates.

#### Circuit modifications

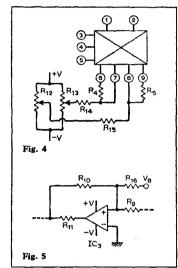

Accuracy of frequency control largely depends on the nonlinearity and offset voltages in the multiplier part of the loop. Output offset adjustment is provided by R<sub>7</sub> and independent adjustment of the offset voltages at the multiplier's X and Y inputs (pins 3 and 5) can be obtained by the 25-k $\Omega$  potentiometers R<sub>12</sub>, R<sub>13</sub> shown in Fig. 4, where  $R_{14}$ ,  $R_{15}$  are 100k $\Omega$ . For a given value of control voltage frequency depends on the scale factor of the multiplier. Adjusting this allows the output frequency to be made a simple linear function

Typical performance Supplies  $\pm 15V$ ,  $\pm 8.5mA$ IC<sub>1</sub> XR2308 IC<sub>2</sub>, IC<sub>3</sub> 741 D<sub>1</sub>, D<sub>2</sub> 3.3V Zeners R<sub>1</sub>, R<sub>3</sub> 22k $\Omega$ R<sub>2</sub>, R<sub>8</sub> 330k $\Omega$  R<sub>4</sub>, R<sub>5</sub> 68k $\Omega$ R<sub>7</sub> 100k $\Omega$  R<sub>8</sub>, R<sub>9</sub>, R<sub>10</sub> 10k $\Omega$ R<sub>11</sub> 2.2k $\Omega$  C<sub>1</sub> 22pF, C<sub>2</sub> 1nF See Fig. 3 for graph of f/V<sub>c</sub> and Fig. 2 for waveforms.

of V<sub>c</sub>. The factor can be adjusted in three ways: (1) by adjusting the op-amp gain in the multiplier block by means of R<sub>2</sub>, (2) by adjusting the gain of the multiplier block by varying R<sub>4</sub> and R<sub>5</sub>, and (3) by connecting the V<sub>out2</sub> signal to the Y input of the multiplier (pin 5) through a

ground-referred potentiometer. • Asymmetry in the output waveforms due to mismatched Zener diodes can be corrected by applying a bias voltage  $V_B$ of suitable polarity to the comparator input via  $R_{16}$ , as shown in Fig. 5. Alternatively, this arrangement with  $V_B = \pm V$ and  $R_{16} = 10 k\Omega$  can be used to purposely introduce a d.c. offset into the output waveforms.

• Other methods may be used to limit the amplitude of the output voltage from the comparator, e.g. by using a diode bridge limiter or by replacing  $IC_3$  with an op-amp of the type providing access to the drive point of its output stage, such as a 748. This allows the comparator output to be

clamped by zener diodes or suitably-biased transistors connected to the output stage drive point.

• For higher frequency operation the multiplier/op-amp block can be replaced by a separate multiplier (MC1495) and inverting amplifier (LM318), the 741-type integrator replaced by an LM318 integrator and the Schmitt replaced by an LM311.

#### Further reading

Graeme, J. G. Applications of operational amplifiers, McGraw-Hill 1973, pp. 161/2. Graeme, J. G., Tobey, G. E. & Heulsman, L. P. Operational amplifiers, McGraw-Hill 1971, pp. 237-51. XR-2208/2308 operational multiplier data sheet, EXAR Integrated Systems Inc. 1972.

Cross references Set 2, card 1

Set 3, cards 1, 5 Set 13, card 9 Set 17, cards 3, 6 Set 21, card 4 11

Set 21: V to f converters-2

### Delta-sigma voltage-to-frequency converter

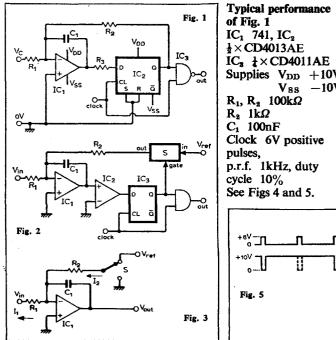

#### **Circuit description**

A class of voltage-to-frequency converter gives an output in the form of a pulse train where the repetition frequency is directly proportional to the instantaneous value of the control voltage but the pulses are generated asynchronously. The output from a delta-sigma encoder is again a pulse train but its average pulse repetition frequency is proportional to the control voltage and the pulses are generated in synchronism with a clock pulse waveform. The basic form of a delta-sigma modulator is essentially a voltage-to-pulse ratio converter (Fig. 3). The circuit maintains a constant voltage across  $C_1$  as the input voltage is varied. which requires that the charging current from the voltage reference source to be switched into  $C_1$  at a repetition rate that attempts to keep the net change in voltage across  $C_1$ at zero. Thus the rate at which the reference current must be switched into the capacitor must be proportional to the input voltage. If the reference current is switched under the control of a stable clock-pulse

generator the output pulses will be proportional to  $V_{in}$  and synchronized with the clock pulse source. Assuming that the net voltage across  $C_1$  is zero, that  $V_{in}$  is negative, that  $V_{ret}$  is positive and  $IC_1$  is a high-gain op-amp then  $I_1=I_3$ ,  $V_{out}$  (mean) =0 and  $I_{out}$  (mean)=0. As the inverting input of  $IC_1$  is a virtual earth,  $I_1=V_{in}/R_1$  and  $I_2=kV_{ret}/R_3$  where k is pulse duty cycle required to keep  $I_2=I_1$ . Equating these currents gives

$$\frac{V_{\rm in}}{R_1} = k \frac{V_{\rm ref}}{R_2}$$

where k is the ratio of the output pulse repetition rate (f) to the clock pulse repetition rate ( $f_e$ ). Hence

$$f = \left(\frac{R_2 f_c}{R_1 V_{ref}}\right) V_{in}.$$

By making  $R_2 = R_1$  and  $V_{in(max)} = V_{ref}$  the maximum output p.r.f. is that of the clock source and the average output pulse rate is proportionally smaller for smaller values of  $V_{in}$ . The arrangement of Fig. 2 uses an analogue transmission gate to realize the switch S.

IC<sub>2</sub> is a precision comparator which determines when the reference voltage source is to be switched to R<sub>2</sub> by monitoring the polarity of the output from the integrator  $IC_1$ . This switching action is synchronized to the clock pulses by using gating pulses derived from the output of a D-type flip-flop which receives the comparator's output at its data input. The circuit of Fig. 1 is that to which the typical performance data refers. This is a simplified form of the arrangement previously discussed with the electronic switch, separate reference source and precision comparator removed. (Note that whilst the integrator used both positive and negative

supplies the D-type flip-flop is connected only across the positive supply.) As the D-type produces output pulses equal in amplitude to the  $V_{DD}$  rail voltage only when its data input receives a positive pulse from the integrator, a separate switched reference is not essential. Also, the precision comparator can be replaced by R<sub>3</sub> which limits the negativegoing pulses to the data input of the D-type which acts as the comparator. Average frequency/Vc graph (Fig. 4) has a linearity of  $\pm 0.1\%$  up to  $f=f_{\rm c}$  when  $V_{\rm c}=V_{\rm DD}$ . No further increase in frequency is possible except by increasing the p.r.f. of the clock source. Output pulse waveform of Fig. 5, inverted by IC<sub>3</sub>, is of  $V_{\rm c} = V_{\rm DD}/2$ , the dashed pulse only being present when V<sub>c</sub> is raised to VDD. The circuit of Fig. 6 is another

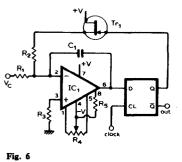

simplified form of the more general system where the comparator had been omitted and the electronic switch is realized by a junction f.e.t. The positive supply rail is used as the voltage reference source and the output is taken from the Q terminal of the D-type flip-flop IC<sub>2</sub>, which is a complementary m.o.s. version to conserve power. This circuit is capable of linear v-to-f conversion within  $\pm 0.05\%$ almost independently of temperature changes. Typical values are: V ±2.7V

$\begin{array}{ll} IC_1 & LM4250C \\ IC_2 & \frac{1}{2} \times MC14013CL \\ R_1, R_2, R_3, R_4 & 100k\Omega \\ R_5 & 5.6M\Omega, C_1 & 100nF \\ Tr_1 & 2N4396 \end{array}$

#### Further reading

Defreitas, R.Low-cost way to send digital data, *Electronics Design*, pp. 68-73, Jan. 18. 1974 Ross, P. J. Simple accurate voltage to frequency converter. *Jnl. of Physics E*, vol. 7, pp. 706/7. Alusten, B. Calculate with a v-f converter, *Electronics Design*, June 7, 1974, pp. 130-2.

13

### Sinewave voltage-to-frequency converters

#### **Circuit description**

This circuit (Fig. 1) is one of the many forms of Wien bridge oscillators with Tr1 and C1 forming the series-connected frequency-dependent arm with  $Tr_{a}$  and  $C_{a}$  forming the parallel connected arm of the bridge. For oscillation to occur the closed-loop gain must be unity, the required amount of gain being provided by the inverting operational amplifier IC<sub>2</sub>, the gain being determined by the ratio  $R_2/R_1$ . With this configuration the commonpoints of the frequencydetermining resistors are connected to the virtual-earth inverting input of IC<sub>1</sub>. This is a convenient arrangement for replacing these resistors with elements which have a resistance that can be controlled by a ground-referred voltage source. In the above circuit these elements take the form of a pair of matched c.m.o.s. transistors which have gatesource resistances that depend

Typical performance Supplies  $\pm 15V$ IC<sub>1</sub>, IC<sub>2</sub> 741 Tr<sub>1</sub>, Tr<sub>2</sub> 1/6×CD4007AE R<sub>1</sub> 150 $\Omega$ R<sub>2</sub> thermistor type R13 C<sub>1</sub>, C<sub>2</sub> 100nF V<sub>out1</sub> 520mV pk-pk V<sub>out2</sub> 1.04V pk-pk See graph for f/V<sub>c</sub> (Fig. 2)

on the control voltage V<sub>c</sub>. Linearity of the voltage-tofrequency conversion characteristic is not particularly good over a wide range of frequencies but may be adequate for many purposes where only a restricted frequency range is required. Resistance of the f.e.ts depends on their drain-source signal voltages as well as on the control voltage Vc but this can be reduced, and the linearity of f.e.t. resistance-to-control voltage characteristic linearized, by using local feedback around the f.e.ts as shown in Fig. 3, where  $R_8$ ,  $R_4$ ,  $R_5$  and  $R_6$  may be of the order of  $1M\Omega$ . If the closed-loop gain deviates from unity the amplitude of oscillation will vary with time, so to avoid extremely precise setting of gain it is initially set slightly high and then automatically controlled the a.g.c. being achieved with a thermistor in the above circuit. In addition to the use of local feedback on the f.e.ts. these elements could be connected to form only part of the frequency-determining resistances with bulk of the values in the form of seriesconnected resistors which would tend to swamp out the non-linearities in the f.e.t. whilst restricting the range of control.

The f.e.ts could be replaced by matched photoconductive resistors or by bipolar transistors which are switched on and off by current pulses to the bases, the mean collectoremitter resistance being controlled by the pulse repetition frequency. A voltage-to-frequency converter using a pair of all-pass active networks is shown in Fig. 4. These networks, using  $A_1$  and  $A_2$ , have a constant gain magnitude but a phase shift given by  $\phi_1 = -2\tan^{-1}(\omega CR_1) - 180^\circ$  and  $\phi_2 = -2\tan^{-1}(\omega CR_2) - 180^\circ$ respectively. With the 180° phase shift through the a.g.c. amplifier A<sub>3</sub> the circuit will oscillate at a frequency  $1/(2\pi C\sqrt{R_1R_2})$ Hz, which shows that a voltage-to-frequency conversion may be obtained by making  $R_1$  or  $R_2$  or both voltage-dependent resistors, e.g. f.e.ts. For a wide range of frequency variations R<sub>1</sub> could be a voltage-dependent resistor and R<sub>2</sub> a range-switching resistor. For  $R = R_1 = R_2$  the outputs are generated with a controllable phase difference  $\phi = (\phi_1 - \phi_2) = -2\tan^1(\omega CR).$ Circuit of Fig. 5 uses two active integrators and two multipliers to produce a voltage-tofrequency converter having quadrature outputs that can have a very fast response to changes in Vc provided a fast a.g.c. system is added to the basic circuit. Under this condition the circuit will oscillate at a frequency which allows the double integration to take place without changing the amplitude of the signal. Multiplier M<sub>2</sub> provides an output  $V_2 = + V_c V_{out_1}/10$  and  $M_1$  gives an inverted output, to maintain the loop phase shift, of  $V_1 = -V_c V_{out_2}/10$ . With the 1/10 scaling factor, frequency of oscillation is  $V_{\rm c}/20\pi RC$ . Multiplier M<sub>1</sub> could be replaced by an inverting operational amplifier.

#### Further reading

Von Ow, H: P., Reducing distortion in controlled attenuators using FETS. *Proc. IEEE*, 1968, pp. 1718/9.

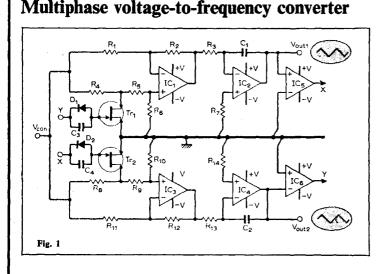

## Set 21: V to f converters-5

#### **Circuit description**

This is a twin circuit based on R-C integration to provide the triangular waveform and level sensing to provide a square wave which operates an electronic switch controlling polarity applied to the integrator. Outputs X and Y are cross-connected giving control of electronic switches Tr<sub>2</sub> and Tr<sub>1</sub> respectively and triangular waveforms which are 90° out of phase. IC<sub>5</sub> and IC<sub>6</sub> provide high open-loop gain, and at low frequencies provide faster switching than comparators. Vout1 is a positive-going ramp until Tr<sub>1</sub> changes state and this occurs at the instant of zero-crossing of Vout<sub>2</sub>, which then switches  $IC_6$ .  $V_{out_1}$  then ramps down and changes the state of Tr, when a zero-crossing point is reached. The time taken to go from say a positive peak to zero level depends on the RC time constant and the value of V<sub>control</sub>. It should be noted that as no amplitude controls for the output are imposed, one or other of the integrators

will reach saturation before the other output reaches its zero crossing point.

#### **Circuit modifications**

• Use a switched integrator rather than a switched gain amplifier. This makes IC1, IC3 redundant (Circard Set 3, No. 5). LM3900 quad package may be now arranged to provide the two outputs. Phase shift oscillator (above) provides three outputs with 60° phase relationship.  $IC_1 - IC_3$ : 1/6×CD4049, R:  $10k\Omega$ , C: 2700pF, frequency: 13kHz. As the c.m.o.s. gates are being used in their linear region, both the n- and p-type transistors will be conducting and hence power consumption will depend on the supply voltage. Typically the total current drain from the supply for the above network is  $V_{\rm DD} - V_{\rm SS} = 3V$  $I_{\rm T}=0$  $V_{\rm DD} - V_{\rm SS} = 10 {\rm V}$  $I_{\rm T}=12{\rm mA}$  $V_{\rm DD} - V_{\rm SS} = 15 \rm V$  $I_{\rm T}=30{\rm mA}$ Frequency may be controlled by substituting voltagedependent resistors for each R<sub>1</sub>

and maintaining as close a ratio as possible between the R values. Frequency is approximately 1/3RC. Note that with the CR values necessary for 60° phase shift at a specific frequency, the output of each buffer stage is attenuated by about one half and hence the minimum gain of each stage must be > 2. An alternative arrangement is shown above right, using similar c.m.o.s. buffer inverters. In this case the resistor ratio is critical and theoretically for infinite gain amplifiers  $R_2 = R_1/2$ and a much better approximation to sinusoidal outputs is obtainable from each buffer, again phase shifted by 60°. Typical values  $R_1$ :100k $\Omega_2$ R<sub>2</sub>: 33 to 39kΩ, C: 2700pF,  $V_{\rm DD} - V_{\rm SS} = 6V$ , frequency 1kHz.

These buffers have gainfrequency responses which give higher gains for lower supply voltages. Typically 50dB at +3V up to 100Hz, and 30dB at +10V up to 100kHz. Hence since the gains are finite, then  $\mathbf{R}_2$  must be less than  $R_1/2$ . But at the lower values of the supply range 3 to 15V, some flexibility of this value between each  $R_2$  is permitted. At higher levels the ratio is more critical, R<sub>2</sub> may be replaced by f.e.ts employed as v.c.r. to obtain a restricted frequency range.

#### Further reading

Voltage controlled two-phase sawtooth oscillator. Wireless World, June 1973, p. 285. AN-88 CMOS Linear Applications, National Semiconductor, p. 170. Frequency controllable 3-phase sinewave generator, Electronic Engineering, July, 1974.

**Cross references** Set 11, card 6. Set 8, card 1.

## Set 21: V to f converters-6

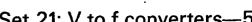

### Monolithic voltage-to-frequency converters

#### **Circuit description**

6.5

An emitter-coupled astable multivibrator uses a single capacitor for timing. The circuit has high switching speed because charge storage effects are avoided by using the transistors in a non-saturated mode. This circuit is the basis of the above medium-scale integration package, where variable frequencies are Typical data IC  $\frac{1}{2}$ SN74S124N C<sub>1</sub> 220pF  $V_s = V'_s$  +5V d.c. Frequency range 0.7 to 1.8MHz (approx. linear)

obtained by charging the external capacitor at different rates via an internal voltage-controlled current source. The i.c. package contains two identical networks, but if only one is being used, it is essential that both ground connections (pins 8 & 9) are earthed to ensure earthing of the substrate and good isolation. The enable terminal

(no. 11) must be grounded for continuous output at the output terminal. Output is disabled if this terminal is taken to logic high or open-circuited. Graphs opposite indicate linearity over a restricted range for each capacitor value, and waveform deteriorates at very low values of  $C_1$ , and thus at high frequencies.

#### **Circuit modification**

Emitter-coupled astable output swings are usually restricted. An additional output stage supplied via V's permits the output swing to be approximately 0V up to V's and hence t.t.l. compatibility is easily achieved, i.e. V's and Vs need not be the same.

Variable-capacitance diodes

may provide a wider frequency range, depending on type (see over). Supply voltage 4.5 to 6.5V, frequency maintained constant.

Supply  $\pm 10V$ IC<sub>1</sub> SH74S124N IC<sub>2</sub> LM301 R<sub>1</sub> R<sub>2</sub> 10k $\Omega$ R<sub>3</sub> R<sub>4</sub> 100k $\Omega$ C<sub>2</sub> C<sub>3</sub> 1 $\mu$ F C<sub>4</sub> C<sub>5</sub> MV16408

$IC_2$  is connected as a non-inverting amplifier with a voltage gain of two, so that the biasing voltage in this case is twice the control voltage. This gain can be altered for appropriate voltage range. A claimed frequency range of 2 to 20MHz using varactors MV1403 and MC1456 for  $IC_2$ is documented in the referenced literature.

Components (circuit right) IC<sub>3</sub> LM566, SE/NE566 General-purpose voltage-controlled oscillator. C<sub>T</sub> 4.7nF C<sub>6</sub> 0.047 $\mu$ F R<sub>8</sub> 4.7k $\Omega$  R<sub>T</sub> 10k $\Omega$ Maximum sweep rate 1MHz R<sub>T</sub> and C<sub>T</sub> are the frequency range determining components. For a fixed value of  $C_T 10:1$ variation in frequency is possible via a variable input at  $V_{control}$  which should be within the range 3 to 5.5V for  $V_{cc} = \pm 6V$ .

The above values provide for a maximum free-running frequency of about 10kHz for  $Tr_1$  off. For  $V_s = -3V$ ,  $Tr_1$  is saturated, hence increasing timing capacitor 10 times, free-running frequency is then approximately 1kHz.

Control voltage measured between pins 8 and 5 should be in the range 0 to  $0.25 V_{ce.}$ (It is this voltage divided by R<sub>T</sub> which defines capacitor charging current.) Frequency is

$$\frac{2(V_{\rm ee}-V_{\rm control})}{R_{\rm T}C_{\rm T}V_{\rm ec}}$$

#### Further reading

Klein, E. Medium-scale integration for instrumentation and control, *Semiconductors* (Motorola) vol. 2 no. 1 1971, p. 20.

Signetics: SE/NE566 function generator data sheet.

Cross references Set 17, card 3 Set 8, card 9

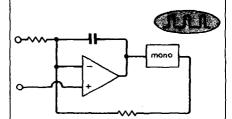

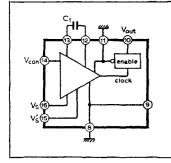

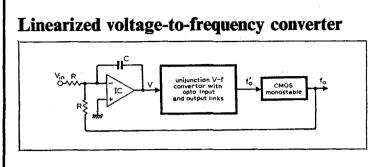

Components R 100k $\Omega$ , C 0.22 $\mu$ F IC 741 Unijunction V-f'\_o-see over, centre. Monostable-see over, right V<sub>in</sub> 0 $\rightarrow$ -10V

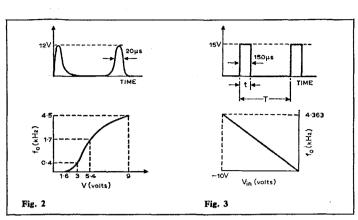

#### Performance

Graphs of  $f'_0$  and  $f_0$  are shown in Figs. 2 and 3. Graph of V against  $f_0$ , corresponding to open-loop v-f conversion, is shown in Fig. 2. with V<sub>1n</sub> against  $f_0$  shown in Fig. 3. Linearity achieved was better than 0.5%—clearly much better than the open-loop performance.

#### System description

If the loop gain of a closed-loop system is high then the effect of non-linearities in the forward path is much reduced. In this case we have a highly non-linear V to  $f_0$  converter and an integrator/error detector is then included to provide the feedback. In d.c. terms, the integrator can be regarded as having infinite gain since for finite input voltage the output voltage after infinite time is infinite, ignoring the effect of saturation. Alternatively:  $\Delta V =$

$$1/RC \int_{0}^{T} V_{in} dt + 1/RC \int_{0}^{t} 15 dt$$

The steady-state condition of constant fo can only occur when V is constant and this occurs when  $\Delta V$  is zero i.e. when the integral of the input signal and the integral of the feedback signal exactly cancel. Hence exact correspondence between Vin and fo can be expected if the integrator and feedback signal are "perfect". Immediate improvement in the system would be effected if an i.c. with much lower input current requirements were used e.g. 308. Further improvement would be obtained by the use of a low-loss capacitor. The c.m.o.s. monostable was included to give an output pulse train of well defined height and width and overall shape. A better f'o to fo converter could have been used. It should be noted that the overall characteristics are now dictated by the feedback signal and the integrator so that

forward path changes, causing changes in  $f_0$ , will be completely cancelled, apart from transient effects. Changes in the shape of  $f_0$ , e.g. impulse height and width, will however have an effect on  $f_0$ , although not linearity.

#### System modification

Effectively, the combination of the monostable and integrator is an  $f'_0$  to v converter. The system could therefore be changed to that shown in Fig. 4. K would be chosen to be sufficiently high such that the linearity of the overall system is equivalent to that of the f to v converter. This is only satisfactory if the shape of the  $f'_0$  pulses is satisfactory.

#### **Element description**

The circuit of Fig. 5 shows the detail of the unijunction v to f converter (card 1) used. The opto-elements are included to show that their inherent isolating properties can be used not least to produce a very non-linear v to  $f'_0$  characteristic. This is because  $D_1$  requires approximately 1.6V to conduct and there is non-linearity in the

device current transfer ratio. Resistor  $R_2$  is

included to protect the transistor and  $R_4$  is large to produce a sufficiently large pulse to trigger the monostable. Resistor  $R_1$  may be reduced to allow much lower input voltages to be used. The limit is set by the opto-diode input current. Any opto-isolator may be used e.g. TIL112.

#### Components

$\begin{array}{l} R_1 \ 2.2 k \Omega, \ R_2 \ 1 k \Omega, \ R_3 \ 100 \Omega \\ R_4 \ 10 k \Omega \\ Opto-isolators \ 4350 \\ (Hewlett-Packard) \\ U.j.t. \ 2N2646 \ \ V_B \ 15V \\ C \ 0.01 \mu F \end{array}$

Circuit of Fig. 6 is the c.m.o.s. monostable used. It is identical in format to that described in set 18, card 8 but includes an extra diode to allow the capacitor to discharge closer to zero volts to improve linearity.

Components R  $100k\Omega$  C 2.2nF

**IC CD4013E**

D 1N914

Fig. 4

$\downarrow$

$\downarrow$

<

## Set 21: V to f converters-8

### Linear voltage-to-frequency converters

)

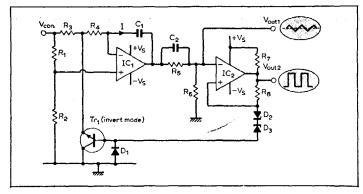

#### **Circuit description**

The circuit comprises an integrator whose output ramps toward positive and negative target values defined by diodes  $D_2$  and  $D_3$  i.e. the potential at the non-inverting input of comparator IC<sub>2</sub> is  $V_{D_2}+V_{D_3}+V_{BC}$  (or  $V_{D_1}$ ) about  $\pm 9V$ . When the transistor is off ( $V_{o_2}$  negative), capacitor current is

$$I = \frac{V_{\text{control}} \left( 1 - \frac{R_2}{R_1 + R_2} \right)}{R_3 + R_4} \qquad (1)$$

When  $Tr_1$  conducts, I is

$$\mathbf{I} = -V_{\text{control}} \left( \frac{R_2}{R_1 + R_2} \right) / R_4 \quad (2)$$

For equal slopes at the triangular output,  $V_{01}$ , the current magnitudes are equal, provided

$$\frac{R_1}{R_2} = 1 + \frac{R_3}{R_4}$$

If  $V_{02}$  is positive,  $Tr_1$  is on, and integrator output rises towards +9V at which level the comparator IC<sub>2</sub> switches over to make V<sub>02</sub> negative, bringing  $Tr_2$  out of conduction.  $C_1$ charges according to the first equation, and integrator output ramps towards -9V, when comparator again changes state. Components C2, R5, R6 form a phase-advance network to compensate for the switching delays of  $IC_2$  and  $Tr_1$  at the higher frequencies. The invert mode of Tr<sub>1</sub> provides a very low collector-emitter drop (few millivolts), i.e. the effect on the second equation is neglected. Linearity is better than 0.5% over the range of control

voltage, 0.1V to 8V, based on deviation from 6V value.

#### Component changes

This slew rate is typically  $10V/\mu$ s. If 741 used, slew rate  $(0.5V/\mu$ s) restricts higher frequency to which linearity is maintained (see graph).

Range of  $C_1$ : Typically 47 to 200pF. Frequency variation shown on graphs. Frequency is power supply dependent, hence need for good stability of supply.

Vary mark/space ratio of output at  $V_{02}$  by  $R_2/R_1$  ratio change; this also modifies frequency. Range of  $R_2$ ,  $R_1$  22 to  $68k\Omega$ Range of mark/space 1:1 to 1:3.

#### **Circuit modifications**

• A variable output voltage is obtainable via the circuit shown in Fig. 1. Comparator hysteresis can be changed by varying the fraction fed back via a potentiometer  $RV_1$ . This will control the output

amplitude. The triangular output is shaped by the circuit of Fig. 2. Potentiometer  $RV_2$ is adjusted for a minimum even-harmonic content, to provide an approximate cisoidal wave form at  $V_{out}$ .

• The field-effect transistors of Fig. 3 provide a similar switching action to  $Tr_1$  in first circuit to provide the integrator capacitor current charging paths. IC<sub>3</sub> as an integrator employs a speed-up network of 150pF in series with 10M $\Omega$ resistor.

Transistors  $Tr_2$  and  $Tr_3$ controlled by square-wave output from the Schmitt circuit of IC<sub>4</sub>. When  $Tr_2$  is on,  $Tr_3$  is off and C<sub>3</sub> charges via  $Tr_2$  and  $10k\Omega$ resistor. With  $Tr_2$  off, and  $Tr_3$ on, current reverses through the capacitor with magnitude defined by  $V_{control}/2R_9$ . RV<sub>3</sub> should be adjusted to provide a symmetrical square-wave output when V<sub>control</sub> is 5mV. Input control voltage range: 5mV up to 5V.

Frequency range 10Hz to 10kHz. Further reading

Wright, M.J. Linear voltage to frequency converter, *Electronic Engineering*, July 1973. Linearize your v-f converter, *Electronic Design*, Nov. 1973. Applied Ideas, *Electronic Engineering*, Jan. 1975, p. 17. Linear Integrated Circuits, National Semiconductor, 1972, p. 255.

### Cross references

Set 3, cards 1, 5, 11 Set 17, card 3

## Set 21: V to f converters—9

## wireless world circard

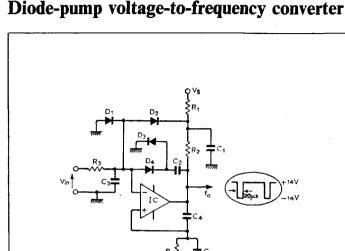

#### **Circuit description**

Elements R<sub>1</sub>, R<sub>2</sub>, D<sub>1</sub>, D<sub>2</sub> and  $C_1$  are not basic to the action of this circuit and will be ignored initially. Suppose the i.c. output is sitting at +14V. Then C<sub>2</sub> will have been charged to this level via D<sub>3</sub>. However as C<sub>3</sub> charges via R<sub>3</sub> under the influence of Vin, the negative terminal of the i.c. eventually reaches 0V and the amplifier output swings negative. The network comprising C<sub>4</sub>, R<sub>4</sub> and C<sub>5</sub> provides sufficient positive feedback to make this swing very rapid-hence the use of a high speed op-amp. Capacitor  $C_2$  then deposits its charge via  $D_4$  into  $C_3$  in a diode pump fashion thereby lowering the voltage across C<sub>3</sub>. However the positive feedback network consists of elements with a short time constant and the voltage on the positive terminal quickly becomes less negative than the negative terminal voltage and so the amplifier voltage swings back to +14V. In the -14V period the circuit is acting rather like a monostable, the delay being fixed by the  $C_4$ ,  $R_4$ ,  $C_5$  network and by the  $R_3$ ,  $C_3$  network. Because there is again positive feedback the rising edge will be

equally sharp but the period will be difficult to define accurately, partly because of the complexity of the CR networks and partly because two voltages both going in the same direction (positive) are being compared.

This, however, is not serious since the pulse width does not affect the amount of charge on  $C_2$ , and it is this charge which is being balanced by the current in the input network. The maximum frequency we obtained was close to the limit of the op-amp but the markspace ratio could have been made even lower if required by reducing  $C_3$ ,  $R_3$  or lengthening the time constant of  $C_4$ ,  $R_4$ ,  $C_5$ . The network comprising  $R_1$ ,  $R_2$ ,  $C_1$  and  $D_2$  prevents the device from locking into a saturated condition by too large an input voltage (positive). Diode  $D_1$  prevents the negative input terminal being overdriven by a negative input voltage.

#### **Circuit modifications**

A high-speed comparator would be preferable to an op-amp which was used in our experiments.

• The pulse width does not theoretically affect the result

Components Supplies  $\pm 15V$ IC 748C  $R_1 12k\Omega, R_2 3.9k\Omega$  $\begin{array}{rrrr} R_{3} & 10k\Omega, R_{4} & 4.7k\Omega \\ C_{1} & 4.7\mu F, C_{2} & 1nF \end{array}$  $C_3 33\mu F, C_4 56pF$ C<sub>5</sub> 500pF D<sub>1</sub> to D<sub>4</sub> 1N914

#### Performance

$V_{in}: 0 \text{ to } +4.00V$ Output pulse train: pulse width about 20 $\mu$ s swinging from +14V to -14V with a maximum frequency of around 14kHz, corresponding to a mark-space ratio approaching 3:1. Linearity better than 0.3% over two decades.

but the pulse height does. A c.m.o.s. buffer amplifier could be included to give a well defined output pulse heightsee reference 2.

An alternative approach to the pulse height problem is to use internal clamping of the output level-see references 3.

#### References

- 1 Pease, R. Ultra-linear voltage-to-frequency converter, Electronic Engineering, March 1971.

- 2 Set 3 (waveform generators) card 11.

- 3 Set 3, card 1. Set 2, card 1.

## Set 21: V to f converters-10

### Differential input voltage-to-frequency converter

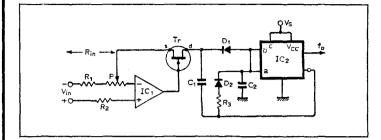

#### **Circuit description**

The above circuit is of a form published by Woodward but with what appear to us as corrections, although we have to admit to not achieving the performance claimed in his article, viz linearity better than 0.05% from 10Hz to 10kHz. The results we achieved are shown roughly in Fig. 2, measured linearity being 0.15% over the two decades, 100Hz to 10kHz.

Pin c of IC<sub>2</sub> is the R (reset) terminal and its action is not necessary in a brief explanation. Pins a and b are the trigger and threshold terminals of the i.c. When the C<sub>2</sub> capacitor voltage goes below the trigger potential,  $V_s/3$ , the output swings high, and when the voltage exceeds the threshold voltage,  $2V_s/3$ , the output swings low—see waveforms of Fig. 3.

The basic principle is that of charge dispensing in which a current proportional to a voltage is balanced by the periodic charging of a capacitor to a precise voltage. In this case, the current through the f.e.t. is fixed by the input voltage at  $V_{1n}/R_{1n}$ . This current flows for time T as a result of the charging of C<sub>2</sub> from  $V_B/3$ to  $2V_S/3$ . Thus

$$\frac{V_{1n}}{R_{1n}} T = C_2 \frac{V_s}{3}$$

and  $f_0 = \frac{3V_{1n}}{R_{1n}C_2V_s}$

This expression is valid so long as T is large compared with the pulse width.

When the output goes high  $C_2$ charges via  $R_3$  and  $D_2$  from  $V_s/3$  toward  $V_s$ . During this period  $D_1$  is reverse biased and at the same time  $C_1$  is providing some current to the f.e.t. When  $C_2$  reaches  $2V_s/3$  the output goes low,  $D_1$  conducts,  $C_1$  and  $C_2$  share the charge on  $C_2$  and the parallel combination discharges linearly through the f.e.t. Diode  $D_2$  is reverse biased in this period. The sharing of the charge between  $C_1$  and  $C_2$  causes the sharp drop in the  $C_2$  voltage when  $2V_s/3$  is reached. The

discharge is linear because the f.e.t. current is fixed by the input voltage. The results obtained required adjusting of the op-amp offset voltage to zero. Common-mode rejection ratio is independent of input resistor match and is dictated by the op-amp used. However, common-mode voltage should not exceed  $\pm 2V$ .

#### Component changes

The charging time depends on  $C_2R_3$  and should be short without R<sub>3</sub> being so low as to overload IC<sub>2</sub>. This is not difficult to achieve since it is the open collector terminal which is used to charge  $C_2$ . Capacitor C<sub>1</sub> serves to cut off  $D_1$  whilst  $C_2$  is charging, so its value is not critical. Generally speaking though it should be less than C<sub>2</sub> to minimize the drop in  $C_2$  voltage when  $D_1$ starts conducting again, thereby keeping the slope of the downwards ramp as large as possible and clearly defining the time at which the voltage drops below  $V_{\rm s}/3$ . Actually,  $C_1$ and  $D_1$  can be removed altogether without complete failure of the circuit, although linearity and output pulse shape

are affected.

Diodes  $D_1$  and  $D_2$  can be any general-purpose diodes unless very high speed operation is required.

Reducing the values of the op-amp input resistors and choosing a suitable op-amp will allow values of  $V_{1n}$  in the millivolt region to be used to give the same output frequencies.

#### **Circuit modifications**

Any circuit which will successfully draw constant current from the junction of  $C_1$  and  $D_1$  will produce the same result and such a circuit is shown in Fig. 4. The photodiode current is proportional to light intensity so an intensity-to-frequency converter would be produced by this arrangement. The differential input aspect is lost, however, unless one puts a second photodiode, connected the opposite way round, across the one shown.

#### Reference

Woodward, W. S. Simple 10kHz voltage-to-frequency converter features differential inputs, *EDN*, Oct. 20, 1974, p. 86.

## Set 21: Up-date

# wireless world circard

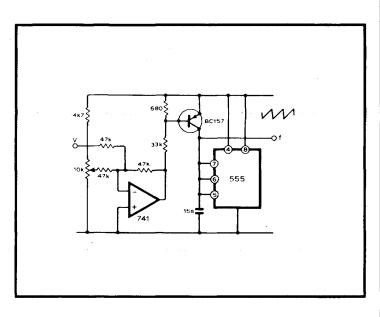

Most of the circuits described have been aimed at linearizing the v-f conversion, as in measurement of modulation systems. Sometimes it is required to have a converter in which the v-f conversion is highly non-linear with the frequency following, for example, an exponential or logarithmic function or sharply changing at some threshold voltage. The circuit indicates a simple way of changing the frequency over a claimed five-decade range. A linear voltage variation is

A linear voltage variation is applied to the base-emitter junction of a transistor to charge a capacitor. The capacitor forms part of an

astable circuit based on the well-known 555 timer, with a sawtooth waveform generated across the capacitor swinging between V/3 and  $2V_3/3$ . The reference indicates additional components to set the frequency to zero for V=0 and for buffering the output waveform. More generally a linear v-f converter is combined with a non-linear amplifier whose non-linearity is predictable, rather than introducing non-linearity into the conversion process itself.

#### Reference

Brice, J. L. Voltage-controlled ramp generator, *Wireless World*, June 1976, p. 72.

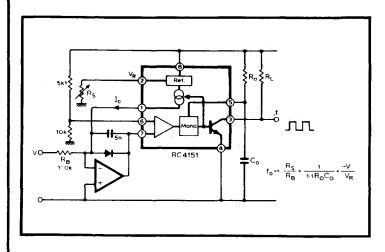

The new generation of linear integrated circuits includes complete v-f modules that will compete with the hybrid and modular versions for many applications. One such monolithic device RC4151 is in line of succession to the 555. It includes a monostable comparator and output stage, but adds a switched current generator. It can be used without additional active devices, but for improved linearity is combined with an op-amp to form a chargebalancing system. The input

current to the summing junction is balanced by the constant-height constant-width current pulses returned by the monostable ensuring a linear relationship. A zero-offset voltage fed to the non-inverting terminal ensures that  $f\rightarrow 0$  as  $V\rightarrow 0$ . Resistor R<sub>s</sub> sets the scale-factor for 0–10kHz corresponding to  $0\rightarrow 10V$ .

#### Reference

Cate, T. IC V-f converters readily handle other functions such as f-V, A-D, *EDN*, Jan. 5, 1977, pp. 82–6.

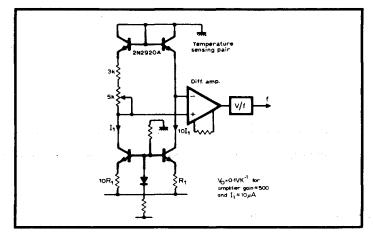

The same article shows amongst other applications a linear thermometer, with some similarity to the band-gap reference circuits of set 23. The temperature-sensing pair are forced to operate at a 10:1 ratio of collector currents giving a  $\Delta V_{BE}$  that is a controlled linear function of temperature. The precise scaling factor is set by the  $5k\Omega$  resistor. The amplifier requires to be a true differential input amplifier of controlled gain. Again the overall function is split into two parts: a linear v-f converter, and a separate circuit to provide the linear or non-linear response. It would be proper to describe this as a T-V-f converter.