## High-speed generator pulses ECL loads

by Andrew M. Hudor Jr.

Department of Physics, University of Arizona, Tucson

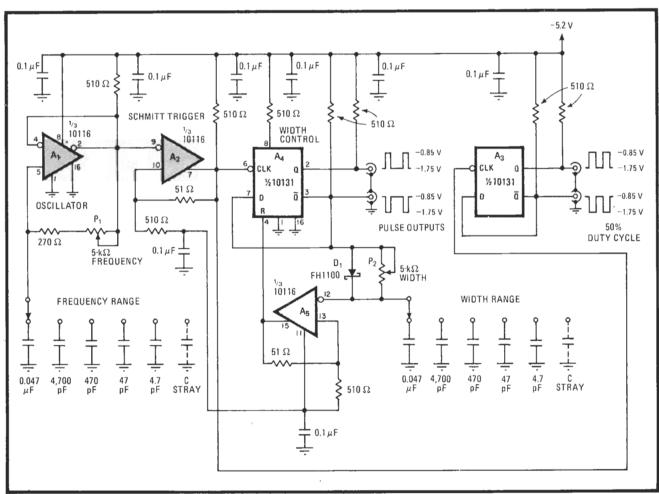

Serving the needs of designers and technicians who work with high-speed digital circuits, this inexpensive two-chip pulse generator is invaluable in trouble-shooting emitter-coupled logic. Besides generating signals having frequency and duty cycles that are adjustable to its complementary outputs, the versatile generator also provides two ports at which pulses with a constant 50% duty cycle are available.

One section of a 10116 ECL line receiver,  $A_1$ , is used as an RC oscillator whose period is determined by the potentiometer  $P_1$  and the capacitor selected by the frequency-range switch. With the values shown, the oscillator frequency can be varied from a few hundred hertz to more than 50 megahertz. The output of the oscillator is then buffered and squared up by a Schmitt trigger,  $A_2$ , which is the second section of the line receiver.

$A_2$ 's output toggles both sections of a 10131 dual-D flip-flop,  $A_3$  and  $A_4$ .  $A_3$  provides for a 50% duty cycle output, while  $A_4$  and the remaining section of the receiver,  $A_5$ , form an adjustable one-shot multivibrator. Here,  $A_5$  serves as a second Schmitt trigger.

The Q output of  $A_4$  is fed to the input of the Schmitt trigger through an RC integrator formed by  $P_2$  and the capacitor selected by the width-range switch. When Q toggles low, the input to the  $A_5$  trigger slowly rises as the capacitor charges. When the trigger level is reached, the Schmitt trigger's output goes high, resetting  $A_3$  and  $A_4$ , and the process is repeated.

The time it takes for the integrator to reach the trigger level defines the pulse width. With the values shown, widths from 15 nanoseconds to 10 milliseconds can be selected. Upon resetting of the flip flops, Schottky diode  $D_1$  allows the capacitor to discharge rapidly. The width control allows adjustment of the duty cycle from nearly zero to 50%. For applications where a duty cycle greater than 50% is required, the complementary output should be used.

If desired, a buffer can be easily added at  $A_3$  and/or  $A_4$  in order to drive 50-ohm lines directly.

## References

William A. Palm, "ECL IC oscillates from 10 to 50 MHz," Electronics, Circuit Designer's Casebook 14D p. 109

**Speedy.** Line receiver and dual flip-flop generate high-frequency pulse trains for emitter-coupled logic. Signals to 50 MHz having widths that are adjustable from 15 ns to 10 ms appear at generator's complementary outputs. Circuit also provides output at duty cycle of 50%.