## Series 8: Astable circuits

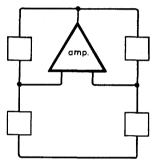

Almost every possible kind of astable circuit is covered in series 8, probably as a result of the interesting unified approach discussed in the article. The oscillator is depicted as a bridge network (Fig. 5) with one bridge arm providing positive feedback, the other negative feedback, the amplifier input differentially connected between the two centre points of the arms, and the output feeding the bridge to sustain oscillation. This approach allows one to see how the six configurations of Figs. 6 and 7 are really variants of the basic bridge circuit. Practical circuits based on Figs. 6 and 8 are given on card 5.

Five cards show other kinds of astable circuit constructed from logic elements, one being a hybrid in that discrete components are used to provide a constant charging current to cross-coupled monostables (card 11). A single-capacitor astable using t.t.l. NOR or NAND gates as inverters is useful up to frequencies of a few megahertz (card 7). Two other single-capacitor circuits, the c.m.o.s. inverter circuits of card 1 and the current-switching emitter-coupled circuit of card 9, both allow voltage control of frequency.

Whilst some logic astable circuits have poor frequency-supply voltage stability, most discrete-component circuits have a stability of the order of 1% per volt, and three have stabilities of less (0.46% card 10, 0.3% card 3, 0.2% card 5).

Complementary m.o.s. astable circuit 1

RTL astable circuit 2

Complementary astable circuit 3

TTL Schmitt astable circuit 4

Operational amplifier astable circuit 5

Astable blocking oscillator 6

TTL dual inverter astable circuit 7

Coupled logic gates astable circuit 8

Emitter-coupled astable circuit 9

Discrete-component Schmitt astable 10

Dual-monostable astable circuit 11

Astable circuit with f.e.t. 12

# **Astable circuits**

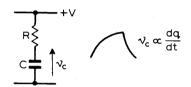

Many circuits generating periodic rectangular waveforms depend on changing the charge on a capacitor. This rate of change of charge is frequently determined by an *RC* circuit, which inherently produces exponential waveforms when connected to a voltage source (Fig. 1). Such waveforms may be used to control the switching on and /or off instants of an active device.

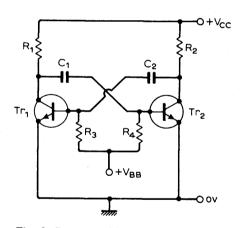

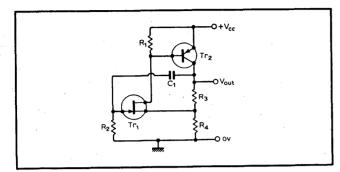

An astable multivibrator using discrete

Fig. 1. Series RC produces an exponential waveform across the capacitor.

Fig. 2. Basic astable multivibrator. Variation of  $V_{BB}$  changes the period.

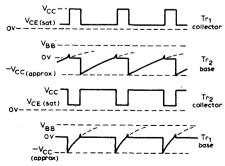

Fig. 3. Waveforms encountered in the circuit of Fig. 2, where  $C_1R_4$  is longer than  $C_2R_3$ .

components is a commonly occurring example of a circuit employing this principle (Fig. 2). This uses two transistors, cross-coupled via capacitors  $C_1$  and  $C_2$ . Normally this circuit has no stable states (they may be called quasi-stable states), but switches alternately from the one state of  $Tr_1$  saturated,  $Tr_2$  off, to the state of  $Tr_2$  saturated,  $Tr_1$  off. For a given value of  $V_{CC}$ , the rate of switching depends on the time constant  $C_1R_4$ ,  $C_2R_3$ , and on the potential to which the base resistors  $R_3$  and  $R_4$  are returned. The more conventional configuration will return  $R_3$  and  $R_4$  to the  $V_{CC}$  rail to give a period independent of rail voltage.

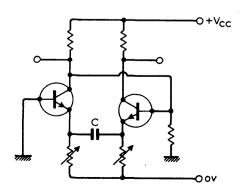

Fig. 3 shows that the output rectangular waves available at the collectors are in anti-phase, and their mark-to-space ratio may be varied by adjusting the  $C_1R_4$  and  $C_2R_3$  time constants. Some astables are attractive due to the small number of components required, but they might be considered to have certain disadvantages. The use of a single CR network gives an output waveform having a non-unity mark-to-space ratio which may be difficult to closely control. Also a second anti-phase output is not available. A circuit using a single capacitor that overcomes these objections to an extent is the emittercoupled astable of Fig. 4. In this arrangement, two emitter resistors are used to allow independent adjustment of the mark and space times of the two output waveforms.

Another group of astable circuits apparently different from each other fit into the form of the general bridge network shown in Fig. 5. The amplifier block is provided with two external

Fig. 4. A single-capacitor astable multivibrator providing mark-to-space ratio adjustment and antiphase outputs. Circuits using one capacitor are normally less flexible.

networks. One network, providing negative feedback, ensures that the d.c. conditions in the amplifier are such that it sits near the middle of its operating region where the gain is high. The other network, which provides positive feedback, forces the amplifier to switch between two distinct states. This amplifier block may comprise either a single differential-input amplifier or two single-ended types. In

Fig. 5. Basic diagram of the group of oscillators using both positive and negative feedback. The circuit is seen to be a bridge network with a sustaining amplifier.

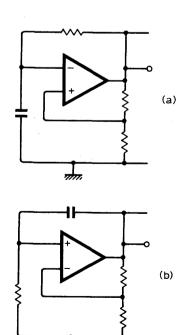

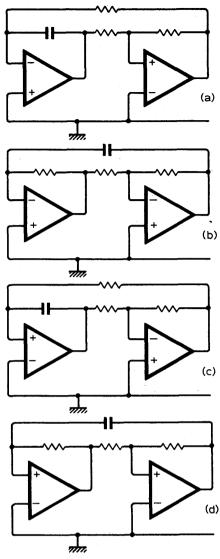

Fig. 6. Two possible combinations of feedback types using a single differential amplifier.

Fig. 7. Four combinations of RC feedback and amplifiers used in the single-ended mode.

conjunction with the different combinations of feedback components, this leads to the apparently different configurations shown in Figs. 6 and 7. These circuits have been redrawn in Figs. 8 and 9 respectively to show their relationship to the bridge arrangement. Circuit 7(d) does not operate as an astable because it will permanently latch into one state, since positive feedback is applied across each single-ended amplifier.

The output waveform from an astable multivibrator is not necessarily rectangular. A self-retriggering action can be obtained by using an electronic switch to discharge a capacitor when its potential exceeds a preset d.c. bias which holds the switch open.

To provide circuits compatible with logic levels, many astables operate in their saturated mode to give well-defined voltage limits. This is achieved at the expense of the switching rate, but may be avoided by the use of current mode switching techniques.

Other applications demand long periods with accurately defined transition times, and this requires high stability passive components. Reasonably small value but stable capacitors can be used in conjunction with field-effect transistors to provide the long time constants necessary. It should be remembered that if an astable multivibrator has good frequency stability, it may prove difficult to synchronize it from an external source.

The reader will have noted that inductive timing elements are conspicuous by their absence. The reason behind this is that, in comparison with capacitors, inductors tend to be more costly and physically larger. One type of inductively coupled circuit worthy of mention is the astable blocking oscillator, which is capable of producing output pulses having a very small mark-to-space ratio.

Fig. 8. Circuits of Fig. 6 redrawn to show that they conform to the general bridge circuit of Fig. 5.

Fig. 9. The four twin-amplifier circuits are also examples of the general bridge circuit.

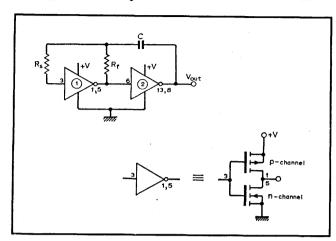

## Complementary m.o.s. astable circuit

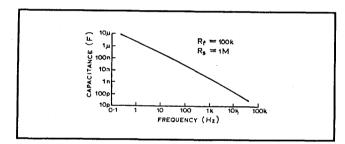

#### Typical performance

IC: CD 4007AE Supply: +10V

$R_f$ :  $100k\Omega$ ;  $R_s$ :  $1M\Omega$ C: 10nF; f: 424Hz

Load resistance: ∞ Supply current: 280µA Square wave available at  $V_{\mathrm{out}}$

Output excursion: 0.03

to 9.9V

Mark-to-space ratio: 0.93

Rise time: 200ns

Circuit description

This integrated circuit package comprises three n-channel and three p-channel enhancement-type m.o.s. transistors which may be arranged to form three separate inverters. The above circuit uses two inverters, the first inverter being biased to its amplifying region by resistor R<sub>s</sub>, and in this region the loop gain is sufficient to initiate multivibrator action. When the output of inverter 2 goes high, the input is low and the input of inverter 1 is high. As the capacitor charges up via resistor R<sub>f</sub>, the voltage across R<sub>f</sub>, and hence the voltage applied to the gate of the first inverter, falls. When this voltage at the junction of C and R<sub>f</sub> passes through the threshold value of the first inverter, its output becomes high, switching the output of inverter 2 to a low state. Capacitor C will now charge in the opposite direction via resistor R<sub>f</sub> and when the voltage at the junction of C, R<sub>f</sub> and R<sub>s</sub> rises towards and crosses over the threshold level, the output of inverter 1 again

goes low, the output of inverter 2 is switched to the high state and the cycle repeats.

The waveform achieved is fairly symmetrical because the threshold point is close to half the supply voltage value. However, this means that the mark-to-space ratio is not unity, but this may be arranged by circuit modification. Resistor  $R_{\rm s}$  also improves the frequency stability of the circuit with respect to supply voltage changes, and should be at least twice the value of  $R_{\rm r}$ .

#### Component changes

- With supply of +10V,  $R_f$  of  $100k\Omega$ , and C of 2.2nF, mark-to-space ratio varies from 0.76 to 0.92:1 for  $R_s$  from 0 to  $1M\Omega$ .

- Components as listed in typical performance data but with finite load resistance  $R_L$ . Output pulse level falls, typically by 10% when  $R_L = 2.2k\Omega$ .

- Minimum value  $R_t$  for acceptable waveform:  $6.8k\Omega$ . Waveform improved by using third inverter as buffer. With  $R_s$  of zero,  $R_t$ :  $6.8k\Omega$ , C: 39pF, f is 610kHz (supply 10V). With  $R_s$  of zero,  $R_t$ :  $10k\Omega$ , C: 10pF, f is 650kHz (supply 10V). If supply is increased to 15V, f is 900kHz.

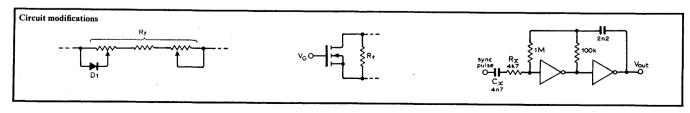

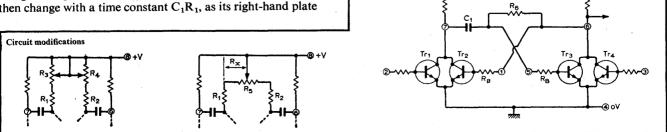

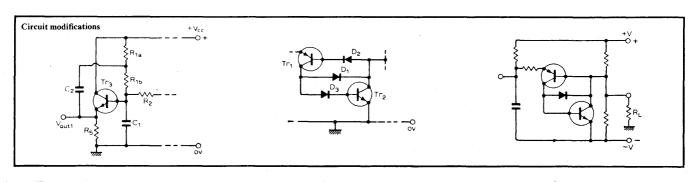

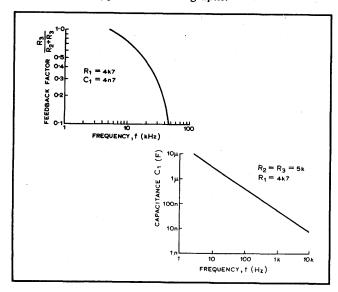

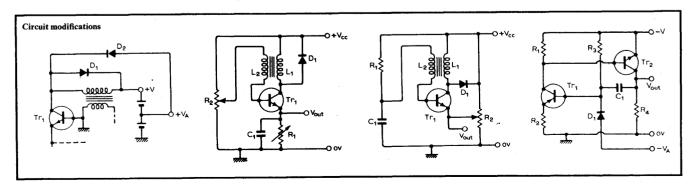

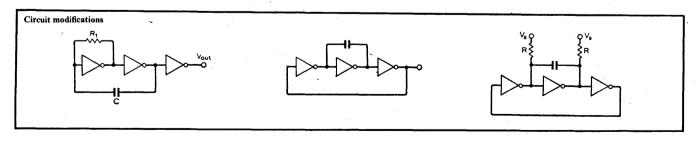

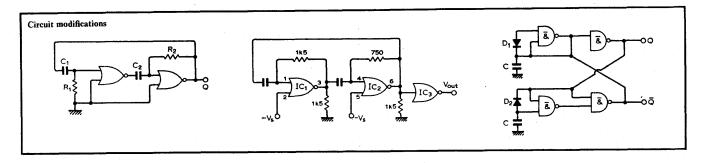

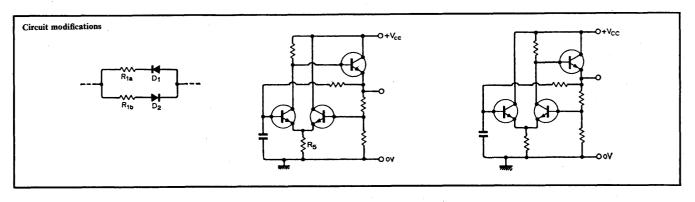

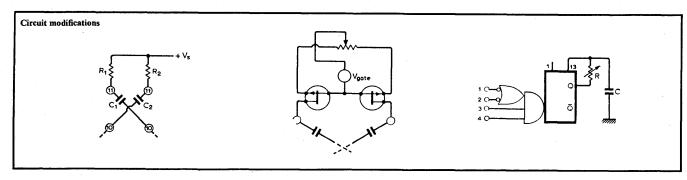

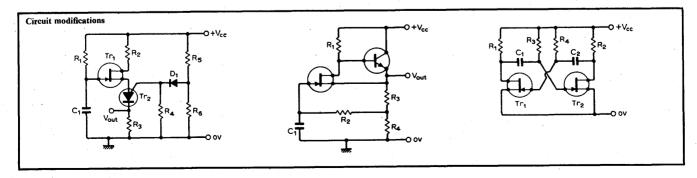

#### Circuit modifications

- Output waveform duty cycle may be controlled by replacing  $R_f$  with the arrangement shown left. The adjustment of this diode shunt causes the frequency of the circuit to vary, and another variable resistance can be added to compensate the change. If a 50% duty cycle is not obtained, reverse the diode  $D_1$ .

- A voltage-controlled oscillator is obtained when  $R_f$  is replaced by the arrangement shown centre. With  $V_G$  in the range 0 to +10V using an n-channel device, frequency is variable from approximately 20 to 30kHz for a supply of +10V and  $R_f$ :  $10k\Omega$ ,  $R_s$ :  $100k\Omega$  and C: 2.2nF.

- A simple way of synchronizing the circuit with an external source is shown right. Components  $R_x$ ,  $C_x$  change the natural multivibrator frequency. With components shown, free-run frequency is 2220Hz increasing to 3985Hz when synchronizing components are connected but with zero source signal. Locking frequency range approximately 22/1 but can depend on level of synchronizing pulse. Suitable pulse level 0.5 to 1.0V.

#### Further reading

RCA COS/MOS Digital Integrated Circuits, SSD-203A, 1973, pp. 353-9.

Low-speed astable uses c.m.o.s., *Electronic Components*, 6 April, 1973, p. 294.

Clock oscillator for telemetry systems uses c.m.o.s. chip to minimize power drain, *Electronic Design*, vol. 20, 1972, p. 84.

#### Cross references

Series 8, card 3. Series 3, card 11

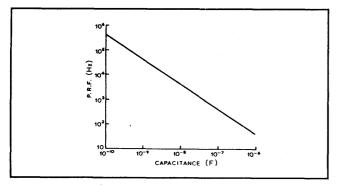

## Series 8: Astable circuits 2

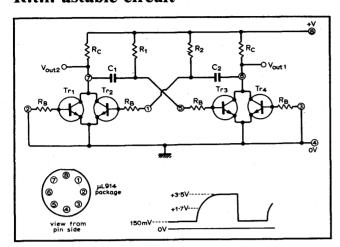

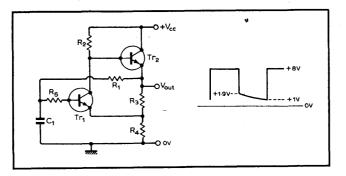

## R.t.l. astable circuit

#### **Typical performance**

$\mu$ L914 package contains

—four 2N708-type

—R<sub>B</sub> of 450Ω; R<sub>C</sub> of

640Ω

External components:

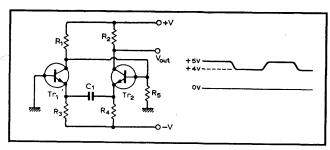

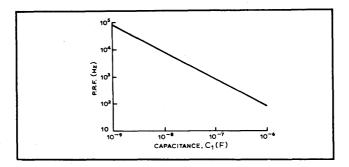

$R_1$ ,  $R_2$ :  $10k\Omega \pm 5\%$   $C_1$ ,  $C_2$ :  $100nF \pm 10\%$ Supply: 3.6V, 6.5mAP.r.f. 699Hz (see graph) Mark to space ratio: 1.06 $V_{out_1}$  waveform as shown

Circuit description

The  $\mu$ L914 contains two identical resistor-transistor logic (r.t.l.) gates. In the above arrangement one input to each gate is not used, pins 2 and 3 being grounded to effectively remove  $Tr_1$  and  $Tr_4$  from the circuit. Transistors  $Tr_2$  and  $Tr_3$  are interconnected to form a cross-coupled astable which may be considered to be a two-stage amplifier with its output fed back to its input and having very high loop gain. The circuit is inherently self-starting; any dissimilarity however small between the two halves of the circuit causes one transistor to be off and the other saturated.

Consider  $Tr_2$  on and  $Tr_3$  off. In this state the circuit levels are:  $Tr_2$  collector:  $V_{CE(sat)}$ ,  $Tr_2$  base:  $V_{BE(on)}$ ,  $Tr_3$  collector: +V and  $Tr_3$  base: approx. -V due to the negative-going transition at  $Tr_2$  collector. When switched from off to on the charge on  $C_1$  cannot change instantaneously.  $C_1$ 's charge will then change with a time constant  $C_1R_1$ , as its right-hand plate

attempts to change to +V from -V. However, when this potential slightly exceeds 0V,  $Tr_3$ 's base-emitter junction becomes forward-biased and it rapidly turns on, its collector voltage falling to  $V_{CE(8at)}$ . The negative step passes to  $Tr_2$  base through  $C_2$  switching  $Tr_2$  off. The circuit is now in its other quasi-stable state. This action repeats continuously, producing antiphase square waves at  $Tr_2$  and  $Tr_3$  collectors. The off-times of  $Tr_3$  and  $Tr_2$  are given by  $t_1 = 0.6931C_1R_1$  and  $t_2 = 0.6931C_2R_2$  sec. The p.r.f. of the square waves is thus: f = 1/T, where  $T = t_1 + t_2$ . The mark-to-space ratio is adjustable by altering the ratio  $C_1/C_2$  and/or  $R_1/R_2$ .

Component changes

Useful range of supply +1 to +6V (exceeds rating, not guaranteed).

Frequency stability: +2% for 1V increase in supply, -3.5% for 1V decrease.

Useful range of  $C_1$  and  $C_2$ : 220pF to  $66\mu$ F (p.r.f.  $\approx 1.4$ Hz). Mark-to-space ratio: 6.8:1 ( $C_1:100$ nF,  $C_2:22\mu$ F) to 1:8.5 ( $C_1:100$ nF,  $C_2:220$ pF),  $V_{out(max)}:1.8$ V.

Useful range of  $R_1$  and  $R_2$ : 2.2k $\Omega$   $V_{\text{out (max)}}$ : 2.8V to 33k $\Omega$  ( $V_{\text{out}}$  distorted in "0V" region).

Complementary square wave is available at Vout2.

At either output  $V_{out(max)}$  falls by 10% when loaded with  $4.7k\Omega$ .

#### Circuit modifications

- As p.r.f. and mark-to-space ratio depend on the  $C_1R_1$  and  $C_2R_2$  time constants, a variable-frequency square wave is obtained by switching in different, but equal, values of capacitance and varying the p.r.f. continuously with  $R_1$  and  $R_2$  in the form of ganged potentiometers. See circuit left, where  $R_1$ ,  $R_2$  are  $2.2k\Omega$  and  $R_3$ ,  $R_4$  are  $22k\Omega$ . If only one resistor is variable, the mark-to-space ratio is variable but so also is the p.r.f.

- A modification allows the mark-to-space ratio to be made greater or less than unity by adjusting the position of the slider of  $R_5$  (middle circuit) without changing the p.r.f. since f = 1/T and  $T = t_1 + t_2$ . Hence, with  $C_1 = C_2 = C$  and  $R_1 = R_2 = R$  then  $T \propto C(R + R_x) + C[R + (R_5 R_x)] \propto C(2R + R_5)$  which is independent of  $R_x$ .

- Circuit on right shows modification to use only one capacitor. Useful ranges of  $C_1$  and  $R_6$  are  $100 \mathrm{pF}$  to  $100 \mu\mathrm{F}$  and 470 to 10k respectively. The circuit may be externally synchronized by positive pulses at  $Tr_1$  or  $Tr_4$  base and locks over a frequency range of at least 2:1. Minimum trigger pulse amplitude about  $500 \mathrm{mV}$ , minimum trigger pulse width about  $200 \mathrm{ns}$ .

#### **Further reading**

Fenwick, P. M., Pulse generator using r.t.l. integrated circuits, *Radio and Electronic Engineer*, 1969, pp. 374-6.

### **Cross references**

Series 8, cards 8, 12.

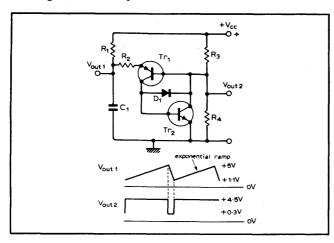

## Complementary astable circuit

#### Typical performance

Supply: +9V, 4.5mA Tr<sub>1</sub>: BC126; Tr<sub>2</sub> BC125 Diode: HP5082-2800 R<sub>1</sub>:  $27k\Omega$ ; R<sub>2</sub>:  $47\Omega$   $R_3$ ,  $R_4$ :  $1k\Omega$ ,  $C_1$ : 10nFP.r.f. 6.1kHzMark-to-space ratio: 49:1

Rise time of  $V_{out_2}$ : 1.2 $\mu$ s

#### Circuit description

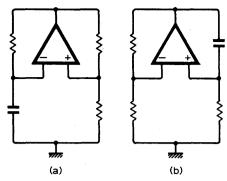

When the supply is connected,  $Tr_1$  base and  $Tr_2$  collector are at a potential determined by the ratio  $R_4/R_3$ , which could be in the form of a potentiometer to set the upper level of  $V_{\rm out_1}$  and  $V_{\rm out_2}$ . The p.d. across  $C_1$  is zero, so the base-emitter junction of  $Tr_1$  is reverse-biased and both transistors are cut off. Capacitor  $C_1$  begins to charge exponentially with time constant  $C_1R_1$  causing the p.d. across it to rise towards  $+V_{\rm cc}$ . When the capacitor voltage slightly exceeds the base potential of  $Tr_1$  the base-emitter junction begins to be forward-biased, significant conduction occurring when the capacitor voltage is approximately 0.5V more positive than  $Tr_1$  base.

Positive feedback, due to the interconnection of the bases and collectors of the complementary pair of transistors, ensures that this transition to the on-state is very rapid. Thus  $C_1$  discharges through  $Tr_1$  and  $Tr_2$  with  $R_2$  providing a discharge current-limiting action. Diode  $D_1$  prevents the transistors saturating and ensures that the circuit can re-cycle.

The capacitor does not completely discharge, but as the current in the transistors falls the loop gain around  $Tr_1$  and  $Tr_2$  reduces to a value that cannot maintain conduction, which ceases when  $Tr_1$ 's emitter voltage falls to about 1V. Both  $Tr_1$  and  $Tr_2$  rapidly switch off allowing  $C_1$  to recharge through  $R_1$  and  $V_{\text{out}_2}$  returns to its initial value determined by  $R_4/R_3$ . During the discharge of the capacitor, a narrow negativegoing pulse is obtained at the junction of  $R_3$  and  $R_4$  due to the conduction of  $Tr_3$ .

#### Component changes

Useful range of supply: +2 to +18V. Useful range of  $C_1$ : 100pF to  $1,000\mu$ F. Minimum load resistance at  $V_{out_2} \approx 220\Omega$ . Frequency stability: +0.3%/V increase in supply.  $Tr_1$ : ME0413, 2N3906, BCY71  $Tr_2$ : ME4103, 2N3904, BC107.

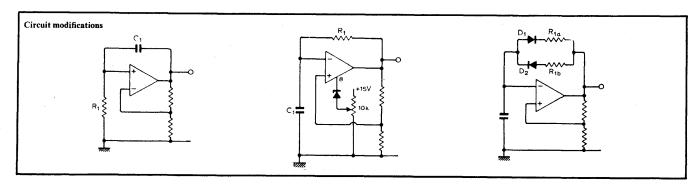

#### Circuit modifications

- Replacing  $R_3$  and  $R_4$  by a potentiometer across the supply changes the value of the capacitor voltage required to trigger the transistors into conduction and hence controls the period and amplitude of the output waveforms for given values of  $C_1$  and  $R_1$ .

- Narrow positive-going pulses in antiphase with those at  $V_{\rm out_2}$  can be obtained by including a small resistor in series with  $Tr_2$  emitter to the 0-V rail.

- The 'exponential' waveform,  $V_{out_1}$ , can be made into a more linear sweep by replacing  $R_1$  with a constant-current source. This sweep output can be extracted without significant loading by using an emitter follower. Linearity of the sweep output may be improved by splitting  $R_1$  into  $R_{1a}$  and  $R_{1b}$  and bootstrapping their junction with  $C_2$ , as shown left, where  $C_2$  should be of the order of  $100\mu F$ .

If  $D_1$  is required to be a silicon diode, additional silicon diodes  $D_2$  and  $D_3$  should be added as shown centre where all diodes could be of the 1N914-type.

• A dual-supply version of the circuit, which is otherwise identical with the single-supply form, is shown right where both outputs are taken w.r.t. ground. Both outputs can then be made to switch between more widely-varying levels and by adjusting the ratio  $R_4/R_3$  to set  ${\rm Tr}_1$  base to zero volt in the off-state, negative pulses may be obtained at  ${\rm V}_{\rm out_2}$ .

#### **Further reading**

Hemingway, T. K., Electronic Designer's Handbook, section 15, Business Publications, 1967.

Thomas, H. E., Handbook of Electronic Circuit Design Analysis, Reston Publishing Co. Inc., 1972, pp. 41-7.

Coers, G., Astable multivibrator needs only one capacitor, *Electronics*, vol. 46, 18 Jan. 1973, p. 171.

#### Cross references

Series 2, cards 5, 12. Series 6, card 8.

Series 3, card 6. Series 8, card 1.

## Series 8: Astable circuits 4

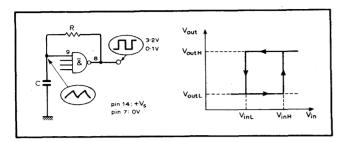

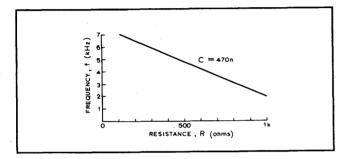

## T.t.l. Schmitt astable circuit

### Typical performance

IC: ½ SN7413 Supply: 5V

R: 330  $\pm 5\%$

C: 220nF  $\pm 5\%$ f: 10.8kHz

Mark-to-space ratio:

0.5:1

Circuit description

This circuit is internally constructed to behave as a Schmitt trigger, i.e. having two distinct output states, switching between them according to the voltage at the input, with a constant hysteresis between the input levels for switching. The relationship between the input and output states is shown above. The output remains low for  $V_{\rm inH} > V_{\rm in} > V_{\rm inL}$ . When the input level exceeds VinH, the circuit enters its active region, the action is regenerative, and the output becomes Vouth and would remain at this level until the input voltage was reduced to less than V<sub>inL</sub>.

In the circuit, a convenient starting point of the output high and the input low may be assumed. The capacitor will tend to charge up towards the output voltage, but when the capacitor voltage reaches the transition level for the i.c., the output falls to near zero voltage. The capacitor then discharges through R until its potential reaches that at which the reverse of the output states occurs, where the output again goes high.

Component changes

Useful range of R: 220 to  $1000\Omega$ . Astable will not function for  $R \geqslant 1.5k\Omega$ .

Useful range of C: 2.2nF to  $22\mu$ F.

Useful range of supply: 4.5 to 5.5V. Operation outside this rated range is possible, but performance not guaranteed. Typically with R: 680Ω and C: 470nF, frequency range is 1.9 to 2.4kHz for supply ranging from 3.5 to 7V.

For supply of 4.5 to 5.5V, frequency stability is approximately

Circuit will supply loads from infinity down to  $1k\Omega$ , with a reduction of frequency of less than 2.5%.

### Circuit modifications

- All four inputs of the nand gate may be paralleled or the unusued ones may be taken to  $+V_s$ .

- One or more of the nand-gate inputs may be grounded to gate the trigger off. This holds the output permanently in the high or logic 1 state (circuit left).

- Two such circuits operating at different frequencies may be locked by capacitive coupling between junctions of C, R elements. The coupling capacitor might be typically C<sub>1</sub>/10, where C<sub>1</sub> is the smaller of the two multivibrator capacitors (circuit middle).

- A further interconnection is shown right. When Vout is high C2 charges at a faster rate when the first oscillator's output is high than when it is low. Similarly, the discharge rate of C2 depends on whether one or both outputs are low, thus giving alternate signal outputs of low mark-to-space ratio, followed by high mark-to-space ratio.

#### Further reading

Texas Instruments: 1971 Seminar Slide Book. Texas Instruments: SN7413 Data Sheet.

#### Cross references

Series 2, cards 3, 8. Series 8, card 10.

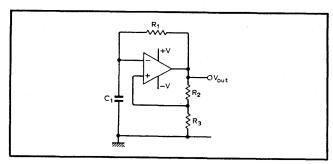

## Operational amplifier astable circuit

#### Typical performance

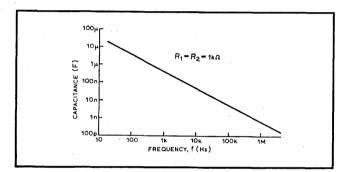

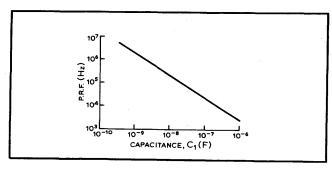

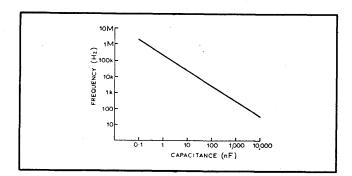

IC: 301 Supply:  $\pm 15V$ C<sub>1</sub>:  $4.7nF \pm 5\%$ R<sub>1</sub>:  $4.7k\Omega \pm 5\%$ R<sub>2</sub>, R<sub>3</sub>:  $5k\Omega \pm 5\%$  Output square wave: 28V pk-pk Slew rate: 8V/μs

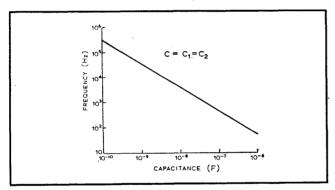

Variation of frequency with feedback factor and capacitance  $C_1$  shown

on graphs.

#### Circuit description

The circuit shown uses an operational amplifier where the output switches between the positive and negative saturation levels of the amplifier, giving a square wave output. The period of the waveform depends on the time constant  $C_1R_1$  and the feedback factor, determined by the ratio of  $R_3/(R_2+R_3)$ . Assume the output has switched to the positive saturation level; the voltage at the non-inverting input is  $+V_{\rm sat}R_3/(R_2+R_3)$  and the voltage at the inverting input is negative with respect to this value. However capacitor  $C_1$  now begins to charge towards  $+V_{\rm sat}$ , but when the capacitance voltage

is almost equal to the feedback voltage, the amplifier comes out of saturation, and the regenerative action due to the positive feedback drives the amplifier quickly into negative saturation before the capacitance voltage can alter.  $C_1$  will now charge towards  $-V_{\rm sat}$ , but again a rapid transition to the positive saturation state will occur when the voltage across  $C_1$  reaches  $-V_{\rm sat}R_3/(R_2+R_3)$ , and the cycle repeats. The duty cycle of this astable circuit is almost independent of the pulse repetition frequency, because the threshold levels are fairly well specified to each op-amp.

#### Component changes

Useful range of  $R_1$ : 6.8k to  $2.2k\Omega$ .

Useful range of  $C_1$ :  $10\mu F$  to 4.7nF for  $R_1 = 4.7k\Omega$ .

Frequency stability: For  $C_1$ : 22nF,  $R_2$ ,  $R_3$ : 5k $\Omega$ ,  $R_1$ : 4.7k $\Omega$ , supply of  $\pm 15$ V and f = 4470Hz, decreasing supply to  $\pm 10$ V reduces frequency by <1%.

Operation possible down to  $\pm 3V$ ; frequency down by 8%. Any other operational amplifier may be used, e.g. 741, but frequency range restricted because at higher frequencies waveform becomes trapezoidal. Typically, for  $R_1 = 2.2k\Omega$ ,  $R_3/(R_2 + R_3) = 0.7$  and  $C_1$  from  $10\mu F$  to 220nF, frequency in the range 24Hz to 1.8kHz. Slew rate  $0.6V/\mu s$ .

A comparator such as the 72710 will give an output pulse excursion of -0.5 to +2.8V for supplies of +12V and -6V. For  $R_2$ ,  $R_3$ : 5k $\Omega$ , useful range of  $R_1$  is 1.5k to 6.8k $\Omega$  and  $C_1$  47pF to  $22\mu$ F giving frequencies in the range 630kHz to 3Hz.

#### Circuit modifications

- Interchange  $C_1$ ,  $R_1$  and the input connections as shown left. For similar component values as in main diagram, frequency is reduced to approximately one third. Note that the derivative of square-wave output is obtained at the non-inverting input.

- Output levels may be clamped for driving t.t.l. loads by connecting a zener diode/resistance network across the output. Clipping at much lower current levels is possible with some amplifiers (e.g. 301), where access is available to the drive point of the output stage. An adjustable arrangement is shown in the middle circuit.

- An unequal mark-to-space ratio may be obtained by using the circuit shown right. The two resistors  $R_{1a}$  and  $R_{1b}$  are selected by the switching action of diodes  $D_1$  and  $D_2$ ,  $D_1$  conducting when the output is negative, and  $D_2$  when the output is positive.

#### Further reading

Clayton, G. B., Operational Amplifiers, Wireless World, vol. 75, 1969.

Shah, M. J., Feedback pot extends multivibrator duty cycle, *Electronics*, September, 1971, p. 62.

National Semiconductor application note AN4-1.

### Cross reference

Series 3, card 5 Series 8, cards 10, 12.

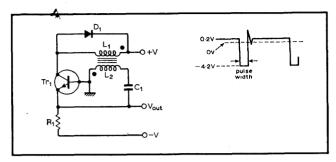

## Series 8: Astable circuits 6

# Astable blocking oscillator

#### Typical performance

Supply: +10V,  $860\mu$ A, -3V 1.1mA

$Tr_1: BC125, D: SD2$  $R_1$ : 6.8k $\Omega$ ;  $C_1$ : 4.7 $\mu$ F

$L_1$ : 30 turns of 36 s.w.g. en. Cu

$L_2$ : 15 turns of 36 s.w.g.

en. Cu; both on FX2049

Circuit description

Many multivibrators have their timing determined by the interval for which an energy storage element holds an active device in the off state. The output pulse is then available at a high output resistance point, at a low power level, and its rise and fall times are significantly influenced by stray capacitance. The blocking oscillator is an example of circuits which overcome these problems by timing the output pulse within the low output resistance, high-current, saturation region by use of a transformer to provide positive feedback with a loop gain greater than unity. Successful design depends on correct choice of the transformer, which should have small stray capacitances and a magnetizing inductance much larger than its leakage inductance. These requirements can be met by making the transformer physically small, interleaving the windings and using a high-permeability core.

At switch-on the base-emitter junction is forward-biased and the collector current rapidly rises to almost equal the emitter current which depends on  $R_1$  and -V. The transformer ensures that a much larger emitter current flows to saturate Tr<sub>1</sub> and C<sub>1</sub> charges in a direction that reverse-biases the baseemitter junction causing Tr<sub>1</sub> to cut-off. A very narrow pulse is generated and the circuit will not regenerate until C<sub>1</sub> has discharged through R<sub>1</sub>. When Tr<sub>1</sub> cuts off D<sub>1</sub> protects the base-collector junction from the large induced e.m.f. in L<sub>1</sub> and restricts  $V_{CB}$  to +V. Capacitor  $C_1$  should be large enough to ensure that the magnetizing inductance of L<sub>1</sub> controls the pulse width and C<sub>1</sub> controls the off-time. The pulse width depends on  $C_1$  rather than  $L_1$  if  $C_1$  is too small.

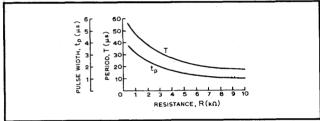

Component changes

Useful range of +V: +4 to +14V;  $-V_{min}$ : -1V. Useful range of  $R_1$ : 470 $\Omega$  to  $10k\Omega$ .

C<sub>1</sub>(min): 470nF.

Minimum load resistance at  $V_{out}$ : 2.2k $\Omega$ .

Frequency stability: -0.96%/V increase in +V, -0.77%/V

increase in -V.

#### Circuit modifications

- It is often convenient to obtain the output pulse from a third winding L<sub>3</sub> to provide d.c. isolation, a suitable transformer turns ratio for  $L_1$ ,  $L_2$  and  $L_3$  being n:1:1.

- A diode D, can be connected as shown left to prevent saturation of the transistor. As the collector current increases during switch-on, the collector voltage falls until it reaches +V<sub>A</sub> causing D<sub>2</sub> to conduct clamping the collector at approximately +V<sub>A</sub>. The current shunted from the collector by D<sub>2</sub> decreases as that in the magnetizing inductance of L<sub>1</sub> increases, the on period of  $Tr_1$  ending when the diode current falls to zero.

- Middle left circuit shows a single-supply version of the circuit with R<sub>1</sub> and C<sub>1</sub> in the emitter. The R<sub>1</sub>C<sub>1</sub> time constant determines the time for which Tr<sub>1</sub> is off and hence the markto-space ratio can be varied by means of R<sub>1</sub>. Alternatively, the p.r.f. may be adjusted by means of R<sub>2</sub> which controls the base potential and hence the timing of the off/on transition.

- The R<sub>1</sub>C<sub>1</sub> timing components may be connected to the base of Tr<sub>1</sub> as shown in the middle right circuit with a potentiometer R2 fixing the emitter voltage and hence the time taken for Tr<sub>1</sub> to switch on as C<sub>1</sub> charges through R<sub>1</sub>.

- An R-C circuit capable of producing very narrow pulses and very small mark-to-space ratio is shown right. Pulse widths of around 250ns with a mark-to-space ratio of at least 1/100,000 are obtainable with -V of -6V,  $-V_A$  of -0.5V,  $Tr_1$ : BSX29;  $Tr_2$ : BSY17;  $D_1$ : EA828;  $R_1$ : 100k $\Omega$ ,  $R_2$ ,  $R_4$ : 50 $\Omega$ , R<sub>3</sub>: 2M $\Omega$  and C<sub>1</sub>: 50nF.

Further reading

Linwill, J. G. & Mattson, R. H., Junction transistor blocking oscillators, Proc.I.R.E., 1955, pp. 1632-9.

Strauss, L., Wave Generation and Shaping, Chap. 12, McGraw-Hill, 1960.

Fontaine, G., Transistors in Pulse Circuits, Chap. 10, Philips,

Tesic, S., Multivibrator with very small mark-to-space ratio, Electronic Engineering, 1967, pp. 671-3.

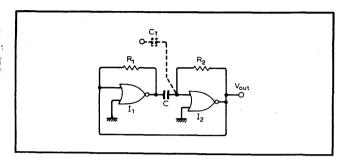

## T.t.l. dual inverter astable circuit

#### Typical performance

Supply: +5V IC: ½ 7402  $R_1$ ,  $R_2$ :  $1k\Omega \pm 5\%$ C: 100pF ±5% Frequency: 2.78MHz

Stability  $> \pm 1\%$  for supply in the range 4.75 to 5.25V for a span of 3kHz to 3MHz

Circuit description

Capacitor C<sub>1</sub> alternately charges and discharges through R<sub>2</sub> because loop gain of the system ensures that the output of the second inverter switches between logic 0 and logic 1 states. When the potential difference with respect to ground at the input of I2 crosses the critical level. Resistor R1 is necessary to bias the first inverter I<sub>1</sub>, and thus prevent the possible stable state of inverter I1 output at almost 0V in the logic zero state, and the output of I2 in the logic 1 state. Charge and discharge cycles have different durations because the input switching level is not symmetrical with respect to the output 0 and 1 states, and also there is an additional charging path for the input of the second inverter at 0 state. Note that when using nor gates as inverters, the unused input should be tied to logic 0 voltage level.

#### Component changes

Useful range of C: 100pF to  $22\mu F$ . Useful range of  $R_1$ : 220 $\Omega$  to  $1k\Omega$ . Useful range of  $R_2$ : 150 $\Omega$  to  $1k\Omega$ . Alternative IC: SN7404 hex inverter.

Circuit operates within the supply range 4.5 to 6V, but not

guaranteed outside t.t.l. voltage limits.

If an attempt is made to achieve high frequencies, the range of resistance values is critical. Typical values  $R_1$ :  $1k\Omega$ ,  $R_2$ : 330 $\Omega$ , C: 120pF, f: 6.7MHz. With nor or nand gates, a spare input is available for external synchronization. Frequency will lock over the range of 4:1 with input pulse widths down to 100ns (positive-going pulse for nor, and negative-going for nand). Capacitive coupling of the trigger source may be used with the inverters of SN7404. Typically  $C_T = C/100$ . Three separate, harmonically-locked astables can then be produced.

#### Circuit modifications

Remove R<sub>2</sub> and connect the capacitor in the feedback loop (circuit left). The third inverter sharpens up the waveform. With supply of +5V, C: 22nF, R<sub>1</sub>:  $1k\Omega$  max. to  $100\Omega$ min., frequency is in the range 22.5 to 165kHz; mark-to-space ratio approximately 0.6/1.

Middle circuit uses the SN7404 again, where frequency of oscillation is determined by the propagation delays through the gates. The external capacitance changes the delay associated with two gates and thus alters the frequency. Useful range of C: 1 to 10nF. Frequency 4 to 0.5MHz. Waveform essentially square, but deterioration evident above about 3MHz. Frequency stability fairly poor. Approximately  $\pm 10\%/V.$

Tuning resistors in the middle network comprise the integrated circuit resistors. With perhaps resistance variations of  $\pm 20\%$  from device to device, and a like tolerance over the temperature range -55 to +25°C, the possibility of frequency and pulse width variations exists. This effect can be minimized for a given output by connecting precision external components as shown right. Output frequency may then remain within  $\pm 5\%$  for device or temperature changes. Typically R should be  $1k\Omega \pm 1\%$ .

#### Further reading

Malmstaat and Enke, Digital Electronics for Scientists, Benjamin, 1969.

Wide range multivibrator costs just 25c to build, Electronics, 1971, p. 59.

MDTL Multivibrator Circuits, Motorola application note AN-409.

#### Cross reference Series 8, card 8.

## Series 8: Astable circuits 8

## Coupled logic gates astable circuit

#### Typical data

Supply: +5VICs: 1 SN7402N  $R_1, R_2: 2.2k\Omega \pm 5\%$  $C_1, C_2: 0.1 \mu F \pm 5\%$ Frequency: 2015Hz

Mark-to-space ratio:

1.27:1

Pulse excursion: 0.3 to

Connect unused inputs to ground for inverter

operation.

Circuit description

The values of the current sinking resistors R<sub>1</sub> and R<sub>2</sub> are critical in this type of circuit, which uses nor logic gates in a cross-coupled mode. It is possible for both gate inputs to sink logic 0 level input currents simultaneously, and this produces a stable state in which both outputs are at logic 1. To avoid this choose values of R<sub>1</sub> and R<sub>2</sub> so that the gate input levels are near the logic threshold level; as the capacitors go through their charging cycles, one gate will be above and one below the threshold level. Assume the Q output has changed from the 0 to 1 logic level of approximately +3V due to the input having reached the threshold value. This output transisition is coupled through the capacitor C2 to make the input of the first gate high, and hence the output Q is low or logic 0. As C2 charges up towards the positive supply via R2, the voltage across R2 and hence the input level at the first gate decreases. At the same time C1 charges via the base resistor of the input transistor of the gate. The output will change state at a time dependent on whichever gate input first crosses the threshold level. Output  $\overline{Q}$  will then be high (approximately +3.0V) and

Q low. Capacitor C<sub>1</sub> will now tend to charge in the opposite direction towards d.c. supply via R1, and C2 also charges in the opposite direction via the input transistor of the first gate until the outputs change state, then the cycle repeats.

Frequency of oscillation is determined by C1, C2, R1 and R2. If  $C_1 = C_2 = C$ ,  $R_1 = R_2 = R$ , the frequency is approximately  $1/2\pi CR$  Hz, where C is in farads and R in ohms. Provided resistors are carefully chosen to ensure self-starting, a wide range of frequencies are available by altering  $C_1$  and  $C_2$ . This type of circuit using standard gates or inverters does not provide stable frequencies as the threshold voltages depend on temperature and supply voltage.

Circuit changes

Use MC7402F, though note pin numbers different.

Useful range of R<sub>1</sub>, R<sub>2</sub> is restricted to ensure that circuit starts:  $2\cdot 2$  to  $3\cdot 3k\Omega$ .

Useful range of C<sub>1</sub>, C<sub>2</sub>: 27pF to 10µF with the above resistor

With  $C_1 = C_2 = 0.1 \mu F$ , and a supply of +5V, a variation of supply voltage of  $\pm 5\%$  produces a percentage frequency change of +5% or -9% respectively. Nand gates may be used in place of nor gates. In this case,

unused pins should be connected to the positive supply line. Waveform of basic astable circuit is improved when the output is applied through an additional gate.

Mark-to-space ratio adjustable by having different values of  $C_1$  and  $C_2$ .

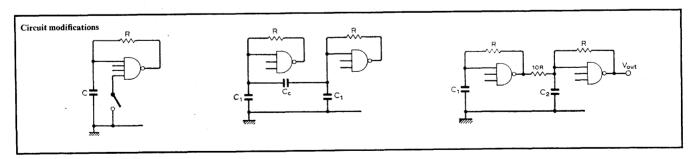

#### Circuit modifications

• Range of resistance values for R<sub>1</sub> and R<sub>2</sub> ensuring selfstarting increased slightly, if R2 is taken to output (left). Range then 1.5 to  $3.3k\Omega$ .

Emitter-coupled logic gates in the middle configuration can provide a high frequency signal, but the component values tend to be critical. IC<sub>1</sub>, IC<sub>2</sub>, IC<sub>3</sub>: ½/MC1011 quad-nor gates using  $1.5k\Omega$  pull-down resistors; supply: -5.2V. Unused input pins connected to - V<sub>s</sub>. Repetition frequency 25MHz. Waveform improved by third gate.

Arrangement shown right would use a single quad twoinput nand gate, useful C range being 10pF to 1µF. Selfstarting problem may be overcome with an extra gate, but a 3-input nand gate then required (cf. Mullard).

**Further reading**

Integrated Logic Circuit Applications Mullard FJ Range, Mullard Ltd., 1968.

Malmstadt & Enke, Digital Electronics for Scientists,

Benjamin., 1969.

2MHz Square Wave Generator uses two TTL gates, p. 110, 400 ideas for design, vol. 2, Hayden.

Simple clock generator has guaranteed start-up. Electronic

Design, vol. 13, 1971, p. 86.

#### Cross reference

Series 8, cards 7 & 2.

## Emitter-coupled astable circuit

### Typical performance

Supplies: +5V, 6.4mA;

-5V, 2.5mA

$Tr_1, Tr_2: 2N706$  $R_1, R_2, R_5: 470\Omega$

$R_3$ : 3.3k $\Omega$ ;  $R_4$ : 4.7k $\Omega$

C<sub>1</sub>: 1.5nF P.r.f.: 1MHz Mark-to-space i

Mark-to-space ratio:

1.04:1

Rise and fall time:

≈ 30ns

Circuit description

Compared with a conventional saturating, cross-coupled astable circuit, this emitter-coupled circuit uses a single timing capacitor, is capable of producing an improved output waveform, can operate at higher frequencies and can be designed to provide a much better frequency stability. The higher switching speeds are obtained because neither transistor is allowed to saturate and the output waveform does not switch between wide limits.

Consider the circuit to be in the state of  $Tr_2$  off and  $Tr_1$  on. The emitter current of  $Tr_1$  divides into a component in  $R_3$  and a charging current in  $C_1$  and  $R_4$ . At the instant that  $Tr_1$  switches on this charging current produces negligible p.d. across  $C_1$  and a p.d. across  $R_4$  sufficiently large to ensure that  $Tr_2$  is off. As  $C_1$  charges, its p.d. increases and that across  $R_4$  falls until the base-emitter junction of  $Tr_2$  becomes forward-biased. Transistor  $Tr_2$  begins to conduct and the emitter current of  $Tr_1$  falls causing the collector potential of  $Tr_1$  and the base potential of  $Tr_2$  to rise. This action causes  $Tr_2$  to conduct more heavily and  $Tr_1$  to switch off. This sequence is then repeated with  $Tr_2$  emitter providing the current to charge  $C_1$  through  $R_3$  until the switching action restores the circuit to its original state of  $Tr_2$  off and  $Tr_1$  on.

Tr<sub>1</sub> will be on for a time:

$t_1 = C_1 R_1 R_5 (R_3 + R_4)/R_3 (R_1 + R_5) + R_1 R_5$  and Tr<sub>2</sub> will be on for a time:

$$t_{2} = \frac{C_{1}(R_{3} + R_{4})}{\left[\frac{+V}{|V| - V_{\text{BE on}}}\right] \left[\frac{R_{4}}{R_{1}} - \frac{R_{5}}{R_{1} + R_{5}}\right]} + \frac{R_{4}(R_{1} + R_{5})}{R_{1}R_{5}} - \frac{R_{4}}{R_{3}} - 2$$

Component changes

Useful range of +V: +2 to +14V.

Useful range of -V: -2 to -10V.

Useful range of  $R_1$ ,  $R_2$  and  $R_5$ : 220 $\Omega$  to 4.7k $\Omega$ .

$R_{3(min)}$  1k $\Omega$  (m-s ratio 3.4/1),  $R_{3(max)}$  27k $\Omega$  (m-s ratio 1/10).  $R_{4(min)}$  1k $\Omega$  (m-s ratio 1/4),  $R_{4(max)}$  33k $\Omega$  (m-s ratio 8/1).

Useful range of  $C_1$ : 180pF to  $1000\mu$ F.

Frequency stability: -1.2%/V increase in +V, -6%/V increase in -V.

Tr<sub>1</sub> and Tr<sub>2</sub>: ME4103, 2N708, HE301, BSY95A.

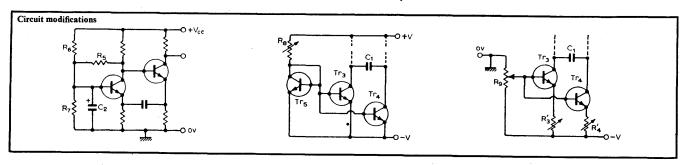

#### Circuit modifications

• If  $R_3$  and  $R_4$  are replaced by a potentiometer connected across  $C_1$  with its sliding contact taken to the -V rail, the mark-to-space ratio of the output waveform may be varied without changing its frequency.

• The on-time of  $Tr_1$  is independent of the supply voltages. and the on-time of  $Tr_2$  depends on the ratio  $+V/[|-V|]_{-V_{BE(0n)}}$ . Hence, high frequency stability is obtained if the ratio of the supply voltages is constant. This condition is assured if only a single supply is used as shown left which can provide a frequency stability of 1% for a  $\pm 50\%$  change in  $\pm V_{CC}$ .

•  $R_3$  and  $R_4$  in the original circuit may be replaced by constant-current tails. Middle circuit shows a pair of parallel current mirrors making the emitter currents of  $Tr_1$  and  $Tr_2$  equal and controlled by  $R_8$ , allowing the frequency to be varied without affecting the mark-to-space ratio.

• The constant-current sources may be voltage controlled, by R<sub>9</sub> in the circuit shown right and the currents in Tr<sub>1</sub> and Tr<sub>2</sub> controlled independently by R<sub>3</sub> and R<sub>4</sub> respectively.

A larger amplitude output, at slower speed, may be obtained by connecting the original output point to the base of a p-n-p transistor with its emitter connected to the +V rail and its collector returned the -V rail through say a  $1-k\Omega$  resistor. If this resistor is connected instead to the 0-V line a t.t.l.-compatible output is obtainable using +V = +5V.

#### **Further reading**

Beneteau, P. J. and Evangelisti, A., An Improved Emitter-Coupled Multivibrator—SGS-Fairchild application report APP-59, 1963.

Electronic Circuit Design Handbook, TAB Books, 1971, pp. 86/7.

### Cross reference

Series 3, card 2.

## Series 8: Astable circuits 10

## Discrete-component Schmitt astable

#### Typical performance

Supply: +9V, 5.6mA  $Tr_1$ ,  $Tr_2$ : 2N706  $R_1$ :  $10k\Omega$ ;  $R_2$ :  $4.7k\Omega$  $R_3$ ,  $R_4$ :  $470\Omega$   $R_5$ : 2.2k $\Omega$ ;  $C_1$ : 10nF P.r.f.: 9.83kHz Mark-to-space ratio:

1.13/1

Rise time: 400ms Fall time: 300ns

Circuit description

This circuit is a Schmitt trigger with overall feedback provided via  $R_1$  and  $C_1$ . Consider  $C_1$  to be uncharged, then when the supply is connected  $Tr_2$  emitter is initially at 0V but  $Tr_2$  immediately conducts due to the base drive through  $R_2$ . Thus  $Tr_2$  emitter rapidly switches to a level close to  $+V_{CC}$  and, with  $R_3 = R_4$ ,  $Tr_1$  emitter rises to half this value. However,  $Tr_1$  remains cut off due to the lack of base drive. Capacitor  $C_1$  begins to charge "exponentially" through  $R_1$  aiming to reach the emitter potential of  $Tr_2$ , but when the capacitor voltage exceeds that at  $Tr_1$  emitter the capacitor begins to discharge mainly through  $R_1$ ,  $R_3$  and  $R_4$  and partially through  $R_5$ ,  $Tr_1$  base-emitter junction and  $R_4$ , thus driving  $Tr_1$  on and into saturation.

The collector potential of  $Tr_1$  falls to a low value as also does  $Tr_2$  emitter, their being insufficient p.d. available to keep  $Tr_2$  in conduction so that it switches off.  $C_1$  continues to discharge until  $Tr_1$  comes out of saturation, when its collector potential

rises sharply. This rise is transferred to  $Tr_2$  emitter, which begins to conduct, and hence to the emitter of  $Tr_1$ . This positive feedback rapidly cuts off  $Tr_1$  leaving  $Tr_2$  in full conduction until, as  $C_1$  charges again through  $R_1$ , the higher potential needed at  $Tr_1$  base to restart the cycle is attained.

Component changes

Useful range of  $+V_{CC}$ : +4 to +15V. Useful range of  $C_1$ : 100pF to  $1000\mu F$ .

Frequency stability: -0.46%/V increase in  $+V_{CC}$ .

$R_{1(min)}$  470 $\Omega$  (m-s ratio 1/5),  $R_{1(max)}$  1M $\Omega$  (m-s ratio 48/1).  $R_{2(min)}$  680 $\Omega$  (p.r.f.: 77kHz),  $R_{2(max)}$  100k $\Omega$  (V<sub>out</sub> reduced to +5.2V)

$R_{3(min)}$  47 $\Omega$  (m-s ratio 5/1),  $R_{3(max)}$  2.2k $\Omega$  (m-s ratio 1/3, f ~ 31kHz)

$R_{4(min)}$  47 $\Omega$  (m-s ratio 1/2.8,  $f \approx 33kHz$ ),  $R_{4(max)}$  2.2k $\Omega$  (V<sub>out</sub> reduced to 5V pk-pk).

Useful range of  $R_{\delta} \approx 220\Omega$  to  $47k\Omega$ .

$Tr_1$  and  $Tr_2$ : ME4103, BC107, BC109, 2N3904. Observe  $V_{BE(max)}$  as well as  $V_{CE(max)}$  rating.

#### Circuit modifications

- If  $R_1$  is not too large the p.r.f. only is affected by adjusting the  $R_1C_1$  time constant; this will not be the case when  $R_1$  reaches a value that is comparable with the relatively high resistance discharge path through  $R_5$ ,  $Tr_1$  base-emitter junction and  $R_4$ . Both the p.r.f. and mark-to-space ratio can be made variable by varying the  $R_3/R_4$  potential divider ratio. Resistors  $R_3$  and  $R_4$  can conveniently be made into a continuously-variable potentiometer or  $R_4$  can be made a voltage-variable resistor, e.g. by use of a f.e.t.

- When a small, but controlled, mark-to-space ratio is required R<sub>1</sub> may be replaced by the resistor-diode combination shown left. Both diodes could be of the 1N914 type. The circuit may be synchronized from an external oscillator by resistive coupling to the emitter of Tr<sub>1</sub> or by capacitive coupling to its base.

- Addition of  $Tr_3$ , as shown middle, allows the timing of the output square wave to be more nearly controlled by the  $R_1C_1$  time constant.  $Tr_1$  and  $Tr_3$  form a long-tailed pair so that the junction of  $C_1$  and  $R_1$  are effectively connected to one intput of a differential operational amplifier.

- Circuit right shows a similar form of modification which has the merit of allowing V<sub>out</sub> to swing almost between the levels of the supply rail potentials.

Further reading

SGS-Fairchild: Industrial Circuit Handbook, pp. 48/9, 1967. Sylvan, T. P., The Unijunction Transistor, Characteristics and Applications, General Electric Co., N.Y., 1965, pp. 52/3.

### Cross references

Series 2, cards 2, 7. Series 8, cards 4, 5 & 12.

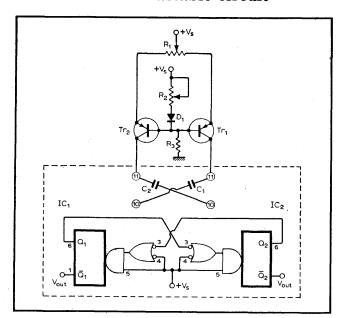

## **Dual-monostable astable circuit**

#### Typical performance

Supply: +5V, 46.5mA ICs: SN74121N (monostable) Tr<sub>1</sub>, Tr<sub>2</sub>: ME0413;

$D_1$ : PS101  $C_1$ ,  $C_2$ : 10nF  $R_1$ : 2k $\Omega$   $R_2$ ,  $R_3$ :  $1k\Omega$ Frequency: 28.6kHz Pulse excursion: 0.2 to 3.6V

Rise time: 100ns Fall time: 50ns

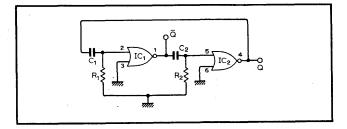

Circuit description

Astable circuits can be constructed out of cross-coupled monostable circuits provided that the output of one monostable can be used to initiate the timing cycle of the other. The circuit shows the interconnection between two t.t.l. monostable i.cs. The timing capacitors for the two parts of the

period are C<sub>1</sub> and C<sub>2</sub>, and these might be equal or different, depending on the need for unity or other mark-to-space ratios. In place of the resistive part of the timing circuit, Tr<sub>1</sub> and Tr<sub>2</sub> provide constant currents, so that the capacitors charge linearly. This allows a ramp waveform to be extracted at pin 11 on either i.c. It has the further advantage that varying the common potential at the bases of Tr<sub>1</sub> and Tr<sub>2</sub> with R<sub>2</sub> allows both charging currents to be varied simultaneously, i.e. a change in frequency without change in mark-to-space ratio. By varying the tapping point on R<sub>1</sub>, the balance between the currents in Tr<sub>1</sub>, Tr<sub>2</sub> collectors are changed and the mark-tospace ratio is varied with a relatively small change in total period, i.e. in frequency. Diode D<sub>1</sub> gives temperature compensation for the base-emitter potential changes of Tr<sub>1</sub> and Tr<sub>2</sub>. Long periods may be attained by lowering R<sub>2</sub> so that the charging currents in the transistors are small, but the period then becomes more temperature and supply sensitive. Independent anti-phase voltages are obtainable at the  $\overline{\mathbf{Q}}$ outputs of the two i.cs without any loading effects on the interconnection circuitry.

Component changes

With  $C_1$ ,  $C_2$ :  $10\mu F$  and minimum setting of  $R_1$ , frequency is 1.6Hz. With  $C_1$ ,  $C_2$ : 10nF, and maximum setting of  $R_1$ , mark-to-space ratio is variable from 0.03 to 0.98.

Frequency stability within  $\pm 3\%$  for a supply change of  $\pm 0.5$  on 5V.

Resistive loading may be reduced to  $2.2k\Omega$  to maintain pulse height within 90% of maximum level. Absolute minimum load 150 $\Omega$  where pulse level is then down to 1.9V.

For fixed capacitance, frequency range roughly 10/1 by varying R<sub>1</sub>.

#### Circuit modifications

• Replacement of  $Tr_1$ ,  $Tr_2$  by resistors connected from pin 11 on each i.c. to supply line, i.e. replacing the current source by the more normal resistive source, gives non-linear charging of  $C_1$  and  $C_2$ , but is a lower cost arrangement (left).

• Any other current source may replace  $Tr_1$  and  $Tr_2$ , e.g. p-channel field-effect transistors, with either variable voltage on the gate, or variable resistance in the source (middle circuit)

• Use a retriggerable monostable SN74L122 in the configuration shown right. This monostable has a similar behaviour to a Schmitt trigger when the timing capacitor is driven from the Q output. Pins 1 and 2 may be taken to supply line and 3 and 4 to ground.

Further reading

Photo-f.e.ts make multivibrator respond to incident light, in 400 Ideas for Design, vol. 2, Hayden, 1971, p.107.

Smith, D. T., Multivibrators with seven-decade range in period, Wireless World, Feb. 1972, pp. 85/6.

### Astable circuit with f.e.t.

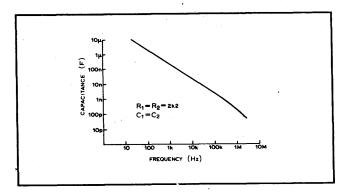

#### Typical performance

Supply: +9V,  $760\mu$ A

Tr<sub>1</sub>: 2N5457;

Tr<sub>2</sub>: BC126

$R_1$ :  $100k\Omega$ ;  $R_2$ :  $10M\Omega$

$R_3$ : 3.3k $\Omega$ ;  $R_4$ : 6.8k $\Omega$

$C_1$ : 1nF

P.r.f. 31.2Hz Mark-to-space ratio:

1.17:1

Circuit description

When the supply is connected both active devices conduct with currents determined by the negative feedback due to R<sub>3</sub> and R<sub>4</sub>. The collector potential of Tr<sub>2</sub> jumps sharply to a level approaching  $+V_{\rm CC}$  and the source of  $Tr_1$  jumps towards  $V_{\rm CC}$   $R_4/(R_3 + R_4)$ . With  $C_1$  initially uncharged, the full positive step at Tr2 collector is passed to the gate of Tr1 so that the gate-source junction becomes forward biased by about 500mV and the charging current flows through it to ground via R<sub>4</sub>. The initial charging current in C<sub>1</sub> is thus larger than it would have been if C<sub>1</sub> charged simply through R<sub>2</sub>. The p.d. across R2 falls rapidly as C1 charges through R4 causing the f.e.t. junction to be reverse biased and the charging time constant of  $C_1$  to charge to the much larger value of  $C_1R_2$ . Capacitor C1 continues to charge until the gate potential of Tr<sub>1</sub> falls below its source potential by an amount that approaches the pinch-off value causing Tr<sub>2</sub> to switch off due to the reduction of base current.

The output switches back to virtually 0V as C<sub>1</sub> discharges

through  $R_2$ ,  $R_3$  and  $R_4$ , where  $R_2 \gg R_3 + R_4$ , until the gate source p.d. allows sufficient drain current in Tr<sub>1</sub> to switch Tr<sub>2</sub> on and the circuit re-cycles. Due to the low reverse-bias gate current of the f.e.t., long time intervals can be obtained between the changes of state using reasonable component values, provided that C<sub>1</sub> is a low-leakage type. The accuracy of these long time intervals however depends on ill-defined value of the pinch-off voltage of the f.e.t.

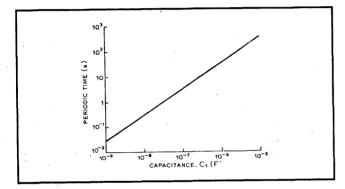

Component changes

Useful range of supply: +6 to +30V.

Useful range of C<sub>1</sub>: 10pF to 100µF, low-leakage type.

$R_{1(min)}$ : 4.7k $\Omega$ .

Useful range of  $R_2$ : 1 to 200M $\Omega$ . Useful range of  $R_3$ : 2.2 to  $33k\Omega$ . Useful range of  $R_4$ : 330 $\Omega$  to  $10k\Omega$ . Minimum load resistance:  $220\Omega$ .

Frequency stability: +1%/V increase in Vcc.

#### Circuit modifications

Another circuit that can produce output pulses separated by a long time interval is shown left. When the supply is connected, the low-leakage capacitor  $C_1$  charges through  $R_1$ until the gate potential of the n-channel j.f.e.t. reaches the threshold voltage of the programmable unijunction transistor Tr<sub>2</sub> minus V<sub>GS(off)</sub> of Tr<sub>1</sub>. On reaching this gate voltage of  $+V_{\rm CC}(R_6/R_5+R_6)-V_{\rm GS(off)}$ , the gate-source junction of  ${\rm Tr_1}$  becomes forward biased and  ${\rm C_1}$  discharges through it to ground via Tr2 and R3 providing an output pulse across R3. Transistor Tr<sub>1</sub> then cuts off and the charge-discharge cycle of C<sub>1</sub> is repeated.

• Caution is necessary in replacing bipolar junction transistors, in circuits that are known to work by field-effect transistors. In the middle circuit Tr1 of a Schmitt astable has been changed to an n-channel j.f.e.t. but for a given pinch-off voltage and R<sub>1</sub>-value there may be insufficient drain-source p.d. to allow the switching action to take place, except by critically adjusting the ratio  $R_3/R_4$ . This situation is improved by inserting a zener diode between the drain of Tr1 and the base of Tr<sub>2</sub>.

Circuit right shows a cross-coupled astable where n-p-n transistors have been replaced with n-channel j.f.e.ts. This circuit will not switch unless R3 and R4 are returned to ground instead of  $+V_{CC}$  and should be returned to a slightly negative rail to ensure self-starting.

Further reading

FET and UJT provide timing over a wide temperature range, in 400 Ideas for Design, Hayden, 1971, pp. 192/3. Watson, J., Introduction to Field Effect Transistors, Siliconix,

#### Cross references

Series 8, cards 2, 5 & 10.

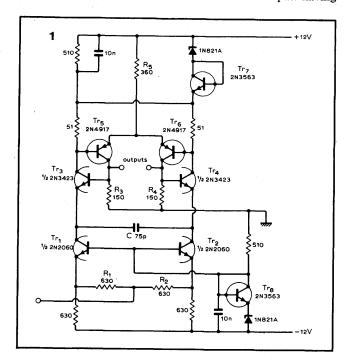

### **Astables**

1. This circuit is a high performance complementary astable. The elements determining the switching functions are the complementary pairs  $Tr_{8}$ ,  $_{5}$  and  $Tr_{4}$ ,  $_{6}$ . These act as complementary Schmitt triggers, channeling the current in  $R_{5}$  via the long-tailed pair formed by  $Tr_{5}$ ,  $_{6}$  into one or other of the load resistors  $R_{3}$ ,  $R_{4}$ . Transistors  $Tr_{5}$ ,  $_{6}$  form part of two distinct circuit functions viz the Schmitt and long-tailed pair switches. The l-t.p. action ensures excellent switching performance since the total current remains constant while the voltage changes required at the bases of  $Tr_{5}$ ,  $_{6}$  to achieve this switching remain small. Timing capacitor  $C_{3}$  is charged alternately by  $Tr_{1}$ ,  $Tr_{2}$  the other transistor of the pair having

its collector current absorbed by whichever of pair  $Tr_3$ ,  $Tr_4$  is conducting at that time. Transistors  $Tr_7$ , sprovide temperature compensation for the biasing networks that stabilize the operating currents.

Because of the totally complementary nature of the circuit the outputs are anti-phase square waves of 0 to +3V, with

Because of the totally complementary nature of the circuit the outputs are anti-phase square waves of 0 to +3V, with operating frequencies claimed to exceed 50MHz. Frequency control input gives linear control over an unspecified range. Aldridge, S. F. Square-wave generator stresses frequency stability, *Electronics*, vol. 46, May 10, 1973, p.98.

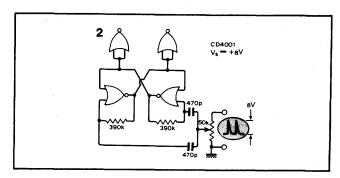

2. This circuit is not itself an astable circuit but is a simple frequency divider that can be added to other astables. Division ratio can be adjusted to any even number from two upwards with increasing dependence on parameters such as supply voltage pulse-height etc. If these two are proportional, as would be the case for an astable operating from the same supply as the divider, then the supply dependence is reduced and ratios up to 30 are claimed to be possible by adjusting the input potentiometer. Operation also depends on the 5-pF gate input which integrates the pulses received from the potentiometer.

Newton, D. C-MOS gate package forms adjustable divider, *Electronics*, March 1, 1973, p.104.