JORDAN DIMITROV | Tradeport Electronics, Vaughan, Canada jodimdim@yahoo.com

Adjust 555-Based Generator's Duty Cycle Without Affecting Frequency

## A free-running generator built on

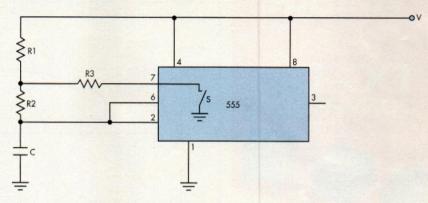

the standard configuration of the 555 timer can't provide a duty cycle of exactly 50%. That's a well-known fact. Fortunately, there are several ways to get around this problem. The best is to place an extra resistor, R3, between the two regular resistors, R1 and R2, and the chip's discharge pin (Fig. 1).

The problem is that variations in R3 strongly affect output frequency (http://home.cogeco.ca/~rpaisley4/LM 555.html#14). This idea shows how to achieve an adjustable 50% duty cycle with minimum frequency change.

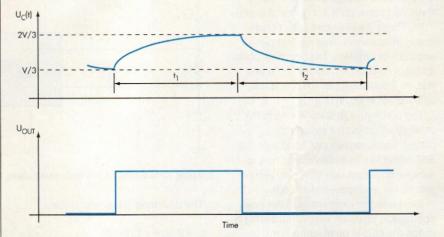

Even with the extra resistor, the timer operates in its usual way. When switch S inside the chip is open, capacitor C is charged through the R1-R2 network (Fig. 2), and the capacitor's voltage rises. When it reaches 2/3 of the power supply, V, the switch closes and capacitor starts discharging. When the voltage drops to the V/3, the switch opens again and the cycle repeats.

q R3/R1

0.0418

0.0764

0.2248

0.3911

0.4068

R2/R1

10

5

1

0.1

0.05

## 1. Adding R3 to a standard 555 timer circuit allows a designer to create a 50% duty cycle.

R3n

$(k\Omega)$

0.137

0.459

4.055

12.826

13.976

The time intervals t<sub>1</sub> and t<sub>2</sub> are:

$$t_1 = R1C(p+1)*In(2)$$

(1)

$$t_2 = R1C \left( p + \frac{q}{q+1} \right) * \ln \frac{q-2}{2q-1}$$

(2)

where p = R2/R1 and q = R3/R1. For a 50% duty cycle,  $t_1 = t_2$ , so:

R2n

$(k\Omega)$

32.795

30.063

18.038

3.280

1.718

$$(p+1)*ln(2) = \left(p + \frac{q}{q+1}\right)*ln\frac{q-2}{2q-1}$$

(3)

And frequency is simply:

$$f = \frac{1}{2t_1} = \frac{0.7213}{R1C(p+1)} \tag{4}$$

Equation 3 is a relation between p and q. If p is set, then q can be calculated. Note that the term under the log operator at the right side must always be positive. This is fulfilled when both the nominator and denominator have identical signs, and it leads to two intervals for q, one from 0 to 0.5 and the other from 2 to infinity. This said, a simple iterative procedure can be used to calculate q. When that's done, R1, R2, and R3 can be defined.

The procedure is as follows:

# TABLE 2: DUTY CYCLE (DC) AND FREQUENCY (F) DEVIATIONS WITH CHANGING RESISTANCES

TABLE 1: R1, R2, AND R3 VERSUS p

R1n

$(k\Omega)$

3.280

6.013

18.038

32.795

34.357

| R1 = R1n + 5%  |               | R2 = R2n + 5%  |               | R3 = R3n + 5%  |               |

|----------------|---------------|----------------|---------------|----------------|---------------|

| DC dev.<br>(%) | F dev.<br>(%) | DC dev.<br>(%) | F dev.<br>(%) | DC dev.<br>(%) | F dev.<br>(%) |

| -0.44          | 0.01          | 0.21           | 4.56          | 0.24           | 0.24          |

| -0.82          | 0.01          | 0.36           | 4.35          | 0.46           | 0.46          |

| -2.56          | -0.05         | 0.83           | 3.25          | 1.80           | 1.80          |

| -5.52          | -0.93         | 0.42           | 0.87          | 5.73           | 5.73          |

| -6.03          | -1.21         | 0.24           | 0.48          | 6.63           | 6.63          |

- Set the desired frequency and select a value for C.

- Select the value of p and calculate q from Equation 3.

- 3. Calculate R1 from Equation 4.

- 4. Calculate R2 = pR1.

- 5. Calculate R3 = qR1.

Table 1 shows the nominal values of R1n, R2n, and R3n determined with this procedure for five values of p, with a frequency of 20 kHz and C of 1 nF.

| reported in the above reference, where   |

|------------------------------------------|

| R3 is the variable resistor.             |

| The differences between theory and       |

| experiment are caused by resistor toler- |

| ances. Obviously, frequency suffers      |

| more from them. If tighter frequency     |

| control is required, a larger value of p |

|                                          |

can be selected and/or more precise

resistors can be used. The first

TABLE 3: RESULTS FROM TEST CIRCUIT DC dev. F dev. DC R1  $(k\Omega)$ (%) (kHz) (%) (%) 2.83 0.07 17.3 49.03 18.881 Ref. Ref. 18.2 50.46 18.866 -0.2219.1 51.77 18.826 -2.60

#### 2. The third resistor doesn't affect the circuit's normal charge-discharge cycle.

Since the resistors must be rounded to standard values, the duty cycle will not be exactly 50%. The question is how to adjust it with minimum change of frequency. The answer is clear from Table 2, where percentage deviations of the duty cycle, DC, and frequency, F, are calculated when one of the three resistors is increased by 5%, while the other two are kept constant. Note that the best results are obtained when R1 is used to adjust the duty cycle.

A circuit designed according to the described procedure (with p = 1) was tested. Resistor values were: R1 = 18.2  $k\Omega$ .  $R2 = 18.2 k\Omega$ . and  $R3 = 4.12 k\Omega$ . Then R1 was modified to be able to change by ±5%. All resistors are of 1% tolerance. Table 3 shows that the results, particularly the duty cycle, were very close to the predictions in Table 2. They're also much better than what is

E-mail: dbs@penton.com · Postal mail to:

**Ideas For Design Electronic Design** 45 Eisenhower Dr., Suite 550 Paramus, NJ 07652

our submission guidelines.

approach affects duty cycle adjustment span; the second affects the price. If needed, frequency can be adjusted independently of the duty cycle by varying capacitor C.

JORDAN DIMITROV, electrical engineer in measurement and instrumentation, received a BSc. MSc, and PhD from the Technical University, Sofia, Bulgaria,

# IDEAS FOR DESIGN WANTED

Send us your Ideas for Design. We'll pay you \$150 for every **Idea for Design** that we publish. In addition, this year's top design as selected by our readers will earn an additional \$500, with two runners up each receiving \$250. You can submit vour Ideas For Design via:

Or by

Go to www.electronicdesign.com for

**READER SERVICE 135**