# Karnaugh Map Display

A low-cost instrument which may be used to assist in teaching logic and Boolean algebra

by Brian Crank\*

Although this concurrence employing the same basic principles on the cardie Workers Workd Logis Diripley Add (May to Docember 1990) any meanblance ends there. The present maranesis is simpler and to wry much charger. The sirves has been reduced to sent four insignment directions indexed to sent four insignment directions three digits lated inside the final fractions doubles. The costs much and sector a first doubles. The costs much and sector a first presends.

Mod you, the present instrument is not nearly so iteration as the carlier design attrough the display is more pleasing to due type. The instrument will produce, on the screen of an occilicocopy, the Karmangh map of any combinational logic circuit If you are accompately familar with Karpaugh maps a impir description will be found in the appendix to this article.

The reason for desping an increment which will produce a Karmagh map for any array is guite anyfe. The student is often imph Beccian algebra and loge through the use of the Karmagh map. It completes the area for the student to see a loge security producing the same map that was used to explain the operation of backs the througy and hyles. In other backs the througy and hyles. In other

You may tenenther that in the ardiat digitaly the characters paraght and care were displayed to the coefficiences and then it to form of a pattern of dots. In the present, design the characters and then its combinetis lines exceedy any powerald down that by hand. A synpace digitary are noted between the instructure and the southercose these returners and the southercose these returners and the southercose the instructure is of the Y deficience in instruction produktion leads it not restored.

As already proteined the central to plyefiel in this behavior and qualitation cause are enginyed. Broadly the elevations of both linear and digital technique and the linear and digital technique and by linear centrals. The choice of whether to displye a booph or a cent as particular position a status by the logo circuit the Karnaugh may of what has to be displayed.

To use the mitrament all one does in

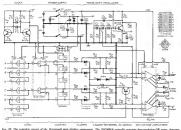

Fig. 1. A simplified block diagram of the beatronicm. Practizelly any oscilloscope will be available because the devised made upon it are study abbough it must be capable of operating from on external involves.

to connect a to the X and Y inputs of an oscilloscope, and connect any logic directly to the instrument; the Karnaugh map for that circuit will then appear on the screen.

<sup>14</sup> A block daymar of the international priority of priority in Fig. 1. In block, a clock, public protection is used to drive in four-block one-block of the counter or point in the start of the st

A content wave coefficient, with a frequency of which higher when the clock generator, produces two company which have a  $90^{\circ}$  produced the two products of the second second

play on the cost, a four-hydrour matrix of the If the switch in the size wave lead to the X operational angelifier is open there will be no horizontal size wave component in the deficient waveform so on the series will appear listen Ia. The 1 is formed by the spin wave insuit to the X arcelifier.

The construct that divers the holder networks also drive a hogic cross when produces outputs that comply with the refer of a Krimsalt may. These cotputs are and to drive the logic crossit year with to driptly and the output of this logic arctin is used to correct the 0<sup>4</sup> switch at the input to the X openvision ampfilies. Each societion of the instrument will now be described in dural.

# Sint wave cocillater

The sime veve conclusion is used to produce a Lassophic figure which increments 0 in the depity and 10 do thut, as we have a develop seen, in runs produce outputs at 0° and 90°. An early versice of the nature meas used a sure wave RC conclusor followed by a 90° phase-with network. Al-tough this weeked a was meanifactory because it was necessary to speedly does the department for the frequency to the respective of the measure of the meas

Fig. 2. The four-section phase-shift outflutor used to produce the characters which form the display. Operating frequency is about 22kHz.

Fig. 3. Astable multiphrator clock generator which runs at about 1.4kHz.

Fig. 4. The Y ladder network. Coopnent reference numbers in brackets refer torbe X ladder. The circula converta the couput of a counter onto a statement wandpare by performing a distribution accurrence.

so be right for the plane shift requered. An LC consists round have been and with the advantage that the frequency adjustment, to ince the operation of the planechill network, world have been opproblem. Howevere, cold, as well as being fairly belies at the frequency we are incerested in, are not the most popular larges in onestructional articles so it was decided to fud a solution using RC clicatory.

The ercelt imployed is shown in Fg. 2. As can be sum it is a single transition phase-shift oscillator. Normally a phasethift oscillator employs three &C sectors, ach sectors phase thifting by (07) so dotain the 180° phase shift necessary to obtain positive factback and oscillation.

In the present design four RC sections

Fig. 5. The equivalent circuits of the indifer network for the four different conditions of the counter driving it.

are employed, each section shifting by  $45^{\circ}$ (4  $\times$   $45^{\circ}$  = 180). It is now a simple matter to pick off the 90° signal after two  $45^{\circ}$ phase shifts at the output of the second 8C section.

The potentionesise R<sub>ask</sub> the only adjustment is the whole more more, is used to vary the to, gain of T<sub>1</sub>, while summarize d.c. conditions. The gain most just be conditions will not occur, if it is too lay outflatter works, if the gain is too lay outflatter will not occur, if it is too lay outflatter works and the top of the seven output from T<sub>1</sub>. The frequency of outflatton is none 23435 but they is not all critical.

## Clock generator and counter

The clock generator a shown in Fig. 3, Little need he said about it as a converticent antable mathy multivibrator which mers at about 1.4kHz.

The four-bet counter is formed by one tall (interstote-transition logic) integrand clouds type SN7493N. This is c. comes in the m.s.l. or moleum scale integration closes. It contains four AF hydrogs and in connected as shown in the same create diagram (Fig. 10). The four the dogs no cassaided to form a standard benary construct to form a standard benary

Looking at only the first two flip-flops, the compute of which are called Q, and Q, the following compute are produced:

The outputs of the second pair of flip-

Wirelos World, April 1971

Fig. 6. Shows how the surgest of the 1.1. Manay assumer is affected by the clock generator. The steps in the wangform are removed by a clamping clocal.

Fig. 7. The champing circuit. The automs to the ladder networks are the rohage drops across three forward-based diodes in series.

Fig. 3. The X algorithm complete complete with the single-transition 1/0 twitch. The Y deficition amplifier certain in the some bas Tr<sub>4</sub> and to canonial component are omitted

Fig. 9. Karnaugh map edge coding. A graticule, the some as this drawing, should be made to that the daplay on the c.r.t. can be neved through it.

Sees. O. and O., produce exactly the same output but at one quarter of the frequency.

### Ladder networks

the binary counter. When the flip-flop Q.ia at 0 the O, currut is connected, via a saturated transister, to the OV lase. When the catput Q, is at 1 it is connected via a saturated transistor to +6V.

The circuit of one ladder network a given in Fig. 4. The inputs Q, and Q, are switched secondate to the table given earlier feer states of the counter, so far as the datret soltare is concerned (Fig. S). If you would care to do the same you will find that the output will rise from OV in equal steps to produce a staircase.

### Clamping network

Unfortunately the output of the fig-does in act a most spare wave Although the rise and fail times are far more than adopasts for the instrument the output of a performing the-flop is affected by its input conditions. Fig. 6 slastrates this posst.

The step in the waveform causes a correspendits step in the cetter of the luckle tetwork which it turn charge certain characters on the display to specir double The cure for this trouble is to odd a clause ing perwork which slices the top off the owner from the flay-dops. This network is shown in Har

The diodes D1 is a solate the cotputs of the flip-flops from each other and resistors R<sub>26 to 22</sub> lensit the current to a safe value The output to the ladder network is now the voltage dron across three dealers in series

### Operational amplifiers and 1/9 calleb

The well known operational approach pro-709 is used in the instrument. The particular version employed (SN72709DN) as manafactured by Teass Instruments and includes ran 709 ameliars in a deale daplituling package. The circuit of the X deflection used for is shown in Fig. 8. The Y defection arrelfer is derived exceet that the 14b unichine transieter, 7r,, and its associated components are ormited.

feedback resistor which sets the ownedl gain of the amplifier. Additionally R, protects the amplifier from scenderes) short circuit of the output loads by finiting the output carriets. R., C. and C. are frequency compensition. components which ensure subility.

The BC108 (77.) is the softsh which is controlled by the enternal legic events It short-presits the 90° output of the sine wave oscillator to ground when a 1 is repared on the c.r.t. Rain of a sufficiently ficently affecting the oscillator stell.

Imaging that the Karanash map of Fig. 9 is superinterested on the c.r.t. face. Recease circuitry the c.r.t. spot first rests in the top left hand square, it then moves to the next square down, then to the square below that until it reaches the bottom of the column The start then files back to the top but this time to the second column. The process continues until all 16 sources heve been scanned. The sast then some back to the first square again and the process to repeated, such is the effect of the two staircorresponds to a particular state of the counter. For mitance, the top left-hand are all 0, that is at the top of both staircase waveforms (both the X and Y amphfare

We also know that each square on a Karnauth man corresponds to a particular set of versibles as defined by the coders at the edge of the map (see appendix if peops servi. We must ensure that when the spot variables represented by that square are available at the output of the entransent for

The 11 (a). This is a simplement of the dupity which shows the same produced by an exclusive-OR gate connected to the A and B success (A B + A B). The observed her here "declared" in that drawn in Normally this automation would be contained on a graticale as shown in Fig. 9, however, this would be very difficult to photograph. The romainder of the abolographs are separation within the unit. (b) L4kHz clock wereform, (c) and were outiliator (22kHz) taken at the entitier of Tr.: of the Y operational amphiler, for this abatamaph the sine were ascillator was duching (c) Y defection satisfy when the dupity at (c) is bong produced and (i) X defection watchest under the same condensus: (a) something of the collector of Tr, when she digalay at (a) is being produced.

feeding to the external logic circuit. We must therefore compare the output of the counter with the Karnaugh map edge codings and rectify any differences that

| Kamsagh map<br>edar opting |   | oputier |    |  |

|----------------------------|---|---------|----|--|

| 8                          |   | - Q. `  | Q. |  |

| ŵ                          | 0 | 0       | 0  |  |

| •                          | 1 | 0       | 1  |  |

| 1                          | 1 | 1       | 0  |  |

|                            |   |         |    |  |

The above table compares the comput of the Y counter with the may's A B edge coding. The issue was terms are different and therefore some logic is necessary to correct the.

Finally on complete from we can say that  $Q_1 = B$  so a direct connection from the connect carpet  $Q_2$  will form the carpet values B.

which is our old fitted the exclusive-OR function, We have already stood that the N contert outputs, Q, and Q, but at a shower true and we can use that the Karmingh map coding. For C and D is the same as for A and R. We must therefore conduct that an identical legit function is required, namely

$$D = Q_1$$

$C = Q_1 Q_2 + Q_2 Q_3$

The circuit of the logic section of the interment can be seen to the lower left. In ad, unit, of the mean encode dispersion  $H_{22}$ . No, and is can be seen that only two integrated circuits are required. The organ variables,  $J = 2 \, etc.$ , are buffreed by simple invariant to prevent actum it consistives from sporting the operation of the control. These traverses also generated by a complement of the variables,  $J \in B \infty$ .

# Complete circuit

$F_{12}$ . To conversely at the circuit disparant on for all theorem latter conversions discourin. The various waveforms present for a particular diplay are shown in Fig. 11, Bottmer the sine wave coefficient and the distance the sine wave coefficient and the children's taken a different route every these and in a variable on the secrets a biblicing (a) Z connection to the coefficsopel in one contend.

# Construction

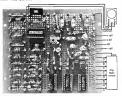

Making the unit is quite straightforward and no special precurations need be taken. A photograph of the layout employed in the prototype is given in Fig. 12; several comporting will not be found in this picture because they not mounted on the reverse side of the board.

It is important to connect pins we used there of the binary counter (SN1491R) to the OV fine. These pins are taposet to a pairs which results the counter if this is not does which results the bailed at OOO and the test will not function. The only adjustment is  $\sigma_{ij}$ , which must be set to give a nodey shaped 0. If you wish to adjust the time of the characters thenging the waits of  $\mathcal{S}_{ij}$ .

Fig. 12. A photograph of the prototype zhowing component positions. It should be noted that some parts have been mounted on the reserve side of the board and are therefore not marked. The integrated circuits are plagged two dual-to-line sockets which makes

will alper the height and R., will also the

### Annediv

Karmuch mags: The Kantaugh map is a ments of meternally shopping all nossible constantions of a number of two-state varables. Because of the way it is constructed it has other properties which make at possible to simplify Boolean expressions with the minersum of effort although it must be said that for more than four venables a is usually better to capploy a more advanced

We will construct a Kamaugh map for four variables. The map will be the same as that displayed on a gra using the instrua Karasagh mup is a square. Each variable (usually labelled A. S. C and D for consquare. To indicate the area occupied by a particular variable a simple edge coding area occupied by the variable A and it is the area adjacent to the Is under A in the odra coding. What is the area adjacent to the Os under A in the edge codine? This is obviously the area representing A If the agenze of Fig. 13(a) is out out and rolled and / become continuous-but more about that later. In Par. 13(h) the areas representutg S and S have been added. The square is now devided in four and each section oppresents one of the four worshie openreading the edge coding, the sections are

You may have noticed that as you progress down the map, or up for this matter, only one of the variables alters at a time and this still agains if the map is rolled into a cylinder arais because A & becomes adsteam to .4 Il

In Fugs, 13(c) and (d) the variables C only these two variables and roll the map into a cylinder the opposite way each section differs by only one variable. Readcound the tube so formed we get

Looking at the mon as a whole it is place

For 13. The construction of a Kornswich exchanging

to see that each one of the sixteen squares possible combinations of the four variables. For instance the too left-hand scenare, an can be seen by the edge coding, represents A & C D and the bottom right hand square

sparses, horizontally or verboally not dasceally, differ only in the negation of one of the variables. We have also proved, by rolling the map into a gainder, that the top of the man is adiapart to the bottom and the left-hand edge is adjucent to the right hand edge.

Two simple examples will show how these properties can be used to simplify Boolean expressions. Consider the expressim A B C D + A B C D. Draw a map as in Fig. 13(d) and put a 1 in the two squares monutaring the terms in the expression and an 0 in all the other searce. Because ranged as shown in Fig. 13(c) The simplified caprouson is derived by taking only yanables which are common in adjacent terms So A B C D + A B C D reduces to A B C

Fig. 130) shows the Karnaugh map for the expression  $\hat{A} \stackrel{\text{def}}{=} \hat{C} \stackrel{\text{def}}{=} \hat{D} + A \stackrel{\text{def}}{=} \stackrel{\text{def}}{=} \hat{C} \stackrel{\text{def}}{=} \hat{D} +$ A B C D + A B C D Al terms are admorted and form a square of their own so only variables contents to all four terms need be used Therefore, from the map of Fig. 13(fr

This brief explanation will serve to give the reader some idea of what a Karnash

Next month a memory unit will be fearihed which can be used with the Karnaugh map display unit, in place of the external logic circuit, to form as 'elecmaps can be stored, displayed or amended at will

### Shopping List

All resistors, except the pointforester, and 150 2 i -470.0 proset potentiometer. Caenchors 10020 1008.67 100a.12V × 5004-12V × 1 Semiconductors SN 1493N, 4-bg binary counter, SN7486N, avail exclasing-OR rate. SN3406N, hex invertor, SN72709DN, daslog ang, BC108 transistory. 1N914 diodes, 5V, 400mW zener diodo

dual-in-line sockets, Leknolty board type LK141. Lektrokit pies,