## Engineer's notebook.

## Circuit layouts minimize noise in digital systems

by Matthew L. Fichtenbaum GenRad Inc., Concord, Mass.

Careful design of power and ground structures on printed-circuit boards and in multiboard systems can do much toward reducing the effects of noise from unwanted signal pickup. The layout techniques recommended here, which minimize ground inductance and stray capacitance, have contributed to the successful operation of many systems.

In Fig. 1, gates A and B, both of which are in one integrated-circuit package, drive gates C and D respectively. The ground path to A and B has some stray inductance, shown as L<sub>ground</sub>, and each signal line has some capacitance to ground, such as C<sub>stray</sub> on the output of A.

If A's output changes from high to low, the charge on C<sub>stray</sub> causes a high instantaneous current to flow into A. The return path for this current is the ground lead, and the inductance in this path causes a voltage spike at the ground terminal. Output B, which should be in the low state, also carries this spike because the output cannot be lower than the ground level of the gate. So gate D,

OUTPUT OF GATE A

GROUND PIN OF A, B

INPUT AT C

INPUT AT D

OUTPUT OF D (ERRONEOUS)

**1. Shaky ground.** Gates A and B suffer unwanted coupling through inductance  $L_{ground}$  in the common ground lead. When gate A discharges  $C_{star}$ , an erroneous signal appears at gate D.

driven by B, sees an erroneous pulse at its input.

This effect may be lessened in several ways. Keeping tracks short, to decrease capacitance C<sub>stray</sub>, reduces the spike amplitude. Although a resistor or inductor in series with the driver can limit the peak discharge current, they reduce system speed and can place unacceptable limitations on fanout. A better attack is to minimize the inductance in the ground lead through the use of a good ground structure.

An ideal solution is the full ground plane common to multilayer boards, which maintains minimal inductance and maximal amount of interconnection. Unfortunately, multilayer boards are expensive and difficult to justify for most circuitry.

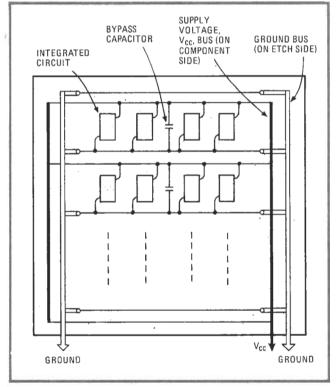

The ground structure on a double-sided board in Fig. 2 gives a good approximation to a full ground plane. A  $V_{\rm CC}$  bus runs up the right and left edges of the front surface of the board, and a ground bus runs up both edges on the back. Horizontal buses connected to the risers at the edges carry  $V_{\rm CC}$  and ground for each IC. The buses' widely separated paths keep ground inductance low. Bypass capacitors, placed between the power and ground buses that feed a row of ICs, suppress the spikes in the supply current when an output switches. Because of the ample interconnection, few bypass capacitors are

2. Grounds for confidence. The solid bar represents the supply voltage bus on the front of the circuit card, and the open bar is the ground bus on the back. The round holes allow back-to-front crossover. The grid structure of the bus lines approximates power and ground planes to keep inductance and noise low.

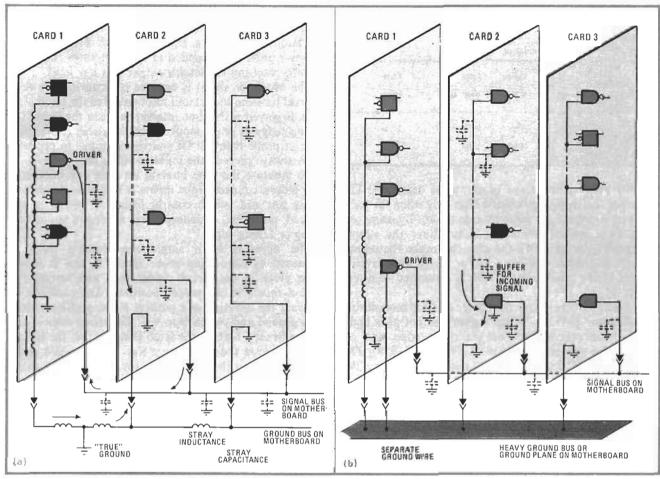

**3. Cool bus.** Stray inductance and capacitance in a multicard system (a) can cause noise problems between cards. The changed signal paths and ground structure in the arrangement shown on the cards (b) make the system less noisy and more reliable.

required; even so, the distance between any IC and a capacitor is small, so the spike path is short.

The same sort of noise problems exist in multicard systems where the logic signals communicate between cards. In Fig. 3a, the driver gate on card 1 must necessarily drive the stray capacitance on three cards and the motherboard. The resulting ground transients at the driver couple into other devices on card 1, so there could be serious noise.

In Fig. 3b, the system has been restructured to reduce noise. A ground plane or several widely spaced heavy ground tracks on the motherboard help keep all card grounds at the same voltage. Cards 2 and 3 buffer

signals from the signal bus with a device near the bus connector. This buffering reduces the capacitive loading on the bus by shortening the length of track directly connected to it. It also keeps the heavy signal currents in the multiple loads local to the receiving card. Locating the driver near the bus connector keeps its paths short.

Perhaps most important, the driver receives its ground through a separate connection directly from the mother-board. This separate line keeps ground transients from affecting other devices on the card. It can dramatically increase the likelihood that the system will function properly, even with the long bus runs encountered when the card is on an extender.