# PRINTED CIRCUIT BOARD LAYOUT and CIRCUIT DESIGN GUIDELINES

#### Dan Fraser

August 15, 2015

Updated January 13<sup>th</sup>, 2020

#### Contents

| Procedures for board design <u>3</u>                      |

|-----------------------------------------------------------|

| Engineering practices for printed circuit layout <u>4</u> |

| Connectivity Check                                        |

| PCB Decals                                                |

| <u>Grounding</u>                                          |

| Star Ground                                               |

| Multiple Ground System                                    |

| Zero Ohm Resistors                                        |

| Single Ground System <u>10</u>                            |

| Chassis Ground                                            |

| Switching Regulators 14                                   |

| <u>Miters</u>                                             |

| <u>Routing</u>                                            |

| Autorouting 15                                            |

| <u>Keepouts</u>                                           |

| DC power input connector wiring <u>16</u>                 |

| Bypass Capacitors on ICs 18                               |

| Power supply filter capacitor wiring 20                   |

| Trace Width 21                                            |

| Trace Clearance                                           |

| Teardrops                                                 |

| Trace Naming       | <u>22</u> |

|--------------------|-----------|

| Routing Op-Amps    | <u>22</u> |

| <u>Clock Lines</u> | <u>23</u> |

| Component Spacing. | <u>24</u> |

| <u>Libraries</u>   | <u>25</u> |

| Text.              | <u>25</u> |

The following are not in any particular order yet.

The following are based on schematic capture using PADs Logic 9.0 and PADs Layout 9.0 from Mentor Graphics. These notes are based on practices at a small high performance audio equipment maker.

# Procedures for board design

These procedures are guidelines. At any stage there may be back and forth communications required between the originator, the Engineer and Design as well as marketing and others. There may even be loopbacks to a previous point in the process at times.

Revising a board for the next version will be a subset of these procedures.

- 1. Basic exterior design of product will come from the the Product Originator. Often someone in upper management, Marketing or wherever the company originates new product ideas.

- 2. Engineer to create block diagram of the product functionality and save that to a new project directory on the server.

- 3. Block diagram to go back to originator of product to see if this is what they intended.

- 4. Back and forth occurs until a consensus on the block diagram is achieved. The feature set may change during this process.

- 5. Engineer to create the schematic for the product. This includes getting the attributes right for all the parts so a BOM<sup>1</sup> can be created from the schematic. Reuse of already proven sub circuits for common functions from previous corporate products is strongly encouraged. The wheel is not to be reinvented.

- 6. Engineer to create the provisional PCB outline. This is generally done by taking the PCB layout of an existing product in the same basic package and modifying it as required. Like using the PCB outline for an existing product in a 19" rack mount case if this product is to also go into a rack mount case. Reuse of basic existing corporate for factors is preferred to save cost on packaging SKUs<sup>2</sup>.

- 7. Engineer to import components to the PCB outline and place the external parts roughly.<sup>3</sup> Routing is not required at this time. New parts and decals to be created as needed.

- 8. Schematic and PCB is sent to Design Department<sup>4</sup> for adjustment of external component placement and 3D modeling of the PCB. The Design Department may move some internal parts without regard of any electrical considerations in order to get the external part placement to

<sup>&</sup>lt;sup>1</sup>Bill of Material

<sup>&</sup>lt;sup>2</sup>Stock Keeping Units

<sup>&</sup>lt;sup>3</sup> External parts are those that impact the enclosure. That is, parts that go through or touch the enclosure including mounting holes.

<sup>&</sup>lt;sup>4</sup> The Design Department is the physical design/3D modeling area.

export to Solidworks. Design will also add drawing numbers to the schematic and PCB and add those to the file name to bring them to company standard.

- 9. The Design Department will work with the Product Originator on the final placement of external parts. Substantial movement may occur from the original positioning by the Engineer. There may even be addition and deletion of features and the Engineer may have to revise the block diagram and schematic. Beware the Feature Creep<sup>5</sup>.

- 10. Once external parts are placed, the layout goes back to the Engineer. Engineer should set all external parts to "Glued" in place.

- 11. The Engineer shall then place internal parts where they make most sense electrically and route the PCB. This includes copper pours and everything else required electrically. There must be no errors on the reports between the PCB and schematic when doing a Comparison on Pads Layout Link unless absolutely unavoidable and documented.

- 12. The board will then be sent to the Design Department for cleanup of the documentation layers on the PCB and all the documentation around the PCB on the layout if that is in their area of competence. Engineers time should not be wasted on making the board pretty. The person doing the cleanup must ensure that all component reference numbers will be visible after the board is assembles. As well, no printing should be over top a via as much as possible.

- 13. Engineer is then to review the layout and release it back to the Design Department.

- 14. If competent to do so, the Design Department is to create the gerber files for board production. As well the Design Department is to also create a documents with BOM and assembly instructions. Engineer input may be required where part attributes are vague.

- 15. Engineer is to use a Gerber viewer to approve the Gerbers for release.

<sup>&</sup>lt;sup>5</sup>The Feature Creep is that nasty creature that wants to keep adding new features to a product in development requiring the whole process start from the beginning over and over. Thus causing budgets and deadlines to get totally blown out of the water. Best fought by a strong manager who wants to get the product out the door (generating revenue) with the suggested new features reserved for the next upgrade of the product. Do not let the perfect stand in the way of the good (and revenue)

# Engineering practices for printed circuit layout.

## Connectivity Check

While it is very important to use the Connectivity checking function on a printed circuit layout, the connectivity checking does not tell you anything is connected in the correct sequence. If there is an error on the schematic, this function will propagate it to the PCB. Therefore it is important that the schematic is correct. There were some incorrect IC and LED decals supplied with PADs originally and while efforts have been made to eliminate these incorrect parts and decals it is important to still check carefully. Particular offenders have been LEDs and 8 Pin dual opamps reversing the + and – input pins. The pin number sequence in the CAE decal in the schematic are not necessarily the pin sequence sent to the PCB decal.

Looking in the Pins tab of the part attributes as shown in the following graphic, it can be seen that the pin sequence and pin numbers in a gate are not necessarily the same. Caution is advised.

| Pin Group | Number | Name | Туре          | Swap | Seq. | Reset       |

|-----------|--------|------|---------------|------|------|-------------|

| ate-A     | 2      |      | Bidirectional | 0    | 1    |             |

| ate-A     | 1      |      | Bidirectional | 0    | 2    | Edit        |

| ate-A     | 3      |      | Bidirectional | 0    | 3    |             |

| ate-B     | 5      |      | Bidirectional | 0    | 1    | Add Pin     |

| ate-B     | 4      |      | Bidirectional | 0    | 2    |             |

| ate-B     | 6      |      | Bidirectional | 0    | 3    | Add Pins    |

| ate-C     | 8      |      | Bidirectional | 0    | 1    |             |

| ate-C     | 7      |      | Bidirectional | 0    | 2    | Delete Pins |

| ate-C     | 9      |      | Bidirectional | 0    | 3    | Renumber    |

| ate-D     | 11     |      | Bidirectional | 0    | 1    | Tionambor   |

| ate-D     | 10     |      | Bidirectional | 0    | 2    |             |

| ate-D     | 12     |      | Bidirectional | 0    | 3    | Сору        |

| ate-E     | 13     |      | Undefined     | 0    | 1    |             |

| ate-E     | 14     |      | Undefined     | 0    | 2    | Paste       |

|           |        |      |               |      |      | Import CSV  |

|           |        |      |               |      |      | Import CSV  |

#### PCB Decals

As much as possible, PCB decals should have their origin point in the physical center of the part to allow easy rotation. And in the case of SMT parts, the center of the decal will then also be at the pick and place center.

## Grounding

#### Star Ground

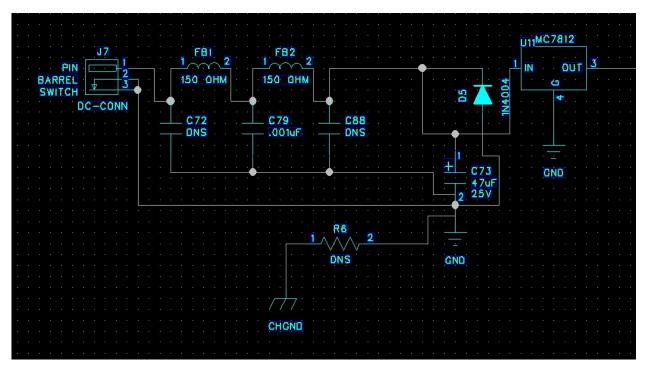

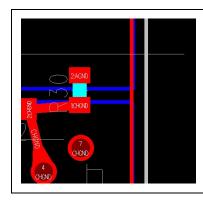

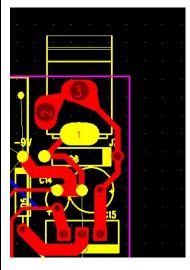

It is recommended that every active PCB has one single point where the various ground paths meet. Especialy mixed signal analog/digital PCBs. In the graphic below, that is C73 pin 2.

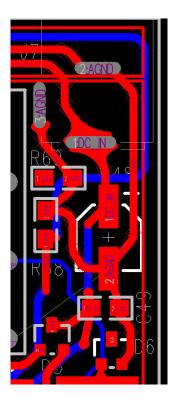

One can see the ground for the input, the chassis ground and the single ground setup all meet there. If there are separate analog, digital or other grounds, this is also where the would meet. R6 is a special SMT decal with copper between the two terminals on a layer the error checker cannot see to make a zero ohm jumper. This allows having different names for the carious grounds yet interconnect them without errors showing up on a clearance check. See below for Zero Ohm resistors. The routing is shown in the next graphic.

The star ground shown has the power jack ground shown in the cyan trace and the ground of the input filter shown in tan going to pin 2 of the capacitor. As well from pin 2 is the zero ohn jumper going to chassis ground. There is a short trace going down from pin 2 which is to a via connecting to the general ground planes. It can be noted that none of these grounds share any conductors to the pad on pin 2.

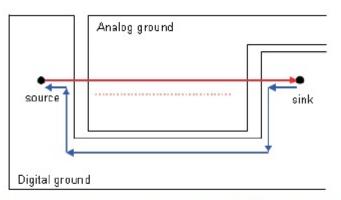

Multiple Ground System

The writer prefers to use multiple grounds back to the star ground point with separate electrical grounds for analog, digital, power input, chassis ground and other ground connections.

Connection between them being made with zero ohm resistors at the ground connection of the power input filter capacitor. Care must be taken that analog, power, digital, chassis and other grounds share no other common connections. If connections must be made elsewhere they must be isolated with small inductors. Connections to the zero ohm jumpers must either directly to a plane of with conductors as wide as possible. At least 25mils wide, preferably wider.

In this graphic from the Twinline R62 R68 are the zero ohm jumpers for the connection is the various grounds and they connect to the ground of C48 through a ground plane... The point here is that are all located at the power input as close as practical to the ground lead of the input filter capacitor.

In the case where the power input has no connection to ground and there is a ground splitter, the ground plane grounds do not connect to the power input filter but to the ground splitter output as close as possible to the output of the ground splitter.

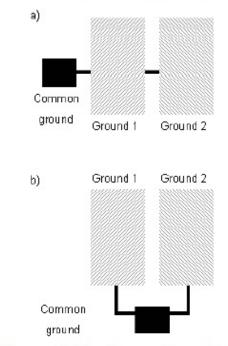

The various grounds should only connect to each other at the ground terminal of the power input filter capacitor. In no case may the ground current from one ground plane pass through a different ground.

Figure 8: Do not let one ground plane pass another ground plane to get connected to the common ground (a). Every ground plane must have its own path to the common ground to reduce noise (b).

Figure 8. Poor and Good Placement of the Common Ground in a Split Ground Environment

#### Zero Ohm Resistors

Zero ohm resistors are used for connecting various traces with different names to the same point. They are especially used for keeping analog, power and chassis grounds apart. As per the graphic to the right showing R30. In the writer's case, this is in their parts library as part type RSMOR-0805. This is to be used on both through

hole and surface mount PCBs as no actual part is stuffed.

Looking at R30, a light blue band can be seen connecting the pads. This is a piece of

copper belonging to no traces on Layer 10 of the PCB as you can see in the Layer Selection window on the right. The layer number does not matter as long as the layer used is not used for anything else.

| Available:                               |                                                | Selected:                   | ОК      |

|------------------------------------------|------------------------------------------------|-----------------------------|---------|

| Layer_6<br>Layer_7<br>Layer_8<br>Layer 9 | Add >>    Add >>   < <remove< td=""></remove<> | Top<br>Layer_10<br>Layer_19 | Cancel  |

| Layer_11<br>Layer_12                     | Ŧ                                              |                             | Preview |

| Other                                    | Items on Primary                               |                             | Help    |

| Board Outline                            | Pads                                           | Ref. Des.                   |         |

| Connections                              | Traces                                         | Part Type                   |         |

| Plated Slots                             | 2D Lines                                       | Text                        |         |

| Non-plated Slots                         | Vias                                           | Attributes                  |         |

| Component outlines                       | Copper                                         | C Outlines                  |         |

| Top Mounted                              | Keepouts                                       |                             |         |

When running the gerbers for the layer the zero ohm jumper is on, one must turn on Layer 10 or whatever layer you used and select Copper for the connection to be made.

When running the BOM make sure the component is shown as DNS.

#### Single Ground System

This where a PCB has a single ground. It is very tempting to have just a single ground for everything. Treating ground like a sewer and throwing everything onto it. This is OK sometimes but in the modern regulatory world, a product with a board with digital circuitry on it, especially in a mixed signal environment will generally not pass Electro Magnetic Compatibility (EMC) testing.

To get around this by putting cutouts or keep outs in the ground planes to make sure digital, analog and power circuit and other ground returns only go to the star ground point are used.

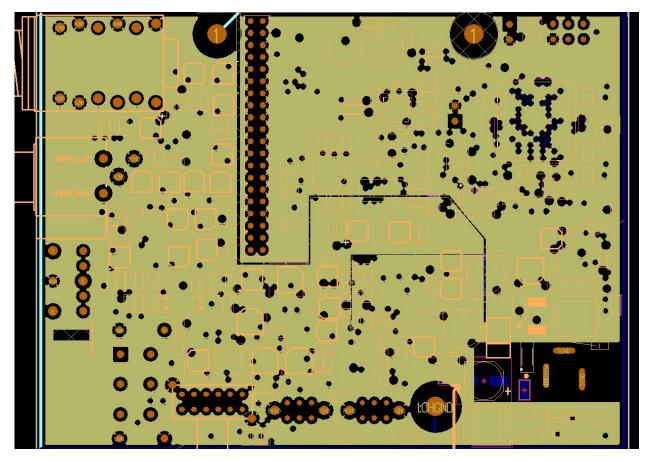

In the above layout keep outs can be seen that section the PCB into various areas. The left side is the analog area while the upper right is the digital section. A separate section near the center is for LED drivers. These cutouts are arranged to funnel each type of current return to the star ground point next to the power connector cutout on the lower right corner.

It is important that no conductors or components cross these cutouts. The drafting properties of the cutouts have to go through all layers and not allow traces, copper or placement. The only exception to the no placement rule is that CODEC chips like the CS4270 which have an analog and digital side. However this will cause a DRC error when checking the keep out clearances.

| J? Drafting Properties       |                                  | x       |

|------------------------------|----------------------------------|---------|

| Type: Keepout                | •                                |         |

| Line settings                |                                  |         |

| Width:                       | Style;                           |         |

| Shape settings               |                                  | -       |

| Scale factor: 1              | Arc approximation error: 0.5     | <u></u> |

| Rotation:                    | Solid copper                     | 2       |

| Copper to trace clearance:   | /5                               | & Hatch |

| Layer:                       |                                  |         |

| <all layers=""></all>        |                                  | -       |

| Net assignment               |                                  |         |

| To assign a net, select a ne | et in the list and click Apply   |         |

|                              | · ·                              | 5       |

| or Assign Net by Click       | and select object in the design, | 쉐       |

| Copper bridge. Select th     | ne nets to bridge                | Net     |

| Keepout Restrictions         |                                  |         |

| ✓ Placement                  | Trace and copper                 |         |

| Component height             | 0 Copper pour and plane a        | irea    |

| Component drill              | Via and jumper                   |         |

|                              | Test point                       |         |

| Select All                   | Accordions                       |         |

|                              | OK Apply Cancel                  | Help    |

See the PADs drafting properties illustration following.

There is also a school of thought that the keep outs should be used only to guide routing and component placement but copper coverage should be continuous. In which case the "copper pour and plane area" box would not be checked. See the link below for this point of view.

http://www.aerospacepal.com/pcb-plane-cuts-kill-emc/

#### Chassis Ground

Care must be taken that no current flows through chassis ground connections. Any current flow will impair the effectiveness of shielding.

The chassis ground must be connected to the power input filter capacitor ground (star ground) connection through a trace as wide as possible. Chassis ground has to be routed in most products to at least one mounting pad so that a connection is made to the case when the product is assembled. While no current flows through a chassis ground conductor it is important that the impedance be kept low which means a trace as wide as practical.

Besides the single connection to the power ground, balanced audio connectors such as XLR connectors may have a chassis ground connection on pin 1. Unbalanced inputs are not connected to chassis ground.

| CHGND |      |  |

|-------|------|--|

|       | DNS. |  |

#### Stackup

On a 6 layer board there are many possible layer stackups. The writer has used, from top to bottom:

COMPONENTS

**GROUND – NO ROUTING**

ROUTING

ROUTING

POWER

GROUND WITH MINOR ROUTING – Where not quite everything could not be done on layers 3 and 4.

All layers would have ground pours though to fill in any unused space on each layer.

Here are some links with opinions on the subject.

```

http://www.aerospacepal.com/6-layer-pcb-designstackup/

http://www.hottconsultants.com/techtips/pcb-stack-up-1.html

http://www.hottconsultants.com/techtips/pcb-stack-up-3.html

http://www.bitweenie.com/listings/standard-4-and-6-layer-pcb-stackups/

```

#### **Switching Regulators**

Switching regulators can be a huge problem for emissions causing problems passing FCC requirements. It is recommended that the manufacturer's spec sheet be obtained and checked to see if a recommended board layout is available. If there is one, follow it as precisely as possible.

#### Miters

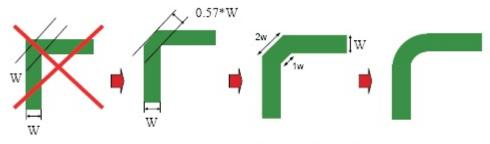

Traditionally miters have been done at 45° angles. In the case of high speed circuits it has been recommended that arcs be use instead. These are not difficult to do in Pads and the writer likes how they look as well. It is suggested that the designer consider the use of arcs miters in cases where PCBs will be in products sent for EMI approval. It has been estimated that using arcs for miters reduce EMI emissions by 2 to 10db which can be the difference between a pass and a fail.

Figure 13. Poor and Good Right Angle Bends

In order to do arcs in PADS the board must be set up for them. Go to Tools-Options. Click on the Design selection. Set "Miters" to "Arc", the Ratio to 3.5 and the Angle to 180.00.

After your board routing is completed to make the corners into arcs:

- 1. Press ESC to clear the existing command

- 2. Right click the mouse and choose Select Pin Pairs

- 3. Press the Home Key

- 4. Select the entire PCB

- 5. Press the "M" key

- 6. Choose "Add Miters"

- 7. Click outside the board area to deselect the pin pairs

- 8. Right click the mouse and choose Select Anything

However some sources feel that arcs make no difference with signals below 1 gHz

If you get a corner that refuses to make an arc that is because one of the traces is split. Press the "O" key to switch to outline view. See the following graphic.

- 1. Highlight the point where the trace is split and press delete.

- 2. Once the split is gone, highlight the angle itself

- 3. Press the M key

- 4. Select Add Miter

- 5. Press "O" again to return to normal view.

#### Routing

#### Autorouting

Do not trust the autorouter. While it may make all the connections on a PCB, the program has no idea of how the wiring of components needs to be sequenced and will almost always do power and ground sequencing incorrectly. It is recommended to only use the Router manually as the time needed to correct Autorouting errors will often exceed the time needed to manually route a PCB using the router program.

#### Keepouts

Digital signals must not cross analog ground planes and vice versa inmixed signal PCBs. Keep outs should be used to insure traces do not cross between the different sections of the PCB.

Figure 7. Loop Area and Crosstalk Due to Poor Signal Routing and Ground Splitting

In digital boards there are often sets of traces that need to be run in as close to parallel as possible and end up about the same length. These sets may include

SDA and SCL

MCLK, SCLK, LRCK and SDATA. SCLK may be called BICK. LRCK may be called LRCLK. SDATA may be called SDIN, SDOUT and may have a number after the name in some cases.

Similarly, balanced audio lines should also run as parallel as possible and be about the same trace length. These trace names often start or end with "+" and "-"

On very dense boards, one may want to make the pads of through-hole parts smaller on the component and internal layers of the PCB while leaving the pads on the solder side full size for good soldering.

#### DC power input connector wiring

Note that the conventional way of drawing schematics rarely gives the correct way to sequence the connections. Especially ground connections.

It is very critical for power inputs to NOT be directly connected to the ground plane of a PCB. The ground side of the power input will be noisy whether the source is a linear supply of a switching power supply. Both the power input and the ground must be connected to a filter capacitor before going to any other place. The only exception would be to a polarity protection diode for the ground side. However this must still not connect to the ground plane. Ground plane connection is to be made only after the connection to a capacitor ground. On the hot side the connection to the capacitor may be made through a series filter resistor or inductor.

For the purposes of an example the Radial Engineering Shotgun is used.

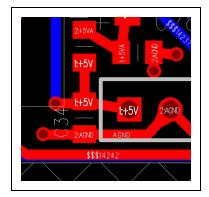

In the following graphic, one can see the leads from the DC input jack go directly to the reverse polarity diode then direct to C15 before they go anywhere else.

The ground plane is cut away around the DC input to make sure that power comes only from after the input capacitor. The power for the input of the voltage regulator, pin 1, comes directly then from the +

pin of C15.

The ground for the regulator is connected to the ground plane. The ground for C15 is routed to the ground plane with a heavy low impedance conductor.

The output, pin 3 of the regulator goes to the + pin of C14 before it goes elsewhere. With the – lead of C14 having a low impedance return to the – lead of C15 as well. Where C15 and C14 have their minus leads connected is the ground reference point for the design. This would be considered the "star ground" point in this design.

Chassis ground would be routed there as well.

A power ground to operate LEDs, relays or other high power devices wound be connected by a zero ohm jumper directly to either the negative lead of C15 or even to the ground lead of the jack, in this case, pin 1 of the DC jack so that share no conductors at all with the audio ground.

#### Bypass Capacitors on ICs

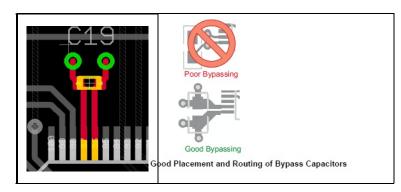

A bypass or filter capacitor is generally any capacitor on the board that has one lead connected to circuit ground or common. On the "hot" or ungrounded pad, they must be routed with at least two conductors going to the pad. A filter or bypass capacitor with only one trace going to it is essentially useless. In most cases there would be 2 traces. One input trace coming from the power source and one trace (or more) going to loads.

A filter or bypass capacitor is like the gasoline filter on a car. You do not run unfiltered gas and filtered gas in and out of the same pipe. The pipes are both one way and separate input and output pipes are provided in a gas filter. The power is the fuel for your circuit and you need separate inlet and outlet conductors for the power the same way that a gas filter on a car has separate inlet and outlet pipes.

C34 in the graphic to the right is an example of a filter capacitor wired incorrectly. With only one trace going to it, it cannot do its job very well and is essentially useless.

In the graphic to the left C34 has been wired correctly. On the hot side the +5V input goes to the capacitor then to elsewhere in the circuit. Similarly the ground lead goes to the ground lead of C34 before going to a pad to the ground plane.

This sequencing of power is rarely made clear on the schematic. Connections to filters is more commonly showed as a part with a single lead going to the part. The board designer must take care to place the bypass capacitor correctly. Bypass and filter capacitors are identified as in most cases, one of the pads connects to ground. All IC

power pins must have a bypass capacitor as close to the power pins as possible. The only exception is that if there are multiple adjoining power pins that may share a capacitor. The power from the power source must ALWAYS go to the capacitor before going to the IC. The power must never be directly connected to the IC. The ground side of the bypass capacitor must be connected to whichever ground is required for that IC. They are never to be connected to the Chassis ground.

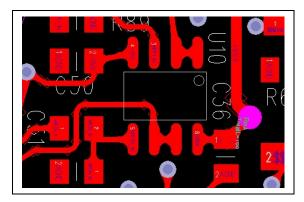

This is a good way to do a bypass in a big chip using a 0402 capacitor with the

capacitor forming a low pass filter between the power and the IC. The capacitor must be as close as practically possible to the IC.

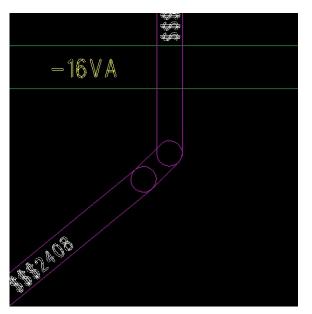

In this graphic from the Radial Decoder Ring one can see the bypass capacitors on pins 4 and 8 or the IC. The positive power trace +6VA goes to the capacitor C36 then to pin 8 of the IC. Likewise negative power trace -6VA goes to C50 then to pin 4 of the IC.

Power must never go to the IC then to the capacitor.

On larger ICs, the manufacturer's spec sheet may have bypassing recommendations and these should be closely followed.

On multi-layer boards power and ground planes should be adjoining layers so that the copper fill of those layers will themselves serve as a decoupling capacitor. If components are on one side only, the ground layer should be next to the component layer. That is, when parts are on layer 1, the ground plans should be layer 2 and the power layer would be layer 3.

When an SMT bypass capacitor connects to a different layer through a via, the via should be jammed up to the bypass capacitor's pads to make the trace as short as possible in order to minimize series inductance. The via holes to a ground or power plane need to be as large as practical to reduce series inductance.

Bulk capacitance of larger value capacitors should be distributed on the board but is not required for every IC.

#### References:

http://www.interfacebus.com/Design\_Capacitors.html

http://www.sigcon.com/Pubs/pubsKeyword.htm#bypass%20capacitors

http://www.sigcon.com/Pubs/edn/thewayhome.htm

http://www.sigcon.com/Pubs/news/2\_3.htm

http://learnemc.com/decoupling-for-boards-without-power-planes

http://learnemc.com/decoupling-for-boards-with-closely-spaces-power-planes

http://www.designers-guide.org/Design/bypassing.pdf

http://www.intersil.com/content/dam/Intersil/documents/an13/an1325.pdf

http://www.ultracad.com/mentor/esr%20and%20bypass%20caps.pdf

#### Power supply filter capacitor wiring.

These are wired as bypass capacitors discussed in the previous section. Traces must always go from the power source, to the capacitor then to the load. This includes both sides of the capacitor. Ground planes may have to have cutouts so that the input ground goes to the capacitor first before connection to the ground plane.

A filter capacitor with only one trace going to either lead is not able to do its job properly. In the lead going into and out of the capacitor, DC current can only flow one way. Which requires separate input and output traces. With only one trace to a capacitor that trace has to have some current going both ways which reduces its effectiveness as a filter.

This and the previous section are especially critical on low noise circuits, circuits with any radio frequency parts, any sort of oscillator, a power converter or any digital circuitry.

#### Trace Width

While 12 mil wide traces are common for signal lines and as low as 9 or 10 mils is common for dense designs. Traces carrying any amount of power, even the minimum amount of power to circuit elements should be at least 25 mils wide. This includes the output traces of headphone amplifier circuits.

### Trace Clearance

Normal clearance is set to 12 mils for everything. The graphic below shows However in some cases on SMT boards this maybe set lower. Traces carrying voltages higher than 35 to 60 volts need to have wider clearances between them.

| Same ne      | t       |          | Trace wid | tth   | Minimu | m Recor | mmended | d Maximum | OK     |

|--------------|---------|----------|-----------|-------|--------|---------|---------|-----------|--------|

| All          | Comer   | Via      |           |       | 8      | 12      |         | 200       |        |

| Via          | ]       | 12       | Classes   |       |        |         |         |           | Cancel |

| SMD          | 12      | 12       | Clearance | 8     |        |         |         |           | Delete |

| Trace        | 12      |          | All       | Trace | Via    | Pad     | SME     | Copper    | 00000  |

| Pad          | 12      |          | Trace     | 12    |        |         |         |           | Help   |

|              |         |          | Via       | 12    | 12     |         |         |           |        |

|              |         |          | Pad       | 12    | 12     | 12      |         |           |        |

|              |         |          | SMD       | 12    | 12     | 12      | 12      |           |        |

| Other        |         |          | Text      | 12    | 12     | 12      | 12      |           |        |

| ounor        |         |          | Copper    | 12    | 12     | 15      | 12      | 12        | +      |

| Drill to dri | I: Body | to body: | Board     | 12    | 12     | 12      | 12      | 12        | +      |

| 6            | 2       |          | Drill     | 12    | 12     | 12      | 12      | 12        |        |

#### Teardrops

Teardrops should be used as much as possible where traces meet pads to strengthen these points. This makes the board somewhat less likely to be damaged if rework or repair is needed. If a teardrop causes an issue in a very small SMT part, by putting a break in the trace inside the pad, formation of a teardrop will be inhibited.

In the Options Menu in the Routing\General page, the "Generate Teardrops" option should be checked and in the Routing\Teardrops page "Display Teardrops" and "Auto Adjust"should be checked.

If a tear drop refuses to form it is generally because of a break in the trace within or near the pad. The procedure to fix this is described in the MITER section.

Also note that some pads with square corners will not generate teardrops at all.

#### **RESEQUENCING INSTANCE NUMBERS**

After the PCB has the instance or reference numbers resequenced, they have to be imported back to the PCB. It is suggested that after this is done one checks one of the text files that pops up that no traces or components have been deleted.

#### Trace Naming

It is suggested that major traces receive specific names. This can make board layout issues easier to troubleshoot. In PADs Logic in the Options select Design. Then make sure the box for "Allow Named Subnets Without Labels" is checked.

When in the PCB layout, enter "NNT" and press Enter to toggle trace names on and off.

NNP turns on pin names.

#### Routing Op-Amps

In routing an opamp the traces on the + and – input leads are critical as the feedback components.

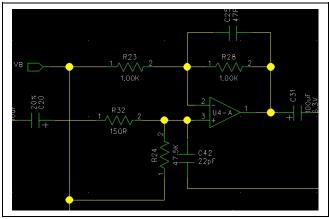

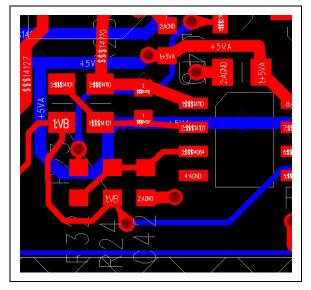

In the graphic the 0603 package capacitor is next to pins 1 and 2 of the op-amp. Then R28 is in parallel with that. Finally R23, is connected to the common (VB). While the trace connected to the – or inverting input of an op-amp is considered a "virtual earth" connection, in reality it has a high input impedance determined by the values of the gain setting resistors (R23 and R28( and can be as susceptible to RF pickup as any other trace.

Similarly the trace connected to the + or non-inverting pin must also be short as possible. The bypass capacitor to ground (C42) may not be there in all cases but if it is used, it must be as close to the input pin as possible. As

#### FEEDBACK COMPONENTS

The feedback components in this case are C25 and R28. These must be as close to the op-amp as possible. In most audio it does not matter whether the resistor or capacitor is closer to the op-amp. However in circuits with noise generators like RF circuits, oscillators, etc, many engineers feel the capacitor should be next to the op-amp.

well the input bias resistor (R24) must also be as close as possible to the input to reduce the impedance of the trace as close to the op-amp as possible. The resistor R32 in conjunction with C42 forms a low pass filter. The connection between this resistor and the capacitor must be as short as possible. If the connection to the op-amp has to come from a long distance, then that long trace would be on either side of C20. R32 serves a secondary function where if the previous stage is an op-amp, and R32 was zero ohms, the capacitor C42 may make that op-amp oscillate. Having R32 causes the frequency pole created by C42 to change to a point where the preceding stage will not oscillate. In cases where the signal through C20 comes from an input jack R32 acts to limit the possibility of static discharge damage to the op-amp.

Also note on the graphic how the power goes to the capacitor then to Pin 8, the power pin of the IC.

#### Clock Lines

In circuits with digital to analog or analog to digital converters and CODECs there are several critical traces.

MCLK SCLK (aka BICK) LRCK (aka LRCLK or Word Clock) SDIN (aka SDATA) SDOUT (aka SDATA)

Only units with CODECs will use both SD traces. These traces carry digital signals up to 24.576 MHz. The signals have leading and/or trailing edges that must arrive at the converter/CODEC at the same time within about 5 nano seconds. That is 1/200<sup>th</sup> of 1 millionth of a second.

These traces must be of the same length as much as possible within a centimeter or so. They should also run parallel with each other as much as possible and have the same number of vias. And as few vias as possible.

The trace length function in the CAD software should be used to make sure these are as close to each other in length as possible. As well, the longer the overall length of these, the more critical that length matching becomes. A "long" length would be over 125mm or 5 inches.

As well in AES receivers, Ethernet lines, USB data lines or other digital lines with balanced signals it is also important to keep those running side by side and to have the same length as much as possible.

#### Component Spacing

#### **External Parts**

Consistent spacing of external components is important to achieve a consistent look. External parts are defined as those that require coordination with the external housing. Usually mounting holes in the case and seen by the user. However they also include mounting pads. The final determination for the placement of these parts is determined by the designer of the external enclosure in consultation with the design engineer. However the engineer can determine the required sequence of the external components in consultation with the requirements of marketing.

All the dimensions listed are in mils. 1 mil = 0.001 inch = .0394mm. The spacings given are center to center on all components. If wider spacings are used, they must be consistent on a product.

Push Switch to Push Switch = 350

Push Switch to 16mm Size Pot = 550.

16mm Pot to ¼" jack = 750

16mmPot to 16mm Pot = 700

½" jack to ¼" jack = 900 to 1000. 800 can be tolerated but would mean that the larger plugs may not be able to be used.

¼" Jack to XLR connector = 1000

Push Switch to XLR = 675

XLR Power Jack (4 or 5 pin) to ¼" jack = 875

LEDs mounted 90 degrees under a push switch are normally mounted at the same position as the push switch.

Depth behind board edge

Push Switch = 555 or 590. The lower dimension is where a button goes through the panel. The larger dimension is where the switch is recessed and there is no button.

¼" Jack = 355

LED – Mounted 90 degrees = 100

Tab Route for LED = -15

#### Libraries

Lib List"

The common library is in the Engineering folder on the server at the writer's company. The writer has the engineering directory on the server mapped as drive "E:\". Thus the common corporate library is at E:\PADs\Libraries\

The library used for corporate parts is the one called "usr". Yet it should have had the company name but once everyone's computers were set up to "usr" it was too much work to change it. The library manager may be used to make this your default directory. Open it by opening the File menu and selecting Library. Select "Manage

| ibrary                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                           |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| : MentorGraph<br>MentorGraph<br>MentorGraph<br>MentorGraph<br>MentorGraph<br>MentorGraph | s-buar<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD_HOME\Libraries\<br>tes:\PADSVX_2\SDD\Libraries\<br>tes:\PADSVX_2\SDD\Libraries\<br>tes:\PADSVX_2\SDD\Libraries\<br>tes:\PADSVX_2\SD\Libraries\<br>tes:\PADSVX_2\SD\Libraries\<br>tes:\PADSVX_2\SD\Libraries\<br>tes:\PADSVX_2\SD\Libraries\<br>tes:\PADSVX_ | anlogdev<br>common<br>connect<br>intel<br>misc<br>motoric |

| Add                                                                                      | Shared  Alow Search Remove Up with PADS Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Down                                                      |

Use the Add command to fins the "usr" library on the server. Then use the Up button to move it to the top position making it the default position.

The library manager also allows one to easily scan libraries looking for specific parts. As well, if one creates a part and feel they have made an error with it, the Library manager is the only way to remove an unwanted part. One can select either Decals or Parts and use the dialog box right under there to enter wild card parameters to limit the number of items selected.

Most parts have a prefix to the part number so that like parts are grouped with like. After that will be the part type or value then voltage if relevant and sometimes the case type.

- Type PREFIX

- Transistors QNPN or QPNP in most cases. However sometimes users have created these under the actual part numbers as well.

- FETS QFET, Q-NFET, NFET

- Capacitors CRE, CSE. CRC, CSC or CRM. R meaning radial and S meaning SMT. E

= Electrolytic, the second C = Ceramic and M = Metal Film or Film. CAC is an axial ceramic capacitor. After the value will be the voltage and the case size or lead spacing.

- ICs N- in most cases. They may also be suffixed by the case style. However at times some users have created ICs without using the prefix "N-".

- Resistors RSM or RM. RM meaning radial metal film and RSM meaning SMT. 1% metal film parts are the preferred type. Carbon film resistors are RF types for carbon film and for wire wound are RW

- Resistors, Vertical Mount RVM

- Potentiometers RPT.

- Trim Pots RTRIM, VRES or VR

- Switches S or SW

- Blocks for block diagrams BLOCK

- Connectors and Jacks J, CON, HEADER or SIP

- XLR Connectors J or XLR

- Diodes D or DIODE

- Zener Diodes D or DZ

- Bridge rectifiers BRIDGE or D

- Fuse F or FUSE

- Ferrite Bead FB

- Mounting Hole MT or MTH

- Pad PAD

- Fiducial Fiducial

- Inductors IND

- LEDs LED

- Opto Couplers OPTO

- Relays RLY

- Transformers XFMR

- Crystals XTAL

When parts are created this graphic shows the most commonly used fields in the Attributes tab of the Parts Information box.

| Attribute                   | Value                              |

|-----------------------------|------------------------------------|

| Castonguay                  |                                    |

| Description                 | N-CHANNEL, JFET, SOT23             |

| Geometry.Height             | 49                                 |

| ead Spacing                 |                                    |

| lanufacturer #1             | Fairchild Semiconductor or equal   |

| lanufacturer #1 Part Number | MMBFJ112 or equal                  |

| Reference Cost              |                                    |

| lize                        |                                    |

| /Hole/SMT                   | SMT                                |

| /alue                       | J112                               |

| /endor #1                   | Digikey                            |

| /endor #1 Part Number       | MMBFJ112CT-ND                      |

| Edit Add                    | Delete Copy Paste Browse Lib. Attr |

Geometry.Height is usually in mils.

In the PCB decals tab make sure one and only one decal is assigned. If there are more than one in the Assigned Decals box errors will happen.

| SOT-23-2N7000                                                                                                                                  | s Connector Pin Ma                 | apping                                       | Reset                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------|--------------------------|

| Library:                                                                                                                                       | ds\Libraries\usr                   |                                              |                          |

|                                                                                                                                                | Filter:<br>sot*                    | Pin Count:<br>3<br>als with pin numbers mate | Apply<br>shing Part Type |

| Unassigned Decals:<br>SOT-23-2N7000<br>SOT-23-NMBD914<br>SOT-23-MMBD914A<br>SOT-23A<br>SOT23<br>SOT23-DUAL_CA_DIODE<br>SOT23-J113<br>SOT23-NPN | Assign<br>Assign >><br><< Unassign | ned Decals:<br>23                            | Assign New<br>Up<br>Down |

| Check Part                                                                                                                                     | ОК                                 | Cancel                                       | Help                     |

Double check that all pins are correct in your PCB decal. SOT23, LED decals and 8 Pin IC decals have sometimes had issues due to some bad decals in the libraries supplied by Mentor Graphics. If a part is imported from a different library this has been an issue in the past.

Never export parts from a schematic to be saved in the library to overwrite an existing part unless you are really, really sure the part in the library already has issues.

#### Text

For decal text, the line width is always 0.1 or less than the text size. That is, if the character size is 100 mils, the line width should be 10. If the line width is greater than 10% of the height, the characters may be blurry. In the cleanup process, check the board carefully to see than none of the characters look "fat" (like graffiti letters). Recommended reference designator height on 0805 and smaller parts would be 50 mils (1.27mm) height and 5 mils (0.127mm) line width. Otherwise 66, 70 and 100 mils character heights are commonly used.