# MAXIMIZE POWER AND EFFICIENCY WITH PADS® PLACEMENT AND ROUTING

JIM MARTENS, MENTOR GRAPHICS

www.mentor.com/pads

## INTRODUCTION

Printed Circuit Board design is a complex process. The most time-consuming tasks are placing parts on the board and routing traces. How effectively you're able to accomplish this will have a direct impact on design quality and the time required to complete the design.

# **PLACEMENT**

Good PCB designs come from good planning, and good planning begins with good parts placement. Placement that is well thought out for board layout

will result in better overall design processes, including better signal integrity and less-expensive manufacturing. Let's examine the benefits that can be derived from good placement.

Good placement leads to the improved routing of traces. Good routing produces shorter traces and requires fewer layers and fewer vias to interconnect the board, all of which reduces the cost of the product. Shorter traces also result in better electrical performance with fewer signal integrity problems.

| Graphics                                  | Research by 🐨 TechValidate                                                                                                                                             |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PADS Helps v<br>Reuse                     | vith Component Placement &                                                                                                                                             |

| symbol and pcb for<br>stitching and reuse | out PADS is the link between the schematic<br>otprint during component placement. Then, the<br>functions are very convenient. The copper pour<br>y good function too." |

| with phonty is a very                     |                                                                                                                                                                        |

|                                           | Engineer, S&P 500 Electronics Company                                                                                                                                  |

For example, if two parts are placed four inches apart but a critical connection between them needs to be two inches or less, this constraint can never be met. Also, with today's high data rates for DDR, SATA, SERDES, and other technologies, the parasitic effects of vias can have a serious effect on the signal integrity of a trace. Eliminating — or at least minimizing — vias on these traces is critical. Placement also has a direct effect on manufacturing. If components are placed too close to each other, will automatic insertion machines have enough room to assemble the board?

### SCHEMATIC DRIVEN PLACEMENT

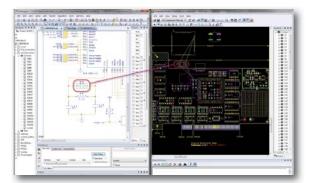

To aid designers during the placement process, PADS includes many features that lead to faster and more efficient placement. To begin with, schematics are created in a logical manner. Often, components that are placed close to each other on the schematic will need to be placed close to each other in the layout. PADS allows cross probing from both the schematic and the layout while placing parts (Figure 1).

Selecting a group of parts on the schematic simultaneously selects the parts in the layout, enabling the designer to place parts, one by one, close to each other using the 'Move Sequential' command. By using this command, each part is automatically attached to the cursor in sequence, until all selected parts are placed, shortening placement time while improving product quality.

Figure 1: Bi-directional cross probing between schematic and layout during placement allows for better parts arrangement in shorter time.

#### UNION

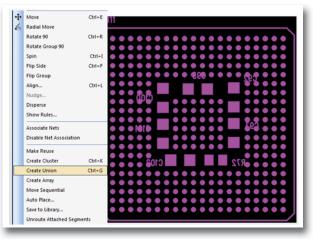

PADS uses the 'Unions' function to associate multiple components after they are placed. For example, let's say you have a large BGA with many bypass capacitors. Placing bypass capacitors correctly takes thought and time. What happens if you have to move that BGA? You don't want to have to do the work all over again. With PADS, you can create a Union of the BGA and capacitors, as shown in Figure 2, that lets you select and move all the components as if they were a single component — this can save a lot of time!

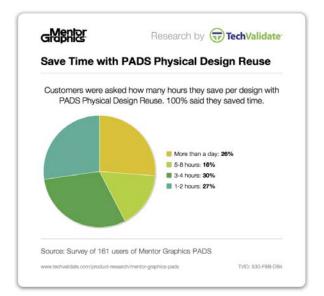

## PHYSICAL DESIGN REUSE

PADS Physical Design Reuse (PDR), included in the PADS ES suite, is extremely effective for placing components and reducing design time. There are several ways this function can be used.

One use model is to create a "golden circuit." Say you are designing the first board in a new series of part

Figure 2: Creating a Union of a BGA package with capacitor and resistor components makes it easy to move them together, as a single component.

numbers that your company is introducing. Wouldn't it be great if you could reuse a section of circuitry, such as the power supply, on all the boards? You could place it, even route it, and then save it off into a library. When you design the next board, just pull the golden circuit from the library and place it in the new design. It is already placed and routed!

A more-common use model is in multi-channel designs. Place the first channel and route it. Create a reuse element

and replicate it in seconds. Do it as many times as you need to, whether that's for two channels, eight, sixteen, or whatever, the time savings continue to multiply (Figure 3). In fact, customers who work with 128-channel designs have indicated that what used to take them two days now takes only two hours!

Figure 3: With Physical Design Reuse, multiple channels are replicated by intelligent placement

PDR isn't just copy and paste; it's an intelligent algorithm that selects the correct component for each replicated reuse, so you can be ensured the right part is being used.

## **RADIAL PLACEMENT**

Radial placement for circular boards is fully supported in PADS. Complete radial parameters can be controlled using Radial Move Setup, as shown in Figure 4. You can save significant time by being able to place components on a round board, using polar placement to automatically calculate location and spacing requirements.

## **INTERACTIVE ROUTING**

Interactive routing is a critical part of the design process, one that can be very challenging and time consuming given the complexity and density of today's designs. So it is critical to have effective, intelligent interactive routing that also guides the designer, respecting all constraints and creating the correct trace geometry from the very beginning.

There is no "one best way" to route a design. There are many variables and individual preferences that have to be taken into account. PADS doesn't force you to adopt one methodology. Instead, it is very flexible, allowing you to choose how you want to drive the routing. Let's look closely at some of the challenges that have to be addressed by interactive routing.

First, interactive routing has to be easy to use. It has to be flexible, ease-to-learn, and customizable. These attributes allow you, the designer, to focus on the overall routing plan and reveal your creativity during the process.

Second, on a dense board the routing channels can get blocked quickly, leaving no space for additional routing. Interactive routing needs to be capable of resolving

Figure 4: Radial Move Setup is intuitive and a good aid in placing round boards.

*Figure 5: Interactive routing of a differential pair with accordion (zigzag) pattern for length control.*

clearance conflicts when trying to route additional traces between ones that are already routed. PADS interactive routing pushes traces and vias out of the way based on design rules. This approach can clear additional routing channels to accommodate new routes that you're working on. Without these features, designs often require multiple rerouting cycles, or additional routing layers, to find the required space and achieve completion.

For good interactive routing you also need a breadth and depth of features to maximize efficiency. Examples include point-and-click control of manually or automatically created geometries that follow cursor moves, customizable routing angles, and layer and via type changes. PADS also lets you follow particular borders, choose appropriate conflict resolution modes, etc. Having a comprehensive arsenal of such capabilities will greatly help with effective routing.

PADS design rule checking (DRC) adheres to all constraints, thus ensuring that no rule is violated and that you won't

have to fix issues afterwards. Equally important is to have well-created trace geometry so that, after interactive routing, your design will be ready for manufacturing immediately, without any need for final tweaking.

Finally, a special emphasis should be made on high-speed nets, differential pairs, and matched-length groups with the ability to add accordion patterns, shown in Figure 5, to comply with length rules. It is critical to route them right. PADS interactive routing handles such nets easily, enabling you to meet all required high-speed constraints.

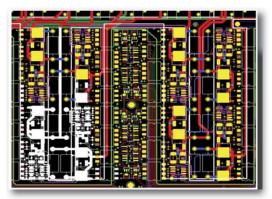

# **AUTOROUTING**

PADS autorouting meets the needs of the power user, while keeping the beginner in mind. It's easy to set up and the user interface is designed for ease of use and efficiency. Sophisticated intelligence for high-speed applications, such as differential pair routing, includes unique rule assignments and automatic tuning of groups of nets to meet min/max length and matched-length constraints. With PADS autorouting you get to control and streamline the complex process of trace autorouting.

PADS autorouting obeys all design rules for pad entry and fanouts based on the type of parts used. This ensures that the signal integrity, power integrity, and manufacturability requirements for the design are accomplished. Additionally, intuitive graphical monitoring tools provide real-time feedback for correct-by-construction methodology.

As demonstrated in Figures 6 and 7, proven routing algorithms enable robust design rules and advanced design constraints to be applied between objects or groups of objects such as components, layers, nets, and vias.

Figure 6: Autorouting of differential pairs with length control employing accordion pattern.

*Figure 7: Autorouting of matched-length groups with length control employing accordion pattern.*

#### VERIFICATION

Verification should always be part of the designer's strategy when autorouting. Pre-route analysis ensures use of the optimum rules strategy before autorouting begins, while post-route verification maximizes manufacturing yields.

Advanced features in PADS autorouting follow Design for Test (DFT) and Design for Manufacturing (DFM) requirements. An example is the DFT routine that can perform automatic test-point insertion as part of the normal routing pass, ensuring optimum test point placement. Autorouting with DFT rules can be set for the correct test point size and clearances to determine spacing between test points and components.

Verification will indicate if any nets are missing a test point, thus allowing you to insert them manually and re-verify whether DFT rules were followed.

PADS helps PCB designers play an early role in validating the routing of a design by considering key aspects of fabrication and assembly that have a direct impact on a design's manufacturability.

#### ROUTING STRATEGIES

Setting up the routing strategy to control autorouting processes like fanout and routing is easy in PADS, as you can see in Figure 8. The routing sequence can be set to start with high-speed nets and/or high-density components, followed by all remaining nets. The routing strategy follows steps similar to a manual routing approach.

These controls allow PADS autorouting to achieve high completion rates that result in shorter design cycles and quicker time to market.

| Pass Type                      | Pass     | Protect | Pause      | Intensity         | 2                        |                                                     | Routing Order                                                                                                                         | Done                   |

|--------------------------------|----------|---------|------------|-------------------|--------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Fanoul                         | 1        | 12      | 10         | Medum             | US,P1,US,U100,Plane Nets |                                                     |                                                                                                                                       |                        |

| Patiente                       | 171      | 10      | 10         |                   | All Nets                 |                                                     |                                                                                                                                       |                        |

| Route                          | 12       |         | E 1        | Medum             |                          | TT2.DFT3 DFT4.D                                     | PFOUT1<->DFFOUT2.DFFOUT3<->DFFOUT4.CLOO                                                                                               | KS,MATCHTRACK,MLNetGro |

| Cylinder                       | 0.1      | 0       | -0-        | 100               | Adhista                  |                                                     | 1                                                                                                                                     | 0                      |

| Center                         | .0.1     | 13      |            |                   | AllNets                  |                                                     |                                                                                                                                       |                        |

| Test point                     | .8       | - 13    |            | Low               | AtNets                   |                                                     |                                                                                                                                       |                        |

| Tune<br>Mbers                  | 8        | 13      | E.         | Low               | All Nets<br>All Nets     |                                                     |                                                                                                                                       |                        |

| Routing order<br>Select compor | erts and |         | te to defi | ne the routing of | order for pass types.    | Defait                                              | Routing Order                                                                                                                         | × + 4                  |

| <i>i⊪ Ш</i> № С                | Xyecta   |         |            |                   |                          | Salactad 33<br>Al Neta 30<br>Plane Neta 30<br>Clear | STRIL-0-851%C DIFFL0-0851%C DIFFL0-0851%C DIFFL0-0854 DIFFL0-015-004F012 DIFFL01T-0-04F0174 CLOCKS MATOTTRACK WALkelGas-1 ANLAG Altes |                        |

Figure 8: Routing strategy controls the order of automatic fanout and routing.

## **CONCLUSION:**

PADS powerful placement and interactive and automatic routing capabilities provide an easy-to-learn-and-use environment with excellent productivity multipliers. With PADS you can complete challenging designs faster, following all rules for signal integrity and manufacturability, and eliminate re-spins and schedule delays.

## **BEHIND PADS: MENTOR GRAPHICS**

When selecting a new EDA tool, you are not just looking for new design tools, but a partner to help you achieve your goals, and grow with you. Mentor Graphics is a \$1 billion company based in Wilsonville, OR that has been helping companies be successful designing electronic products since 1983. Mentor Graphics has solutions in many design spaces, from IC and FPGA, to embedded software, to PCB design.

Mentor has a proven track record in technology investment that has resulted in market share leadership in many areas, including PCB design with more than a 50% market share worldwide.

The partnership truly begins once you buy PADS, and access Mentor's SupportNet. On SupportNet, you have 24/7 access to the information you need, when you need it.

Ask questions and troubleshoot problems in the industry's largest online knowledge base. Download full product and update releases to make sure you are using the most up-to-date software on your design projects. Find product documentation, application notes, tutorials and how-to videos to help you learn how to use existing, and new features.

Mentor's Customer Support is more than its online resources. We have won the prestigious industry STAR award 5 times. We have a global presence of AE's experienced not only in PADS — but in PCB design as well.

You can also take advantage of the large, loyal global user base of PADS once you partner with Mentor Graphics.

In Mentor's online Ideas site, users can post their Ideas, or enhancement requests. Other users can view these and vote for or against them. To date, PADS has implemented over 100 customer submitted Ideas.

### For the latest information, call us or visit: w w w . m e n t o r . c o m / p a d s

©2013 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.

Corporate Headquarters Mentor Graphics Corporation 8005 SW Boeckman Road Wilsonville, OR 97070-7777 Phone: 503.685.7000 Fax: 503.685.1204

Sales and Product Information Phone: 800.547.3000 sales info@mentor.com Silicon Valley Mentor Graphics Corporation 46871 Bayside Parkway Fremont, CA 94538 USA Phone: 510.354.7400 Fax: 510.354.7467 North American Support Center

Phone: 800.547.4303

Europe Mentor Graphics Deutschland GmbH Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.00 Fax: +49.89.57096.400 Pacific Rim Mentor Graphics (Taiwan) Room 1001, 10F International Trade Building No. 333, Section 1, Keelung Road Taipei, Taiwan, ROC Phone: 886.2.87252000 Fax: 886.2.27576027 Japan Mentor Graphics Japan Co., Ltd. Gotenyama Garden 7-35, Kita-Shinagawa 4-chome Shinagawa-Ku, Tokyo 140-0001 Japan Phone: +81.3.5488.3003 Fax: +81.3.5488.3004

LVG 10-13 TECH11460-w