### Set 19: Monostable circuits

Monostable circuits, often referred to as multivibrators. can take various forms. The term multivibrator seems to have been used for Abraham and Blochs astable two-triode circuit of 1918, and the related bistable Eccles-Jordan circuit of 1919. Flip-flop or monostable circuits were developed a few years later, for example the 1926 transitron of van der Pol. Many of the early circuits used two timing capacitors, being derived from the a.c.-coupled multivibrator, but all of the monostables described in this set of cards use one timing capacitor. The most well-known arrangement (card 1) can be thought of as derived from the crosscoupled bistable circuit, with one resistive coupling replaced by the timing capacitor. Recovery time is often too long with this straightforward circuit. Cards 1 & 2 show a complementary arrangement that has short recovery time  $(RC|\beta)$ , but a possible disadvantage is that both transistors conduct in the quiescent state. Other methods are shown in the article, e.g. use of a diverting diode to prevent saturation (Fig. 3), addition of an emitter follower as shown in Fig. 4, and a circuit in which the on and off transistors are transposed, Fig. 6 (see also card 10). Emitter-coupled circuits, card 6, have the advantage of isolating the output point from the remainder of the circuit. As with the astable circuits of set 8 this collection includes t.t.l. circuits (card 4), op-amp circuits' (card 3) and circuits using c.m.o.s. devices (cards 5 & 8). Long delay circuits use the D-type flip-flop or unijunction transistors (card 8) and improved duty cycle is obtained with the circuits of card 10. A voltage-variable delay is

provided by the circuits of card 7 of around 7 to  $90\mu$ s

Basic discrete-component circuits 1 Complementary circuits 2 Op-amp/comparator circuits 3 Monostable using t.t.l. gates 4 Compensated c.m.o.s. circuits 5 Emitter-coupled circuits 6 Voltage-controlled monostables 7 Long-delay circuits using c.m.o.s. and unijunction devices 8 Dual monstable applications using 555 timer 9 High duty-cycle monostable 10

and 40 to 200ms.

# The monostable . . . doth give us pause

Not quite the words of Hamlet, but delay is one outstanding property of the monostable circuit. De Bono, in The Mechanism of Mind, could be describing another function of the circuit when he writes, "a short-term memory is just a way of extending the influence of an event beyond the real time of its occurrence along the dimension of time", e.g. a monostable will accept a transition at its input and respond with an output pulse, but for a finite time. A more formal description of the monostable (sometimes called a one-shot) is a circuit having one stable state in which it remains until triggered by an external signal into a quasi-stable state, where it remains for a time determined by circuit parameters and subsequently returns to its stable state. This basic action allows the monostable to be used for a variety of purposes such as lengthening, delaying and regenerating pulses, sequential timing and delay applications and frequency division.

The nature of the monostable circuits can be widely different because they can be designed using n-p-n and p-n-p bipolar transistors (in cross-coupled emittercoupled and complementary modes), fieldeffect transistors, operational amplifiers, discrete and integrated-circuit logic gates, as well as purpose-designed monostable integrated circuits.

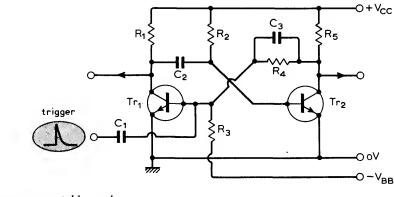

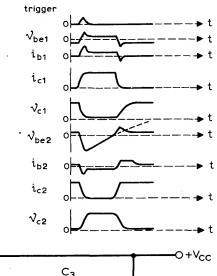

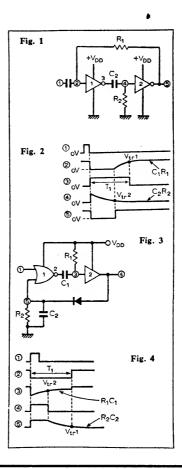

A very common type of monostable uses a cross-coupled configuration which can be thought of as being a modification of a symmetrical bistable where one resistive coupling is replaced by a capacitive coupling. Two possibilities are available; the timing capacitor can either be connected between the collector of a normally-off transistor to the base of a normally-on transistor, or between the collector of a normally-on transistor and the base of a normally-off transistor. Fig. 1 shows a circuit of the first type and Fig. 2 the associated current and voltage waveforms.

Transistor  $Tr_2$  is in a stable on state, until triggered, due to the base drive supplied through  $R_2$ . Transistor  $Tr_1$  is held in a stable off state as  $R_4$  is connected to  $Tr_2$ collector which is at the low saturation value of  $v_{ce2}$  and  $R_3$  is returned to the negative  $V_{BB}$  rail. When a positive-going trigger pulse is applied to  $Tr_1$  base via  $C_1$  this transistor turns on causing its collector voltage to fall to almost zero.

Because the charge on  $C_2$  cannot change instantaneously, this negative-going transition is passed to  $Tr_2$  base which switches off. The transistors remain in these states while the charge on  $C_2$  changes via  $R_2$  causing  $v_{be2}$  to rise exponentially towards  $+ V_{CC}$ . When  $v_{be2}$  passes through zero and rises positively to a value depending on the type of transistor used, which causes base current to flow in  $Tr_2$ , this transistor begins

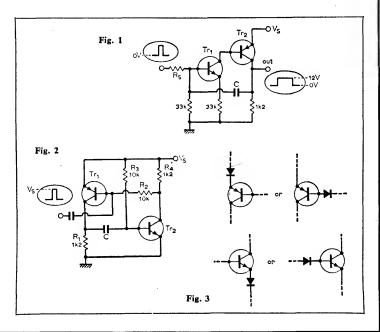

Fig. 1. A common monostable can be thought of as a bistable circuit with one resistive coupling replaced by a capacitative coupling. Two can be connected as shown.

Fig. 2. Waveforms associated with circuit of Fig. 1.

Fig. 3. Switching speed of Fig. 1 circuit is improved by preventing saturation with diodes  $D_1$  and  $D_2$ . Clamping diode  $D_3$ reduces recovery time by connection to a supply less than  $V_{cc}$ .

to turn on. The resulting fall in  $v_{c_2}$  is coupled to  $Tr_i$  base via  $C_3$ ,  $Tr_i$  beginning to turn off; the regenerative feedback via  $C_2$  and  $C_3$  causes the circuit to return to its stable state of  $Tr_i$  off and  $Tr_2$  on, the capacitor  $C_2$  recharging through  $R_i$ .

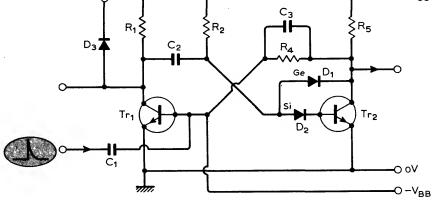

The switching speed of this kind of circuit can be improved by using higher speed switching transistors in a non-saturating circuit. To prevent saturation, germanium diode  $D_1$  and silicon diode  $D_2$  can be added as shown in Fig. 3. When  $Tr_2$  begins to turn on, to return the circuit to its stable state,  $D_1$  will be reverse-biased until  $v_{c2}$  falls below  $(v_{be2} + v_{D2})$  causing the excessive base drive current, which would otherwise saturate  $Tr_2$ , to be diverted through  $D_1$ . Two series-connected germanium diodes can be used in place of the silicon diode  $D_2$ The waveform at  $Tr_1$  collector can have a slow recovery time, especially when driving capacitive loads, and this can be reduced by the addition of the clamping diode  $D_3$ returned to a supply  $V_A < V_{CC}$ . The output voltage  $v_{CI}$  attempts to rise towards a higher value with  $D_3$  present but becomes clamped at  $(V_A + V_{D3})$  when  $D_3$  conducts.

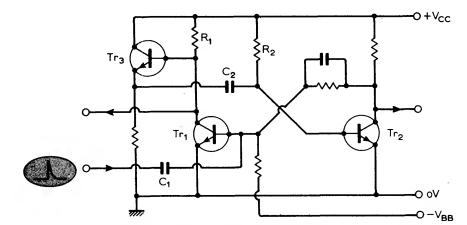

Another method of reducing the recovery time is to include an emitter follower between  $R_1$  and  $C_2$  of Fig. 1, as shown in Fig. 4. As  $C_2$  is charged to almost the supply rail voltage, the emitter of  $Tr_3$  is normally close to  $+V_{CC}$ . The input trigger pulse switches the circuit to its quasi-stable state and as the charge on  $C_2$  changes, the emitter voltage of  $Tr_3$  rises above its base yoltage ( $v_{CI}$  on) cutting the transistor off. When  $Tr_2$  again begins to conduct, the circuit returns to its stable state with  $C_2$  being rapidly recharged by the emitter current of  $Tr_3$ .

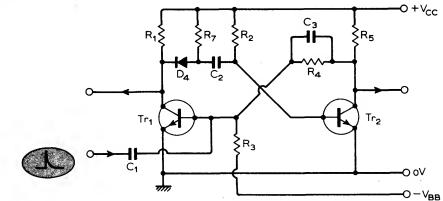

The output from  $Tr_i$  collector can be made to more closely approach a rectangular pulse by the inclusion of an isolation diode  $D_4$  as shown in Fig. 5. When  $Tr_1$  is on the collector current flows through  $R_1$  and  $R_7$  in parallel and a faster recovery time is achieved by making  $R_7 < R_1$  so that when  $Tr_1$  switches off  $D_4$  is reverse biased and  $C_2$  recharges more rapidly, through  $R_7$ , than in the circuit shown in Fig. 1. Other methods of triggering this type of monostable include negative pulses to either  $Tr_{i}$ collector or  $Tr_2$  base or positive pulses to the base of another transistor having its collector and emitter respectively connected to  $Tr_1$  collector and emitter.

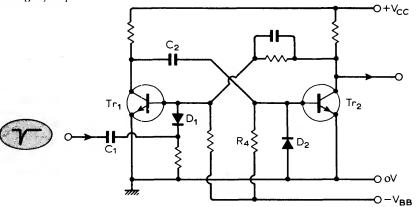

Another form of the cross-coupled monostable is shown in Fig. 6, the major difference compared with the foregoing circuits being that  $Tr_1$  is on and  $Tr_2$  is off in the stable state. This is achieved by correct choice of the potential-dividing chain and by  $D_2$  being forward-biased via  $R_4$ , holding the base-emitter junction of  $Tr_2$ reverse-biased. A negative-going input trigger pulse causes  $Tr_i$  to switch off and hence  $Tr_2$  to switch on and to remain in that state as  $C_2$  charges, part of the charging current being base drive to  $Tr_2$ . Diode  $D_2$  is reverse-biased in this quasi-stable state which ends when the base drive to  $Tr_2$ has fallen to a level which will not maintain conduction. Transistor Tr<sub>2</sub> then switches off causing  $Tr_i$  to return to the stable on state.

Fig. 4. Recovery time can also be reduced with an emitter follower between  $R_1$  and  $C_2$  of Fig. 1.

Fig. 5. Output from  $Tr_1$  is made more rectangular by isolation diode  $D_4$  and by making  $R_7 < R_1$ .

Fig. 6. In this variant of the cross-coupled monostable,  $Tr_1$  is normally on and  $Tr_2$  normally off. Note trigger is of opposite polarity. Circuit has much faster recovery time.

No output is taken from  $Tr_1$  collector as a load at that point significantly changes the off time of  $Tr_2$ . This circuit has a much faster recovery time than the previous ones discussed.

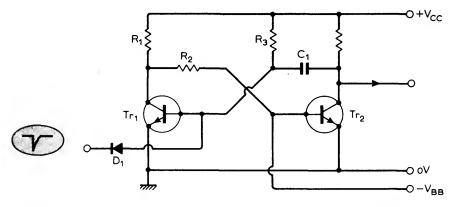

A cross-coupled monostable which besides producing a time-constant-dependent output pulse may provide one due to the input pulse duration is shown in Fig. 7. In the stable state  $Tr_1$  is on and  $Tr_2$  is off, so when a short-duration trigger pulse is applied via  $D_1$  the circuit remains in its quasi-stable state for a time determined largely by  $C_1R_3$ . However, when a long input pulse is applied,  $Tr_1$  will remain off until the input is removed even if  $C_1$  completes its discharge during that interval.

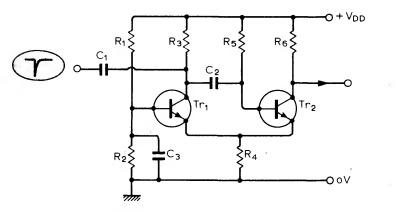

Fig. 8 shows an emitter-coupled monostable where  $Tr_2$  is on and  $Tr_1$  is off in the stable state. Compared with the cross-

coupled circuits, this type has the advantages of only using a single supply and providing an output which is taken from a point having no internal coupling. When a negative-going trigger pulse is applied to  $Tr_1$  collector via  $C_1$  it is coupled to the base of  $Tr_2$ , which switches off. The emitter voltage falls allowing  $Tr_i$  to switch on for a time determined by that required for  $C_2$  to discharge sufficiently to allow  $Tr_2$ to begin to conduct. The emitter voltage then rises, causing  $Tr_1$  to begin to switch off, and the resulting rise in  $Tr_1$  collector voltage is coupled to  $Tr_2$  base which switches on, and  $Tr_{j}$  switches off to regain the stable state. Due to the presence of  $R_4$ , the output voltage swing does not approach  $V_{cc}$  and the recovery time is not very fast, as  $R_3$  should be greater than  $R_6$  to ensure the correct switching action.

Fig. 7. This circuit produces an output pulse dependent on input pulse duration.

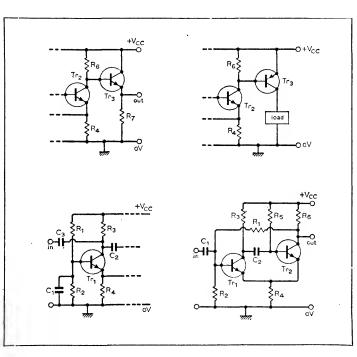

Complementary transistors enable both transistors to be normally off (Fig. 9, above) or normally on (Fig. 10, right). Opposite-polarity outputs are available from Fig. 10.

Recovery time can be improved by the addition of an emitter follower as was done in Fig. 4.

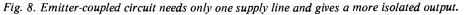

A monostable using a complementary pair of transistors, having both transistors off in the stable state, is shown in Fig. 9. A negative-going trigger pulse applied to Tr, base causes this p-n-p transistor to switch on, its collector current in  $R_1$  and  $R_2$  causing the base of  $Tr_2$  to go positive causing this n-p-n transistor to switch on also. The resulting collector current in  $R_4$  causes the output voltage to go negative and this change is coupled to  $Tr_i$  base through  $C_1$  causing  $Tr_1$  and hence  $Tr_2$  to be switched hard on. In this quasi-stable state  $C_1$  charges through  $R_3$  and  $Tr_2$  towards  $-V_{EE}$  and when the charging current is insufficient to maintain conduction

in  $Tr_1$  this transistor switches off, as does  $Tr_2$  and the circuit returns to its stable state.

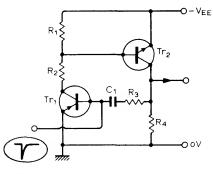

Fig. 10 shows a complementary monostable in which both transistors are on in the stable state, and which provides a pair of opposite-polarity outputs simultaneously. A positive-going trigger pulse applied to  $Tr_2$  base turns both transistors off and after  $C_1$  charges sufficiently, through  $R_2$ and  $R_4$ , both transistors return to the stable on state regeneratively.

### **Basic discrete-component circuits**

#### **Circuit description**

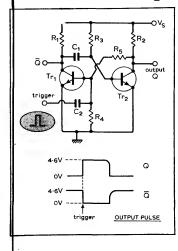

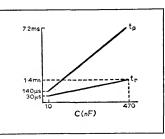

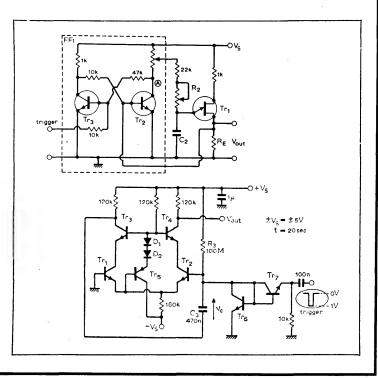

In the quiescent state with the trigger at 0V, Tr<sub>2</sub> is held on due to base drive via R<sub>3</sub>. Point **b** is therefore at zero volts and hence  $Tr_1$  is off, its base being at OV. In receipt of the trigger bulse the base of  $Tr_1$  is forced positive,  $Tr_1$  conducts and its collector voltage drops. This is ransmitted via  $C_1$  to the base of Tr<sub>2</sub> and hence Tr<sub>2</sub> is forced off, raising its collector voltage. By potential division via  $R_5$  and  $\mathbf{R}_4$ , the base of  $\mathbf{Tr}_1$  is forced positive, thus forcing Tr<sub>1</sub> urther into conduction. This ositive feedback action forces a rapid change in state of both  $Tr_1$  and  $Tr_2$ .  $C_1$  then has one side at 0V, point Q, and the other side connected via R<sub>3</sub> to V<sub>s</sub>. It thus commences to charge towards V<sub>s</sub>. This continues until the potential at the base of Tr<sub>2</sub> reaches a value which causes Tr<sub>2</sub> to start conducting. Point Q then starts to fall in potential causing the base of  $Tr_1$  to fall. This causes  $\bar{\mathbf{Q}}$  to rise, forcing the base of Tr<sub>2</sub> even higher and rapidly the two transistors change back to the quiescent state. Length of the output pulse depends on C<sub>1</sub>R<sub>3</sub>. See graph. The original quiescent state is

not reached until  $C_1$  has returned to its original uncharged state. The discharge path is via  $R_1$  and the base-emitter junction of  $Tr_2$ . Discharge time is what accounts for the recovery time,  $t_r$  minus the minimum time after the output pulse trailing edge at  $Tr_{1}, Tr_{2}: BC125 R_{1}, R_{2}: 1k\Omega R_{3}: 22k\Omega R_{4}: 4.7k\Omega R_{5}: 10k\Omega C_{2}: 100pF V_{8}: 5V$

Typical performance

Min. trigger pulse width  $0.5\mu$ s Trigger pulse height in range 1.4 to 3.6V

Output pulse width  $t_p$  depends on  $C_1R_3$ —see graph Recovery time  $t_r$  depends on  $C_1R_1$ —see graph

Output pulse height 4.6V

which a further trigger pulse will give correct operation; see graph above.

Maximum trigger pulse height is fixed by the negative-going voltage applied to the base of  $Tr_1$  on receipt of the trailing edge of the trigger pulse. If this is greater than the bias set by  $R_4$  and  $R_5$  then  $Tr_1$  is switched off immediately and monostable action is prevented. Minimum trigger pulse height depends on  $C_2$  and on the pulse rise time.

#### **Circuit modifications**

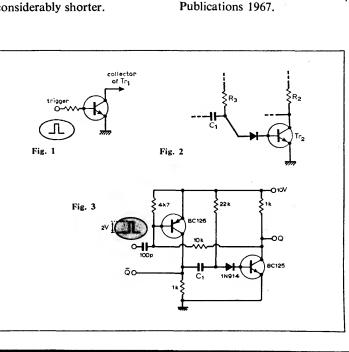

• Both of the above restrictions on the trigger pulse height may be reduced by applying the trigger pulse as shown Fig. 1. If this arrangement is used the min. pulse height should be about 0.7V and the maximum should be the breakdown voltage of the triggering transistor.

• A general-purpose diode e.g. 1N914 should be inserted in the base line of  $Tr_2$  as shown Fig. 2, if the supply voltage used is above 6V or so which is the base-emitter breakdown voltage of most planar transistors. If this is not done the linearity of  $t_p$  with respect to C is lost.

• If short recovery times are required between consecutive output pulses the circuit of Fig. 3 may be used. In the quiescent state both transistors are conducting, Q is low and  $\overline{Q}$  is high. On receipt of the trigger pulse the p-n-p transistor (BC126) is switched off causing

the base of the BC125 to fall in potential, thereby raising the voltage of Q and, via the  $10k\Omega$ resistor, the base of the BC126. The circuit thus latches into a condition where both transistors are off. Capacitor C<sub>1</sub> then charges via the 22k and  $1k\Omega$  resistors toward the supply and eventually turnsthe BC125 on and with it the BC126. Discharge of C<sub>1</sub> occurs more quickly in this case because the discharge path is through the collector-emitter junction of the BC126 and the base-emitter junction of the BC125. No external resistors are involved in this path as occurred previously. Hence, the circuit recovery time is considerably shorter.

# Set 19: Monostable circuits—1

#### Further reading SGS Fairchild. Industrial Circuit Handbook 1967. Hemingway, T. K., Electronic Designer's Handbook. Business

# Set 19: Monostable circuits—2

### **Complementary circuits**

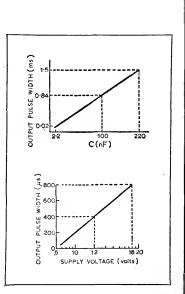

#### Typical performance Tr<sub>1</sub>: BC126, Tr<sub>2</sub>: BC125 $R_1, R_2: 33k\Omega$ $R_3$ : 1.2k $\Omega$ , $R_4$ , $R_5$ : 10k $\Omega$ **D**<sub>1</sub>: 1N914 With $V_s = 12V$ , trigger frequency 500Hz, trigger pulse width and height 10µs. and 2V respectively, graph opposite of output pulse width against C was obtained. With C = 47 nF and pulse width of $10\mu s$ , minimum trigger pulse height about 1.3V. With pulse height at 2V, minimum pulse width about $2\mu s$ . Output pulse height about 12V; maximum mark-space ratio is 10:1 at this frequency.

(Fig. 3). A diode may be inserted in the emitter lead or in the base lead. The last-mentioned is generally preferred in that it will not affect the output pulse levels.

#### References

- 1 Electronic Circuit Design Handbook, Tab. p.174.

- 2 Electronic Circuit Design Handbook, Tab. p.85.

Cross references Set 18, card 1 Set 10, card 4

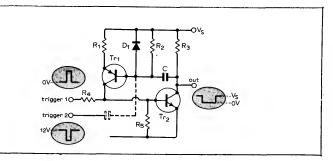

#### **Circuit description**

Monostable circuits using complementary transistors allow one to trigger either with respect to the positive supply line.

In the circuit shown both transistors are non-conducting in the quiescent state. On receipt of a positive-going pulse at trigger point 1, Tr<sub>2</sub> starts to conduct, dropping its collector voltage. This drop is transmitted via C to the base of Tr<sub>1</sub> and hence Tr<sub>1</sub> starts to conduct. This produces further base drive to  $Tr_2$  and pushes it further into conduction. Very quickly both transistors are fully conducting and the output, initially at Vs drops to 0V approximately.

Capacitor C, uncharged in the quiescent state, then begins to charge towards  $V_s$  via  $R_2$  and  $Tr_2$ . When it reaches  $V_s - V_{be}$ ,  $Tr_1$  is cut off,  $Tr_2$  is cut off and the capacitor discharges via  $D_1$  and  $R_3$  principally. Insertion of  $D_1$  provides a low resistance discharge path giving a fast recovery time.

When  $Tr_2$  is cut off the output swings back to  $V_s$  so the output pulse period is determined by the charging time of the capacitor.

With the basic monostable circuit (card 1) the capacitor is, in the quiescent state, charged in one direction and this direction is reversed when triggered. Ignoring  $V_{be}$  effects, the capacitor during charging

is going from  $+V_s$  to  $-V_s$ and the 0V or 50% point is sensed to bring the circuit back to quiescence. Because one is sensing a particular percentage of the attempted swing, the time taken is not supply voltage dependent. This is not the case here since a particular voltage is being sensed; the graph over shows the variation of pulse width with supply voltage. This could conceivably be used to produce a voltagedependent monostable action.

#### **Component changes**

Increasing the pulse height allows a reduced pulse width (trigger pulse). Reducing  $R_1$  to  $4.7k\Omega$  allows operation down to 6V and  $0.1\mu$ s trigger pulse width. Value of  $R_2$  is not critical;  $R_3$  depends on  $Tr_2$ ;  $R_4$  and  $R_5$  not critical.

#### Similar circuits

• The circuit of Fig. 1 will have zero stand-by power consumption but in this case has a positive-going output pulse. Again the output pulse width will depend on Vs, since in the quiescent state C is uncharged. In addition the V<sub>CEsat</sub> of Tr<sub>2</sub> will affect the height of the pulse which should be  $V_{\rm s} - V_{\rm CEsat}$ . The 0V level should be well defined. In the circuit over the VCEsat affects the OV level but not the peak value (ref. 1). The circuit of Fig. 2 has a pulse width given by

$t_p=0.69(R_1+R_3)C$  and a recovery time given by  $t_r=R_3C/\beta$ . As recharging current is supplied by  $Tr_1$ , this recovery time is short. Pulse width is not supply dependent but since both transistors conduct in the quiescent state the standby power is large. Two outputs are available, at the collector of both transistors. They are the complement of one another (ref. 2).

• Diodes are frequently included in monostable circuits to prevent too large a reverse voltage being applied to the base-emitter junction of a non-conducting transistor

142

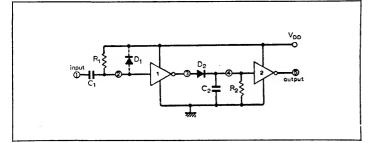

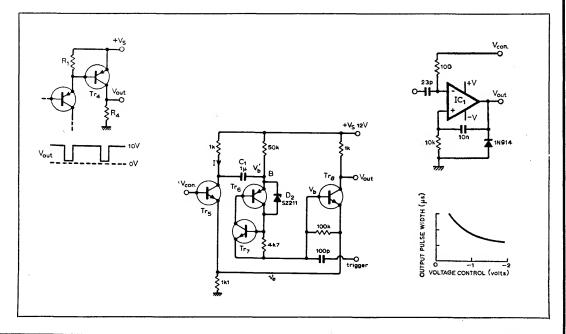

### **Op-amp/comparator circuits**

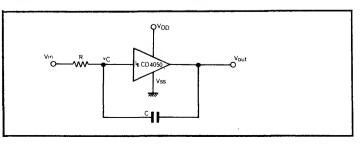

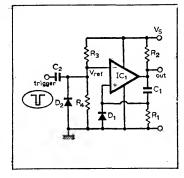

#### Circuit description

This comparator features an open-collector output, and may be used with pull-up resistor R<sub>2</sub> and a separate supply to give a wide switching range. Resistors  $R_3$  and  $R_4$  set the reference voltage equal to  $V_s/2$ , but also determine the trigger pulse level necessary for switching. Resistor R<sub>1</sub> should be much greater than R<sub>2</sub> to avoid loading the output. With  $V_{\rm ref} = V_{\rm s}/2$  and the noninverting input near 0V, the output transistor of the comparator is conducting and the output is at VCEsat. A negative trigger pulse at the input causes this transistor to switch off and hence the voltage at the output rises to almost Vs. Capacitor  $C_1$  now charges at a rate mainly determined by R<sub>1</sub> and  $C_1$ , which also control the width of the output pulse. The potential of the non-inverting input now falls exponentially from V<sub>s</sub> and the comparator switches to its original condition when the noninverting comes below  $V_{\rm s}/2$ . Diodes  $D_1$  and  $D_2$  prevent the inputs from being driven below zero volts, and  $D_1$  also provides a low impedance discharge path for  $C_1$ .

Typical performance IC<sub>1</sub>:  $\frac{1}{4}$  LM139 V<sub>s</sub>: +10V C<sub>1</sub>: 1nF C<sub>2</sub>: 470pF R<sub>1</sub>: 330k $\Omega$ R<sub>2</sub>: 10k $\Omega$ R<sub>3</sub>, R<sub>4</sub>: 1M $\Omega$ D<sub>1</sub>, D<sub>2</sub>: 1N914 Trigger pulse width: 30 $\mu$ s Trigger pulse level: 6V Output pulse width: 190 $\mu$ s Output pulse level: 9V

Component changes IC<sub>1</sub>:  $\frac{1}{4} \times MC$  3302P Useful range of C<sub>1</sub>: 220p to 22nF

Useful range of  $R_1$ : 47k to 470k $\Omega$

Minimum trigger pulse width:  $5\mu$ s

Minimum trigger pulse height:  $5V(\text{for } V_s = +10V)$ Range of V<sub>s</sub>: up to 28V. • Increasing trigger pulse

height to 8V decreases pulse width by 150 to 200µs.

Variation of pulse width with capacitance shown, for

Output pulse 5V.

Output pulse is supply dependent, see graph above.

(For C = 1nF, R = 330k O

(For  $C_1 = 1$ nF,  $R_1 = 330k\Omega$ , p.w. is  $50\mu$ s.)

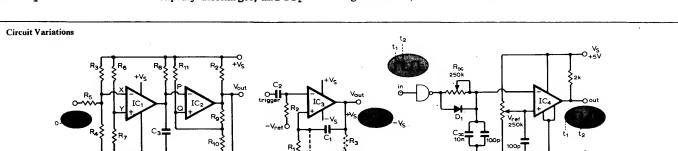

#### **Circuit variations**

• Circuit shown left gives a pulse width that is supply independent, and is capable of a high duty cycle. Capacitor  $C_3$ is initially charged to  $+V_{cc}$ and  $V_{out}$  is at almost zero volts. Potentials at X and Y are defined by associated divider chains. A positive input trigger pulse to make  $V_X > V_Y$ causes  $IC_1$  to switch (output driven low). Capacitor  $C_3$ rapidly discharges, and  $IC_2$

will switch when the voltage across  $C_3$  falls below  $V_Q$ , defined by R<sub>11</sub>, R<sub>10</sub>. Output voltage is now equal to Vee, which is fed back bia  $R_7$  to  $IC_1$ which again switches to off condition. Hence C<sub>3</sub> now charges up via R<sub>8</sub>. Output pulse width is defined by the time for the voltage across  $C_3$ to just exceed that of point Q; IC<sub>2</sub> then reverts to its on, or low-output state. IC1, IC2  $\frac{1}{4}$  LM139, R<sub>5</sub>, R<sub>4</sub> 100k $\Omega$ ,  $R_6 1M\Omega$ ,  $R_7 62k\Omega$ ,  $R_8$ ,  $R_9$ 10M $\Omega$ , R<sub>10</sub> 220k $\Omega$ , R<sub>11</sub> 560k $\Omega$ , C<sub>3</sub> 0.1nF.

Note that retriggering is not possible while IC<sub>2</sub> output is high-a useful lock-out feature. Circuit centre, using an . op-amp, has a similar action to the comparator network. A negative reference voltage on the inverting input, with the non-inverting input tied to ground, gives a stable condition where  $V_{out} = + V_s$ . A positive input trigger sufficient to cause the differential input polarity to change, the output switches to  $-V_{\rm s}$ . At this instant the potential of  $R_1$  with respect to ground is  $-2V_s$ . As C<sub>1</sub> charges, the potential across R1 rises towards  $-V_{ref}$ , when switching again occurs, and circuit resets

to initial condition. Component values:  $IC_3$ MC1530/1531,  $C_2$  23pF,  $R_2$  100 $\Omega$ ,  $C_1$  10nF,  $R_1$  10k $\Omega$ ,  $V_{ret} = 2V$ . Pulse width typically 125 $\mu$ s. Diode and  $R_3$ allow faster discharge of  $C_1$ , permitting an increase in p.r.f. • Circuit right is a useful

• Critchi right is a discriting interface for delaying logic signals. When logic level is 1, capacitor charges quickly via diode, discharges via  $R_x$  when logic level is 0, allowing V<sub>out</sub> to rise when  $V_{Cx} \rightarrow +1V$ . Using LM311, claimed delay is typically 0.04 to 370ms.

Cross reference Set 17, card 8.

V<sub>ref</sub> = + 1V

### Set 19: Monostable circuits—3

### Set 19: Monostable circuits—4

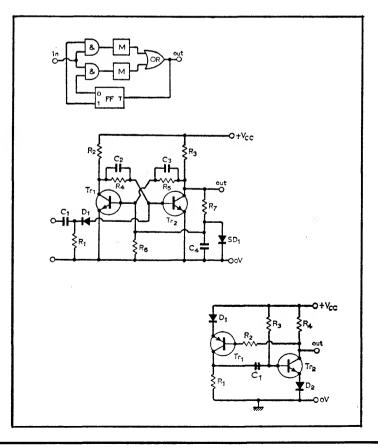

### Monostable using t.t.l. gates

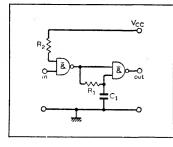

#### **Circuit description**

The circuit above uses two of the four NAND gates available in the integrated circuit package. Positive trigger pulses are applied to the first gate which is connected as an inverter, the unused input being taken to the positive supply rail (logic 1 state) via a 1-k $\Omega$  resistor to prevent the gate being damaged by a supply line transient. With the trigger input in the logic 0 state (0V), the output of the first gate is at 1, as are both the inputs to the second gate in the steady state, causing its output to be at logic 0. A positive trigger pulse causes the output of the first gate to go to its logic 0 level. One of the two inputs to the second gate immediately goes to the logic 0 level but its other input receives the voltage across  $C_1$  which cannot change its charge instantaneously. The inputs to this gate are thus at logic 0 and 1 respectively. causing its output to switch to 1 where it remains until the trigger pulse returns to the 0-volt level. During this interval, capacitor C<sub>1</sub> discharges towards 0 volt through R1 and the output impedance of the first gate and is recharged to the 1 level after the trigger pulse has returned to the 0-volt level.

#### **Circuit changes**

Useful range of  $V_{cc}$ : +4.5V to +5.5V Maximum useful R<sub>1</sub>: 470 $\Omega$ Maximum useful C<sub>1</sub>: 1.5 $\mu$ F Minimum trigger pulse amplitude: +3V

Minimum trigger pulse width:  $40\mu s$

Output pulse shape improved by cascading a third gate (see waveform and graphs above).

#### Typical performance

Logic gates:  $\frac{1}{4} \times 7400$ Supplies: +5V; 8mA R<sub>1</sub>: 100 $\Omega$ , R<sub>2</sub>: 1k $\Omega$ , C<sub>1</sub>: 1 $\mu$ F Input pulses: amplitude +5VWidth: 50 $\mu$ s, p.r.f. about 10 kHz Output pulse width about 74 $\mu$ s

Cascading the fourth gate in the package provides a pair of complementary outputs.

#### **Circuit modifications**

• The simple two-gate circuit shown in Fig. 1 has positive trigger pulses fed simultaneously to one input of each gate. These pulses appear at the output of the first gate inverted and delayed by the propagation time of the gate. Both of the inputs to the second gate are therefore at the 1 level for a short period, providing a narrow negativegoing output pulse, delayed by the propagation time of one gate. This circuit has two defects: the output pulse is very narrow and non-adjustable and the trigger pulse must be wider than the output pulse.

The circuit shown in Fig. 2 . overcomes the first defect but still requires a trigger pulse wider than the output pulse. When the trigger input is at logic 0 the output of the first gate is at 1. Inputs to the second gate are at logic 0 and 1 since C is charged from the first gate, hence the output is at 1. When the trigger pulse goes to 1 the output of the second gate switches to the 0 state for an interval determined by the time constant, as C discharges through R, and the output impedance of the first gate. When C has discharged to a level where its voltage crosses the switching threshold of the 1 to 0 transition the output from the second gate switches back to its 1 level. Trigger pulse width must still be greater than the output pulse width, as the output of the second gate will always

return to the 1 state whenever the trigger pulse returns to 0 volt.

• To overcome this problem the trigger pulses can be fed to the monstable via a third gate which has an output logic state determined by the monstable output, as shown in Fig. 3. Addition of this gate causes

the monostable to be triggered when the input transition is from the 1 to the 0 state and the width of the input pulses is only that required to cause the input and output gates to change state. Since the same time constant controls the charge and discharge rates of C both circuits have relatively low maximum duty cycles, typically around 25%.

• Circuit of Fig. 4 uses only two gates but has a very similar mode of operation, the output pulses controlling the state of the input gate. This gate will normally have a 0 output since both its inputs will be at 1 until the trigger pulse goes to 0 volt. This causes the output to switch states for a time determined by that required for the CR network to cross the logic threshold.

#### Further reading

Malmstadt, H. V. and Enke, C. G., Digital Electronics for Scientists, Banjamin 1969, pp. 213-5. Wilke, W., Operating a logic gate as a flip-flop, *Electronics*, 21 March 1974, pp.120/1. Kaniel, A., Digital delay circuit for one-shot controls timing interval in programmable integer steps, *Electronic Design*, 18 Jan. 1974, p.94.

Cross reference Set 11, card 3.

## Set 19: Monostable circuits—5

### Compensated c.m.o.s. circuits

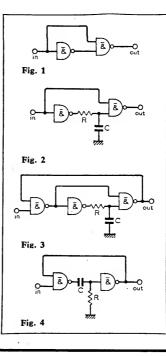

#### **Circuit description**

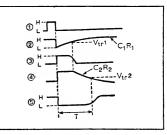

Complementary m.o.s. monostables using one time constant suffer from the fact that the transfer voltage  $(V_{tr})$ of i.cs can vary by as much as  $\pm 33\%$  so that replacement of an i.c. by another can result in a considerable change in the output pulse width. This defect can be removed by using two identical time constants with two inverters on the same chip. In this case the transfer voltage of both inverters is almost identical and the effect is cancellation of the variation in transfer voltage. This is taken advantage of in the circuit shown.

In the quiescent state with the input pulse low (ground), point 2 is high  $(V_{DD})$ , points 3, 4 and 5 are therefore low, low and high respectively. Capacitor  $C_1$  is therefore in a charged state. On receipt of the input pulse this charge is removed rapidly via the source resistance and  $D_1$  which is an internal protection device to prevent the input rising beyond V<sub>DD</sub>. On the negative-going edge of the input pulse point 2 is taken down to ground and  $C_1$  commences to charge towards  $V_{DD}$  via  $R_1$ . Point 3 will go high and remain in this state until  $C_1$  passes through the transfer voltage of inverter 1. When point 3 goes low  $C_2$ will commence to discharge via  $R_2$ ,  $D_2$  acting to prevent discharge into inverter 1. When point 4 passes through the transfer voltage of inverter 2 point 5 will go high and the operation is complete. The graphs show that there are two possible outputs-at points 3 and 5. The output at point 5 is the only one in which there is compensation

for transfer voltage variation. Due to lack of feedback in the circuit the risetime of the output is decidedly long (see performance data) but this is acceptable if the circuit is supplying further c.m.o.s. circuitry.

Despite the protection of D<sub>1</sub> the fact that the circuit is being fed via a capacitor makes it advisable to ensure that the input pulse height is close to V<sub>DD</sub>. This can be done if the pulse is fed via further c.m.o.s. supplied from  $V_{DD}$ . This circuit can be re-triggered, i.e. the output 5 can be maintained in its low state by feeding in a succession of pulses, provided each pulse occurs before point 2 reaches the transfer voltage of the first inverter.

#### **Circuit modifications**

A positive-going output • pulse, again triggered by the negative-going edge of the input is obtainable with the circuit shown top. In this case the output is obtained at the output of the first inverter viz point 3. This output is compensated, whereas that at 5 is not. Relevant waveforms are shown in Fig. 2. In this case re-triggering is not possible because any positivegoing trigger pulse would reduce  $T_1$  no matter the state of point 5.

• A negative-going pulse triggered on the positive-going edge of the input pulse is obtainable from the circuit shown in Fig. 3. For compensation, the output is taken from point 2 in this diagram. Relevant waveforms are as in Fig. 4. With this circuit re-triggering is also

#### Components

$D_2$ : general-purpose diode Inverter 1 and 2:  $\frac{1}{3} \times CD4007AE$

#### Performance

$R_1C_1 = R_2C_2 = RC$   $T \approx 1.4RC$ ; tested in range  $10\mu s < T < 1ms$ With clock rate of 1kHz and pulse width 400 $\mu$ s, T remains within 4% of the nominal value over supply range 5V to

impossible because point 2 will stay low so long as point 5 is high, the trigger signal having no effect due to the normal NOR gate action.

#### Further reading

RCA applications note ICAN6267. Murphy, C. Simple reconnection reduces rise time of CMOS delay circuit. *Electronic Design*, 4 Jan. 1974.

10V. With T of  $330\mu$ s fall time is minimal but rise time is  $120\mu$ s.

# Set 19: Monostable circuits—6

OUTPUT PULSEWIDTH (µs)

### **Emitter-coupled circuits**

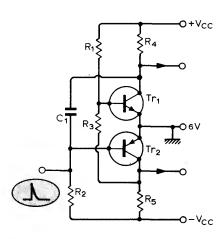

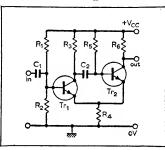

#### **Circuit description**

In the stable state Tr<sub>2</sub> is on and saturated due to the base drive via R5. The emitter current of Tr<sub>2</sub> causes the common emitter voltage to be at approximately 1.5V. Thus  $Tr_1$  is held off by the  $R_1$ ,  $R_2$ potential divider which maintains its base at about 1.3V, slightly reverse-biasing the base-emitter junction. Output voltage at Tr<sub>2</sub> collector is at approximately 1.6V in this stable state. The C<sub>1</sub>, R<sub>1</sub>, R<sub>2</sub> network differentiates the input trigger pulses and, if these have a positive-going transition large enough to exceed the emitter voltage by  $V_{BE}$ ,  $Tr_1$ will switch on and saturate. The collector voltage of Tr<sub>1</sub> falls by about 4.5V and this negative-going transition passes to  $Tr_2$  base through  $C_2$  so this transistor switches off. Output voltage rises to  $+V_{cc}$  and  $Tr_2$ remains in the off state while C2 charges via R5, Tr1 and R4. As C<sub>2</sub> charges, the base voltage of Tr<sub>2</sub> rises exponentially towards  $+V_{cc}$  but when it exceeds the emitter voltage, Tr<sub>2</sub> rapidly turns on and saturates. Current in R4 increases, producing a corresponding rise in the emitter voltage which reversebiases the base-emitter junction of  $Tr_1$ , which switches off, and the circuit returns to its stable state.

#### **Circuit changes**

Minimum trigger pulse width  $0.5\mu$ s. Output pulse width could be varied by  $R_5$  but this would also change the d.c. conditions. Larger supply voltages may be used but then a silicon diode should be included in series with  $Tr_2$  base

Typical performance Supply: +6V, 4mA Tr<sub>1</sub>, Tr<sub>2</sub>: BC125 R<sub>1</sub>:  $6.8k\Omega$ R<sub>3</sub>:  $1.8k\Omega$ R<sub>3</sub>:  $2.7k\Omega$ , R<sub>4</sub>:  $330\Omega$ R<sub>5</sub>:  $22k\Omega$ , R<sub>6</sub>:  $1k\Omega$ C<sub>1</sub>: 100pF, C<sub>2</sub>: 100nFInput pulse amplitude: +2VInput pulse width:  $1\mu$ s p.r.f.: 1kHz

to prevent reverse breakdown of its base-emitter junction by the switch-off transient.

#### **Circuit modifications**

• Adding an emitter-follower to the original circuit, as shown in the top left diagram, allows the output pulses to be obtained from a low-impedance source and to be referred to ground. By adjustment of the supply voltage these pulses may be made compatible with t.t.l. logic circuitry.

• A p-n-p common-emitter stage may be added, as shown top right, to use the output pulses for driving a groundconnected load. For example, the load could be in the form of a filament lamp for alarm or monitoring purposes and as collector currents of at least Output pulse—see waveform below

50mA may be obtained, the load could be a relay coil to provide control of some other circuitry. The inductive load provided by the relay coil should be shunted with a protective diode.

The original circuit may be modified to be triggered by negative-going pulses as shown in the circuit shown bottom left. In this arrangement the trigger pulses are applied to the collector of  $Tr_1$  via the small coupling capacitor  $C_3$ . The negative-going trigger pulse edge is passed to Tr<sub>2</sub> base through  $C_2$  switching this transistor off.  $Tr_1$  turns on and the remaining cycle of operations are as described previously. The circuit will function with  $C_1$  omitted but the transition to the quasi-stable state will be more rapid when it is included in the circuit.

10 C<sub>2</sub> (nF)

$R_5 = 22k\Omega$

• In all of the circuits discussed the output point was isolated from any internal coupling. If, see bottom right,  $R_1$  of the original circuit is taken to  $Tr_2$  collector instead of the  $+V_{CC}$  rail this is no longer the case and changes in emitter voltage may be very small. The simplest way to provide

faster switching is to prevent  $Tr_1$  and  $Tr_2$  from saturating by increasing  $R_4$ .

#### Further reading

SGS-Fairchild, Industrial Circuit Handbook, 1967, pp.51/2. Budinsky, J., Techniques of Transistor Switching Circuits, Iliffe 1968, pp.486-91.

2

#### **Cross references**

Set 18, cards 1 and 7.

# Set 19: Monostable circuits—7

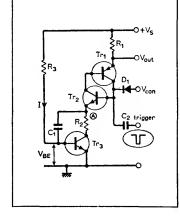

### Voltage-controlled monostables

#### Circuit description

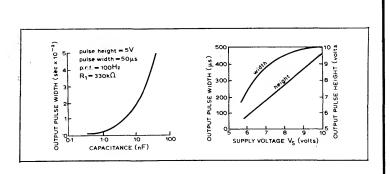

Transistors Tr<sub>1</sub>, Tr<sub>2</sub> form a complementary-pair positive feedback switch, and are either both off or both on. In the rest state, this switch is closed,  $Tr_3$  is on,  $D_1$  is non-conducting, and  $C_1$  is charged. A negative trigger pulse applied at the trigger terminal causes the regenerative switch  $(Tr_1, Tr_2)$ to open. Collector current of Tr<sub>3</sub> is now  $\alpha I$ , where  $\alpha$  is common base current gain and  $I = (V_{\rm S} - V_{\rm BE})/R_3$ . Hence C<sub>1</sub> discharges at a constant rate giving a run-down linear sweep at point A. This sweep continues until the potential of point A is less than  $V_{\text{control}} - V_{\text{D}_1} - V_{\text{BE}(\text{Tr}_2)}$ , when the complementary switch again conducts. The switch also acts as a comparator, besides providing a low impedance path for recharging capacitor C<sub>1</sub>. Notice that the sweep termination depends on the level of the control voltage, which therefore controls the width of the output pulse.

#### **Component changes**

Tr<sub>2</sub>, Tr<sub>3</sub>: BSX28, Tr<sub>1</sub>: BSX29 Useful range of  $C_1$ : 1 to 47nFUseful range of R<sub>3</sub>: 10k to  $100k\Omega$

Useful range of control voltage is in the range 10% to 90% of  $+V_{s}$ .

To minimize inductive and stray capacitive effects, this circuit was constructed on a p.c.b. to obtain above measurements.

Rise and fall times of output

**Typical performance** Tr<sub>1</sub>: BC126  $Tr_{2}$ ,  $Tr_{3}$ : BC125  $R_1$ : 22 $\Omega$ ,  $R_2$ : 1.2 $k\Omega$ R<sub>3</sub>: 10kΩ C<sub>1</sub>: 1nF, C<sub>2</sub>: 100pF  $+V_{s}:+10V$ D<sub>1</sub>: 1N914 Trigger pulse magnitude: -13V Trigger pulse width:  $0.1\mu$ s Vcontrol: 8V Output pulse duration:  $7\mu s$ Waveforms and timing graph shown opposite, curve (a)

pulses less than  $0.5\mu s$ . Control voltage may be obtained from potential divider connected across supply.

#### **Circuit modifications**

Connect additional buffer stage Tr<sub>4</sub> (BC126) and R<sub>4</sub> (390 $\Omega$ ) for increased output pulse amplitude (below). Trigger pulse amplitude is 7V, when coupling capacitor C<sub>2</sub> increased to 1nF; provides timing graph shown above a (b).

Circuit (centre) is basically an emitter-coupled monostable circuit. Time duration may be extended by the inclusion of a complementary pair (Tr<sub>6</sub>, Tr<sub>7</sub>) with breakdown fixed by zener diode  $D_2$ . This effectively increases the cut-in voltage,

V<sub>b</sub>, of Tr<sub>8</sub>. Tr<sub>8</sub> is normally on. Trigger pulses cause Tr<sub>5</sub> to conduct (Tr<sub>8</sub> off), and circuit returns to its stable state when the voltage at B brings the regenerative switch into conduction. Pulse duration depends on I, which is controlled by voltage applied to base of transistor Tr<sub>5</sub>. Output pulse duration typically in the range 40 to 200ms for a control voltage of 3 to 6V.

Operational amplifier IC, • (MC1530/MC1531), shown right, can provide variable delays by controlling the voltage at the inverting input. Diode clamps the negative amplitude of the output to about -0.7V. Positive output will approach +V.

#### Further reading

Rakovich, B. D. & Djurdjevich, B. Z., Wide-range voltage-to-time converter, IEEE Transactions vol. IM-22, no. 2, June 1973, p.162. Time delay circuit for SCR control, Electronic Eng. June 1974, p.14. Motorola application note AN-258.

Cross references Set 18, card 3, 6.

# Set 19: Monostable circuits—

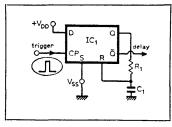

# Long-delay circuits using c.m.o.s. and unijunction devices

#### **Circuit description**

The high input impedance of c.m.o.s. integrated circuits offers a low leakage path for capacitor  $C_1$ , and thus allows a wide range of delays from this D-type flip-flop configuration. The D-input is permanently connected to the positive supply rail, hence Q goes high when a positive trigger pulse is applied at the clock input. A positive voltage approximately  $50\% (V_{DD} - V_{SS})$ at terminal R will reset Q to its initial condition of 0V. On the occurrence of a trigger pulse, the reset threshold will be reached in a time defined by  $C_1$  and  $R_1$ , which in turn defines the delay available at Q. This circuit is fairly insensitive to supply voltage change, because the threshold level for reset will alter pro-rata. However it should be noted that this level is not well defined, and hence the accuracy of time delays will depend on specific measurement with the components used. Unused inputs should be tied down to ground.

#### **Component changes**

Useful range of  $R_1$ : 100k to 10M $\Omega$ Useful range of  $C_1$ : 47pF to 32 $\mu$ F (For long time delays, lowleakage capacitors must be used) Supply voltage range:  $(V_{DD} - V_{SS})$  3 to 15V Minimum pulse width: 0.1 $\mu$ s Minimum pulse height: 2 to 4V Alternative IC: MM74C74

#### UJT transistor monostable

The circuit shown right (top). employs a discrete transistor flip-flop, with the timing controlled by the firing of the unijunction transistor  $Tr_1$ . Typical performance IC<sub>1</sub>:  $\frac{1}{2} \times CD$  4013AE V<sub>DD</sub>: +5V, V<sub>SS</sub>: 0V R<sub>1</sub>: 470k $\Omega$ , C<sub>1</sub>: 10 $\mu$ F Trigger pulse width: 1 $\mu$ s Trigger pulse height: 4V Delay: 9s Typical waveforms and delays shown opposite.

The normal rest condition of bistable FF1 is  $Tr_3$  off and  $Tr_2$ conducting. Hence the available voltage at point A is approximately  $V_{CESat}$  of  $Tr_2$ . This is much less than the firing voltage  $V_P$  of the unijunction transistor which therefore is non-conducting, and the output voltage is at zero volts.

A positive pulse applied at the trigger input brings Tr<sub>3</sub> into conduction, and due to positive feedback Tr<sub>2</sub> is rapidly switched off. Hence the potential of point A rises. Voltage across  $C_2$  now rises exponentially toward  $+V_s$ . When it reaches V<sub>P</sub> in a time determined by  $R_2C_2$ , Tr<sub>1</sub> will conduct and discharge C2 via the emitter and the resistor R<sub>E</sub>. The output pulse developed across RE is applied to the base of Tr<sub>2</sub> to turn it on again and hence reset the bistable, and turn off Tr<sub>1</sub>. Well-defined output pulses are also available at the collectors of Tr<sub>2</sub> and Tr<sub>3</sub>.  $R_2 1M\Omega$ ,  $C_2 1\mu$ F,  $R_E 27\Omega$ , Tr<sub>1</sub> 2N4853, Tr<sub>2</sub>/Tr<sub>3</sub> 2N4123,  $V_{s} + 10$  to +30V.

An advantage is that the initial voltage across  $C_2$  is always the same at the start of a period no matter the pulse repetition frequency. It is claimed that with the supply voltage variation noted above, pulse duration changes are  $2\%_0$ .  $\bullet$  Circuit (bottom) uses the transistor array CA3095E. Diodes D. D. and Tr. act as a

Diodes  $D_1$ ,  $D_2$  and  $Tr_5$  act as a voltage-limiting network. Quiescent condition is with transistors  $Tr_1$  and  $Tr_3$  off,  $Tr_2$  and  $Tr_4$  on. A negative-going pulse at the trigger-input terminal is coupled to the base of  $Tr_2$  via diode-connected transistor  $Tr_7$ . Hence  $Tr_2$  (and  $Tr_4$ ) cut off and  $V_{out}$  rises to  $+V_8$ . Because  $Tr_2$  and  $Tr_1$  are

emitter-coupled,  $Tr_1$  can now conduct when  $Tr_2$  is off, therefore the voltage across  $C_3$ i.e.  $V_L$  is near ground. Capacitor  $C_3$  now charges via  $R_3$ . When the base potential of  $Tr_2$  is high enough to bring it into conduction,  $Tr_1$  again goes off and  $V_{out}$  drops to its normal value of about 1.8V. Time duration is  $t \approx 0.47R_3C_3$ . Cross references Set 18, cards 5, 9.

#### Further reading

Unijunction Transistor Timers and Oscillators. Motorola application note AN-294.

# Set 19: Monostable circuits—9

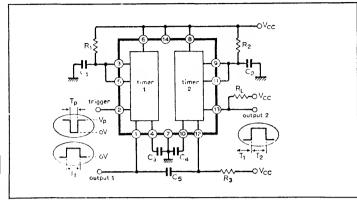

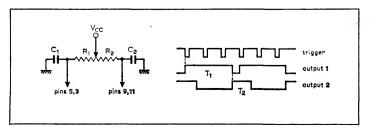

# Dual monostable applications using 555 timer

#### **Circuit description**

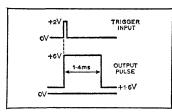

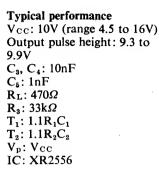

The i.c. shown is a dual 555-type timer (internal details of which are shown in cross references 1 and 2). In this application the output of the first timer is capacitively coupled via C5 to the input of the second. Both timers are triggered when the input to each drops below  $\frac{1}{3}V_{\rm CC}$ . In this case the trigger pulse operates timer 1 and the output of timer 1 triggers timer 2. Both timers are connected in their monostable mode. Formulae for  $T_1$  and  $T_2$  quoted are valid for all conditions and are fixed entirely by the external  $R_1$ ,  $C_1$ and  $R_1$ ,  $C_2$ . Any succeeding trigger pulses are ignored. Both  $T_1$  and  $T_2$  can be anywhere in the range  $10\mu$ s to 100s with two provisos: T<sub>1</sub> cannot be reduced below  $T_p$ , but since  $T_p$  can be less than  $3\mu$ s this is not serious. Secondly low values of  $T_1$  and T<sub>2</sub> should not be obtained by reducing R<sub>1</sub> and R<sub>2</sub> to a level at which current drain from the supply is serious. A minimum value of  $1k\Omega$  is recommended for both R<sub>1</sub> and R<sub>2</sub>.

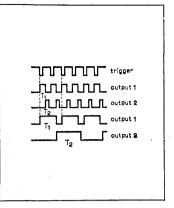

The only restriction on RL is that it must not be so low as to exceed the current rating (200mA) of the i.c. Typical waveforms are shown above. These are suitable for sequential timing circuits. Note that trigger pulses occurring during the period set by  $R_1$ ,  $C_1$ and  $R_2$ ,  $C_2$  are ignored.

# **Circuit modifications**

Obviously the i.c. may be used as two separate timers or monostables by omitting C<sub>5</sub> and  $R_3$  and by applying the trigger pulses directly to pins 2 and 12.

Referring to the main diagram, control over the total period  $(T_1 + T_2)$  can be achieved by connecting the arm of a potentiometer to Vcc and the ends to pins 3 and 9,  $R_1$  and  $R_2$ being now the two segments of the potentiometer shown above. If  $C_1 = C_2 = C$  then  $(T_1 + T_2) = C(R_1 + R_2)$  which is constant no matter the individual  $T_1$  and  $T_2$ .

Each individual timer can • be regarded as a frequency divider in its own right. For example, in the waveforms shown over, the lower two graphs indicate that output 1 is running at half the trigger pulse frequency and output 2 is running at half the frequency of output 1. By correct choice of T<sub>1</sub> one can make output 1 run at any submultiple frequency of the trigger and likewise with correct choice of  $T_2$  output 2 can run at any submultiple frequency of output 1.

A combined frequency divider and pulse width controller can be achieved by setting  $T_1$  so that it is greater

than the trigger period and by ensuring that  $T_{2} < T_{1}$ . The value of  $T_1$  sets the frequency division and the value of  $T_2$ sets the pulse width, the output being output 2. Furthermore, the "phase" of the output with respect to the trigger can be controlled since, for example, frequency division by 3 allows  $T_1$  to lie anywhere between two and three trigger periods. See waveforms above.

#### Further reading

XR-2556 Dual Timing Circuit. data sheet/application note, Exar Integrated Systems Inc.

Cross references Set 3, card 9 Set 13, cards 3 and 5

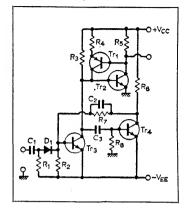

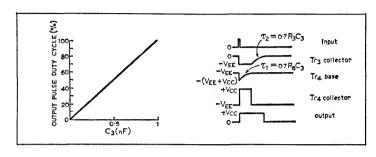

### High duty-cycle monostable

#### **Circuit description**

In this circuit the timing capacitor Ca not only determines the width of the output pulse obtained from Tr<sub>2</sub> collector but also delays the setting-up of the circuit in readiness for the next cycle of operations. This prevents an early trigger pulse from producing an output pulse having too short a duration. Because the circuit may be re-triggered immediately after completing its cycle, an output-pulse duty cycle approaching 100% may be obtained. The conventional "cross-coupled" monostable allows only about 95% duty cycle, even when its timing capacitor is rapidly recharged from a low-resistance source. In the stable state, Tr<sub>3</sub> is biased off and  $Tr_1$ ,  $Tr_2$  and  $Tr_4$  are on. Input trigger pulses are differentiated by  $C_1 R_1$ , the positive component passing to  $Tr_3$  base via  $D_1$ . If of sufficient amplitude, these overcome the reverse bias on Tr<sub>3</sub>, which switches on,  $Tr_1$ ,  $Tr_2$  and  $Tr_4$ switching off. Transistor Tr<sub>4</sub> remains off for approximately  $0.7\tau_1$  as its base potential rises under the control of C<sub>3</sub>. When  $Tr_4$  turns on again,  $Tr_3$  collector potential rises as  $C_3$  recharges with time constant  $\tau_2 = C_3 R_3$ until it exceeds approximately 0 V. Transistor Tr, and hence  $Tr_1$  then switch on regeneratively and the circuit returns to its stable state and may be re-triggered immediately.

#### **Component changes**

Minimum useful supplies  $\pm 2 V$ Useful range of R<sub>1</sub>: 1k to 100k $\Omega$ Useful range of R<sub>2</sub>: 1k to 470k $\Omega$  **Typical performance** Vcc: +6V, 6 to 18mA\*, V<sub>EE</sub> -6V, 6 to 12mA\* Tr<sub>1</sub>: BC126, Tr<sub>2</sub>, Tr<sub>3</sub>, Tr<sub>4</sub> BC125 R<sub>1</sub>: 10k $\Omega$ , R<sub>2</sub>, R<sub>7</sub>: 56k $\Omega$ R<sub>3</sub>, R<sub>8</sub>: 47k $\Omega$ , R<sub>4</sub>: 1.8k $\Omega$ R<sub>5</sub>, R<sub>6</sub>: 1.2k $\Omega$ , C<sub>1</sub>, C<sub>2</sub>: 100pF C<sub>3</sub>: see graph opposite; D<sub>1</sub> PS101 Input: 4V positive pulses, pulse width 1 $\mu$ s, p.r.f. about 10kHz Output rise time: 0.5 $\mu$ s Output fall time: 0.2 $\mu$ s \*depending on value of C<sub>3</sub>.

Minimum trigger pulse amplitude approximately 2.5 V Minimum trigger pulse width less than about  $0.1\mu$ s Maximum useful p.r.f.: 200kHz.

#### **Circuit modification**

The circuit shown top is a logical representation of a high duty-cycle monostable which may be realised with logic gates or discrete transistor circuitry. A pair of pulse-steering AND gates and a flip-flop used as a toggle cause the positive-going input trigger pulses to be alternately applied to the pair of monostables (M). The monostable outputs are combined in the OR gate to provide the output pulse and to toggle the flip-flop which changes state when the output pulse is completed. Hence, the start of the next output is only delayed by the time taken for the flip-flop to change its state, which can be a small percentage of the output pulse duration. A discrete version produced 700ms pulses every 705ms.

Circuit shown next uses a . flip-flop in conjunction with a Shockley diode (SD1) to achieve a high duty cycle. An input pulse causes the flip-flop to change its state producing an exponential voltage rise across  $C_4$ . When this voltage reaches a critical value the diode breaks down rapidly discharging C4 and producing a negative pulse to reset the flip-flop via  $C_a$  in readiness for the next input pulse. Pulses of  $2\mu$ s duration may be produced after only a 250ns recovery time.

Typically,  $R_1$ ,  $R_6 \quad 1M\Omega$ ,  $R_2$ ,  $R_3$ 10k $\Omega$ ,  $R_4$ ,  $R_5 \quad 150k\Omega$ ,  $R_7$ , 2.2M $\Omega$ ,  $C_1$ ,  $C_2$ ,  $C_3 \quad 20pF$ ,  $C_4$ 500nF,  $D_1 \quad 1N914$ , SD1 4E20-8, with Vcc +25V.

• Circuit shown bottom can provide a recovery time of only 1% of its period and may be triggered by positive pulses at  $Tr_1$  base or negative pulses at  $Tr_2$  base causing both transistors to switch from their on to off states. Transistor  $Tr_1$  can recharge  $C_1$  with a large collector current to rapidly regain its initial voltage. Diode  $D_1$  and  $D_2$  may be omitted if  $Tr_1$  and  $Tr_2$  have a large reverse  $V_{\rm BE}$  rating.

#### Further reading

Shagena, J. L. & Mall, A. Single-shot multivibrator has zero recovery time, *Electronics*, 27 Nov., 1967, p. 83. Electronic Circuit Design Handbook, 4th edition, Tab, 1971, pp. 85, 96, 342/3.

Cross reference

Set 19, card 9.

Set 19: Monostable circuits—10

# Set 19: Monostable circuits Up-date

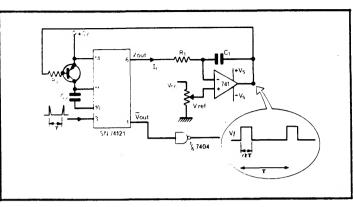

Disadvantages of monostables in digital circuits caused by their sensitivity to noise on the output line or transients in the power supply are avoided by using integrated-circuit monostables such as the SN74121. Two applications are considered.

1. The normal timing resistor for the monostable connected between pins 14 and 11 is replaced by the impedance of a transistor. The input trigger pulses to pin 3 provide predetermined pulse width at the output of the monostable depending on  $C_2$ and the effective resistance provided by the transistor which is changed by the feedback loop to maintain the duty cycle. The output pulse defines the time for which

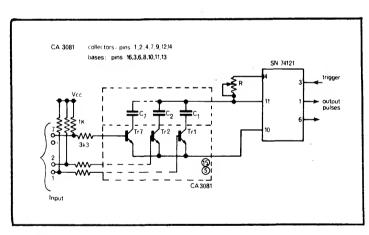

2. Integrated-circuit CA3081 contains seven n-p-n transistors with the emitters commoned. The control of pulse width from the integrated-circuit monostable is achieved by the **R-C** combination across pins 14, 11, 10. Hence by driving the base of one of the transistors  $Tr_1$  to  $Tr_7$ , a different capacitor is switched across pins 10, 11. The absolute value of capacitor depends on which of the input terminals are taken high or low respectively, and this may be

current  $I_1$  flows into  $C_1$ . For  $V_{out}$  high,

For V<sub>out</sub> low  $I_1 = \frac{V_{\text{out}L} - V_{\text{ref}}}{R}.$

In steady-state operation, the

average current to the capacitor is zero, when  $\alpha$  has reached the correct value. The above expression for  $I_{av}$  is then zero and

$$\alpha = \frac{V_{\rm ref} - V_{\rm outL}}{(V_{\rm outH} - V_{\rm outL})}$$

To avoid loading the monostable output and thus possibly varying  $V_{out_H}$  and  $V_{out_L}$ , an alternative output is taken from pin 1 via an inverter. Variable base drive due to V<sub>I</sub> can cause the transistor impedance to vary between 500 $\Omega$  and 500k $\Omega$ , allowing a pulse repetition frequency range of the order of 1000:1.

#### Reference

Langon, H. P. D. *Electronics*, July 24, 1975, p. 93.

controlled sequentially, as in the specific application of the reference, using a read-only memory package. It is suggested that temperature compensation for the pulse width might be achieved by including a thermistor as part of the tuning resistor network R.

Reference Pulford, I. P. & Risk, R. J. Applied Ideas: *Electronic Engineering*, Sept. 1974.

3. The input impedance of c.m.o.s. gates is very high and therefore provide a useful means of obtaining long delays with relatively small capacitance values. This circuit provides a means of eliminating the slow rise of capacitor voltage, when it is normally connected between gate-input and the  $V_{\rm SS}$  rail. When  $V_{\rm C}$  reaches the lower threshold value, then  $V_{\rm out}$  begins to go positive. As the charge on the capacitor

cannot change instantaneously,  $V_C$  follows the output at a rate determined only by the c.m.o.s. gate. A similar regenerative effect will occur

on a negative transition.

Reference

*Electronic Design 1*, January 4, 1974.