# CHIP-BY-CHIP

## THE GATING OF PULSES

### By Ed Noll

ating pulses on and off is an important facet in counting, switching, and other activities in digital circuits. The circuit arrangement of this column uses a clock generator and divider to form a low-frequency square-wave signal that will serve as a source of pulses that can be applied to one input of a NAND gate. How the logic applied to the second gate

R2 390K ≹RI ≸680K CLOCK 555 6 C2 0.01 CI IMFD -0+V 15 14 13 DIVIDER COUNTER 12 SQUAREWAVE 4017 11 10 9

Figure 1.555 Clock and 4017 Divider Generate the Pulse Train.

input affects the transfer of the pulses to the gate output can be shown. The LED demonstrates such action clearly because of the low repetition rate of the clock pulses. The same observations will be made using several other gates including AND, NOR and OR types.

The schematic of the clock and divider pulse generator is given in Figure 1, in case you haven't built this basic unit for one of the previous columns. Capacitor C1 is used to set the clock frequency. The frequency desired is obtained by using a capacitor value of 1 uF for C1.

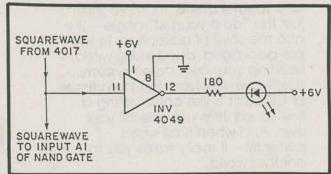

Figure 2. Addition of Inverter to Divider Output. LED is ON when Input is at logic 1.

The next step in assembling the demonstration circuit is to add a simple logic indicator at the output of the generator, Figure 2. This is one of the inverters in the 4049 inverter chip used in a previous column. The output LED of the converter is connected to illuminate when there is a logic 1 at the inverter input.

Connect this circuit to the clock output. Turn on the generator. Note the equal-length on and off periods of the generated square-wave pulse train. This is the pulse train that will be applied to the NAND gate to

observe its operation.

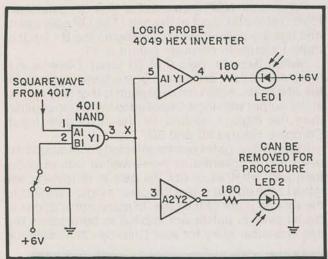

The NAND gate is a quad 4011 which we used in a previous column, in the Spring 1988 issue of Electronics Handbook. Next wire the single NAND gate and follow it with a logic probe comprised of two more of the 4049 inverters. The complete circuit is described in Figure 3. The logic probe circuit is the same as the one you may have built for use in the demonstration circuit of the previous column.

Figure 3. NAND Gate Circuit Followed by Logic Probe. Use only LED 1 leg.

In the operation of the logic probe when the Y1 output of the NAND gate is logic 1, LED 1 will go on. If the Y1 output is logic 0, LED 2 would normally go on. In this demonstration circuit, however, the LED 2 side of the circuit is not needed. Consequently, you can remove LED 2 from the circuit to avoid any confusion.

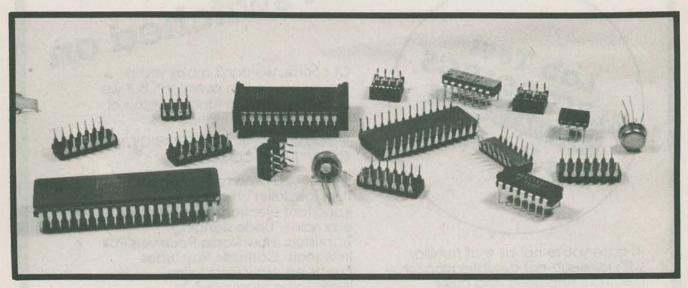

The output of the pulse generator is applied to the NAND gate input A1. A wire lead is connected to NAND gate input B1. This lead is used to connect either a logic 1 (+6 volts) or a logic 0 (GND) to NAND gate input B1 when checking out gate operation with the pulse train from the generator applied to gate input A1. The four chips used in the demonstration circuit are shown photographically in Figure 4. Starting from the top, they are the 555 clock, the 4017 counter, the 4049 inverter, and the 4011 NAND gate chips.

#### Observing NAND Gate Operation

Turn on the generator. When you do so, you will notice the generator output indicator LED will flash on and off, showing that the clock generator is working and is being applied to the NAND gate input A1. Next switch the NAND input gate B1 to logic 1 by inserting the associated lead at a +6 volt point. By so doing the gate is switched on and the pulse train passes to the gate output Y1 as proven by the flashing of LED 1 of the logic probe. Switch the NAND input gate B1 to logic 0. Now the gate is switched off and no pulse train passes to the output.

Figure 4. Components mounted on Solderless Circuit Board.

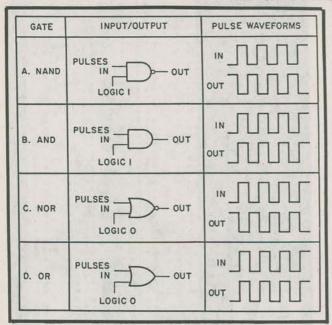

Change gate input B1 back to logic 1 to switch the gate on once again. Observe the phasing of the gate input and output pulse train. When the input pulse is positive the output pulse is negative. Stated another way, the switched on NAND gate inverts the pulse train, Figure 5A. Keep this in mind as you check out some of the other gates.

#### Observing AND, NOR and OR Gate Operations

Replace the 4011 NAND gate with a 4081 AND gate. Gate wiring is identical and the changeover can be done without any rewiring of the circuit board. Just remove the 4011 and replace it with the 4081. Turn on the generator again. Switch the AND input gate B1 to logic 1. The AND gate closes and the pulse train appears at the gate output. Switch the AND input gate B1 to logic 0 and the pulse train does not appear at the gate output.

Go back to logic 1 at input B1. Observe the different phasing of the input and output pulse train. When the input pulse is positive the output pulse is positive too. The two LED's turn on and off at the same time indicating that the input and output pulses have the same logic phasing, just the opposite of the NAND

#### THE GATING OF PULSES

Figure 5. Summary of Gate Operation.

of Figure 5A and B.

Remove the AND gate and replace it with the 4001 NOR gate. Again no rewiring is necessary. Turn on the demonstration circuits. Connect the NOR gate input B1 to logic 0. The gate is switched on and the gate operation. Refer to the pulse waveform drawings pulses appear at the Y1 output. Connect the NOR gate input at logic 1. Pulses do not appear at the output.

Change the B1 input back to logic 0. Observe that the NOR gate output is inverted as compared to the generator pulses applied to the NOR gate input A1. The same situation existed for the NAND gate operation. However there is one difference. NOR gate on operation occurs when the input B1 is logic 0 rather than the logic 1 of NAND gate operation. Compare Figure 5A and 5C.

Replace the NOR gate with the 4071 OR gate. Use a logic 0 at the B1 input of the gate. The OR gate opens and lets the pulse through. Changing the B1 input to logic 1 results in no pulse putput at Y1.

Switch back to logic 0 at B1 input. Observe that input and output pulses are of the same logic as for the AND gate. Again the exception is that they appear at the output with logic 0 applied to the B1 input rather than the logic 1 needed by the AND gate input. Compare Figures 5B and 5D.

In summary, gates can be selected according to the need for an inverted or non-inverted output pulse train and, whether or not the gate is to transfer the input to the output with a logic 0 or a logic 1 applied to the second input of the gate. In many applications in digital circuits pulses are applied to both gates. But that is another story for your Chip-By-Chip column.

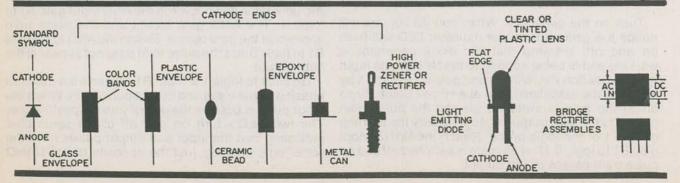

Correspondence from some of our readers leads us to new ones with known values?" believe that there is considerable confusion among readers who have only recently joined the ranks of the "Electronics Hobbyists" concerning the identification and/or value of some of the more common diodes. For example, the following letter, recently received from a reader, pretty well sums it up:

power supply that I can use to power a walkie-talkie from house current. I've finally given up and decided to build my own. I have a transformer that converts 110 VAC to 12.6 VAC, some large filter capacitors salvaged from a discarded television set and some 'bargain bag' diodes I purchased from a discount store. The diodes are black, unmarked, and have one rounded end. Can I use them, or will I have to invest in your possession.

Of course, we couldn't be sure exactly what the reader had in this supply of diodes, but from the description, and our reference to the above chart, we were fairly certain that he had a supply of epoxyencapsulated rectifiers with somewhere between 100 to 200-PIV rating. These would easily fill his needs if "I have been trying for several months to purchase a our guess was right. Although we haven't heard anything further from this reader, we assume that he didn't blow himself up.

> For those readers who have similar difficulty with diodes, we suggest that you keep a copy of this chart handy on your workbench or in your spare parts "junkbox" as a reference for identifying the leads and types of whatever diodes happen to find their way into