Application Note 26A

January 1988

## Interfacing the LTC1090 to the 8051 MCU

Guy Hoover William Rempfer

#### Introduction

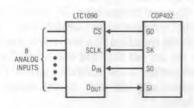

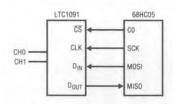

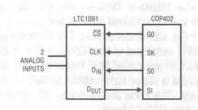

This application note describes the hardware and software required for communication between the LTC1090 10-bit data acquisition system and the MCS-51 family of microcontrollers (e.g., 8051). The four wire interface is capable of completing a 10-bit conversion and transferring the data to the 8051 in 102 $\mu$ s. Configuration of the 8051 and the LTC1090 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be discussed. Finally, a summary of results including data throughput rates will be provided.

#### **Interface Details**

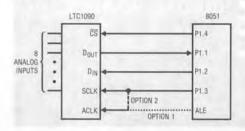

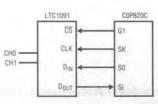

The serial port of the 8051 does not support the synchronous, full duplex format used by the LTC1090. Therefore it is necessary for the user to construct a serial port using four lines from one of the parallel ports available on the 8051. The lines are set or cleared using the bit manipulation features of the 8051. This provides a very flexible serial port but the data shift rate is three to four times slower than that available from microcontrollers with dedicated serial ports.

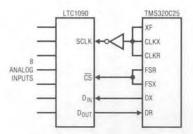

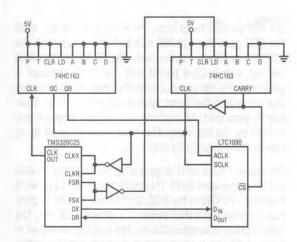

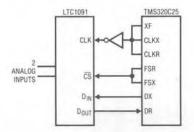

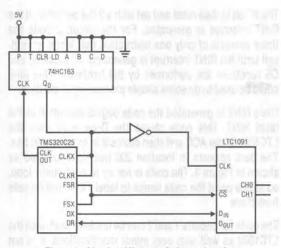

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. These lines may be tied together or run separately. The 8051 provides a pin (ALE) which can be used to drive the ACLK of the LTC1090 (option 1). Alternatively, tying the clocks together saves one line that has to go between the LTC1090 and the 8051 (option 2). However, this implementation slows the data throughput rate due to additional code. The schematic of Figure 1 shows both of these options.

#### **Hardware Description**

The 8051 was simulated and the code for this interface was developed on an Intel ICE 252 emulator.

Due to the weak pullups of the 8051, excess loading should be avoided when examining the output of the microcontroller.

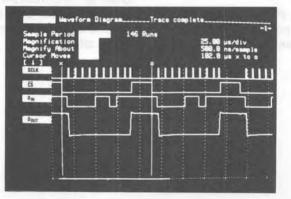

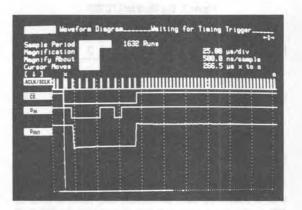

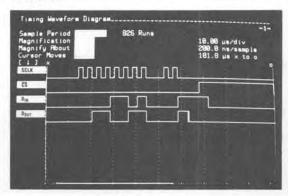

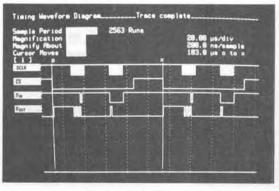

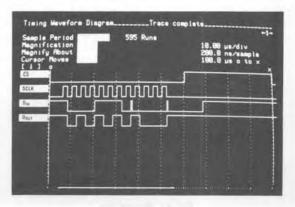

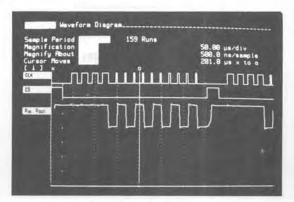

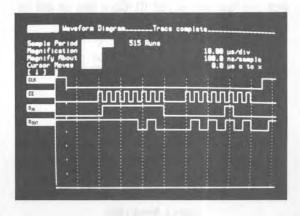

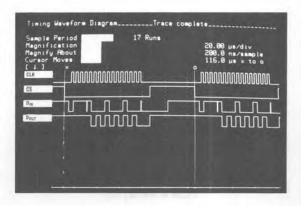

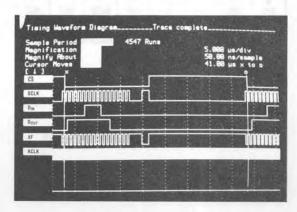

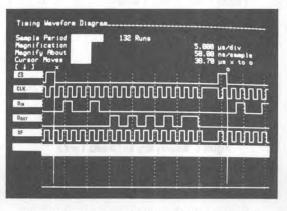

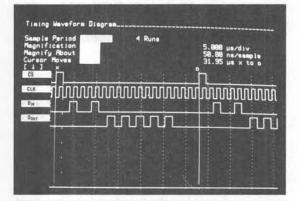

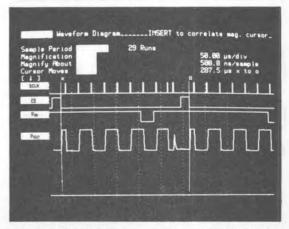

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer using separate ACLK and SCLK (option 1). The 8051 clock rate was 12MHz, producing a 2.0MHz clock on the ALE pin.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

#### Software Description

The software simulates a serial port through bit manipulation instructions of the 8051. Additionally, the software generates a delay during which time the A/D conversion takes place.

The code sets up bit one of port one as an input by setting it high. (Due to the weak pullup of the 8051, the  $D_{OUT}$  pin of the LTC1090 can then drive the pin high or low.)

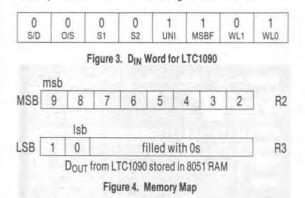

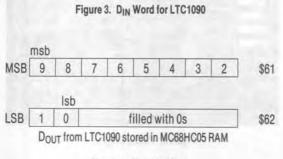

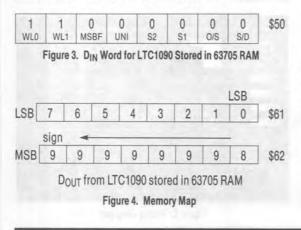

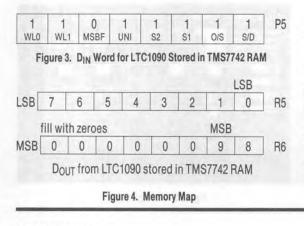

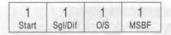

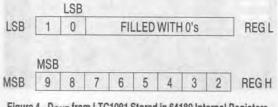

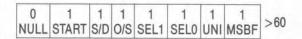

SCLK is initialized to a low state and  $\overline{CS}$  is initialized to a high state. A D<sub>IN</sub> word of \$0D is then loaded into the ac-

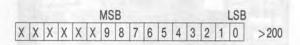

cumulator. An examination of Figure 3 and the data sheet will show that this configures the LTC1090 for CH0 with respect to CH1, unipolar, MSB first and a 10-bit word length. Next  $\overline{CS}$  goes low. If the user is tying ACLK and SCLK together (option 2) it is then necessary to generate two clock pulses to meet the deglitcher requirements. With separate clocks (option 1) the NOP is necessary to allow sufficient time for the deglitcher before starting to shift the data. Data is moved from the P1.1 pin (D<sub>OUT</sub> of the LTC1090) to the carry register and shifted one bit at a time into the accumulator. At the same time, the 8-bit D<sub>IN</sub> word is shifted from the accumulator into the carry register and output on P1.2 (D<sub>IN</sub> of the LTC1090).

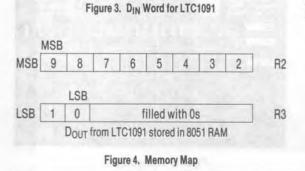

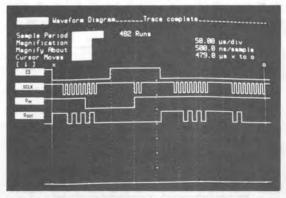

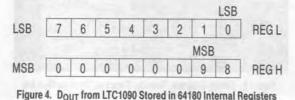

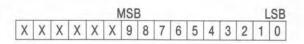

After the eight MSBs have been shifted, the contents of the accumulator are stored in R2. The final two bits are then shifted into the accumulator, placed in the most significant bits and stored in R3. The data is left justified at this point with the MSBs in R2 and the LSBs in R3.  $\overline{CS}$  is then raised and time (44 ACLK cycles) for the LTC1090 to do its next conversion must be allowed before the next read can be performed. If separate clocks are being used (option 1), quite often the microcontroller will have other tasks to accomplish and this time can be used productively. Otherwise, a routine such as the one labeled DELAY can be used. With the clocks tied together (option 2), it is necessary for the 8051 to manually clock the LTC1090 44 times and this free time is then lost as shown in Figure 7. An example of this routine is labeled LOOP 1.

Figure 2. Timing Diagram for Option 1

If right justified data is required, the MSBF bit of the  $D_{IN}$  word could be cleared and the bits reversed (in this case producing a  $D_{IN}$  word of \$90). Also it would be necessary to swap the rotate left and rotate right instructions.

#### Summary

A four wire interface between the LTC1090 and the 8051 with a combined data conversion and transfer time of  $102\mu$ s was demonstrated. It was shown that the ACLK of the LTC1090 can be run separately from the SCLK by tying the ACLK to the ALE of the 8051. Alternatively, the two clock pins can be tied together (saving one line at the expense of speed). The data can be either left justified or right justified in the microcontroller's memory through the proper choice of software and LTC1090 data format. The code shown applies to all MCS-51 family members. The same technique can be used on any parallel port processor.

#### MNEMONIC COMMENTS MOV P1, #02H BIT 1 PORT 1 SET AS INPUT P1.3 SCLK GOES LOW CLR P1.4 CS GOES HIGH SETB MOV A, #ODH DIN WORD FOR LTC1090 CS GOES LOW CLR P1.4

LABEL

CONT

Application Note 26A

|       | MOV  | R4, #08H         | LOAD COUNTER              |  |

|-------|------|------------------|---------------------------|--|

|       | NOP  |                  | DELAY FOR DEGLITCHER      |  |

| LOOP  | MOV  | C, P1.1          | READ DATA BIT INTO CARRY  |  |

|       | RLC  | A                | ROTATE DATA BIT INTO ACC  |  |

|       | MOV  | P1.2, C          | OUTPUT DIN BIT TO LTC1090 |  |

|       | SETB | P1.3             | SCLK GOES HIGH            |  |

|       | CLR  | P1.3             | SCLK GOES LOW             |  |

|       | DJNZ | R4, LOOP         | NEXT BIT                  |  |

|       | MOV  | R2, A            | STORE MSBs IN R2          |  |

|       | MOV  | C. P1.1          | READ DATA BIT INTO CARRY  |  |

|       | CLR  | A                | CLEAR ACC                 |  |

|       | RLC  | A                | ROTATE DATA BIT INTO ACC  |  |

|       | SETB | P1.3             | SCLK GOES HIGH            |  |

|       | CLR  | P1.3             | SCLK GOES LOW             |  |

|       | MOV  | C, P1.1          | READ DATA BIT INTO CARRY  |  |

|       | RRC  | A                | ROTATE RIGHT INTO ACC     |  |

|       | RRC  | A                | ROTATE RIGHT INTO ACC     |  |

|       | MOV  | R3, A            | STORE LSBs IN R3          |  |

|       | SETB | P1.3             | SCLK GOES HIGH            |  |

|       | CLR  | P1.3             | SCLK GOES LOW             |  |

|       | SETB | P1.4             | CS GOES HIGH              |  |

|       | MOV  | R5, #07H         | LOAD COUNTER              |  |

| DELAY | DJNZ | R5. DELAY        | GO TO DELAY IF NOT DONE   |  |

|       |      | tion a series at | as is security that bothe |  |

Figure 5. 8051 Code for Option 1 (ACLK Tied to ALE)

TLINEAR

## Application Note 26A

| LABEL  | MN   | EMONIC     | COMMENTS                  |

|--------|------|------------|---------------------------|

|        | MOV  | P1, #02H   | BIT 1 PORT 1 SET AS INPUT |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | SETB | P1.4       | CS GOES HIGH              |

| CONT   | MOV  | A, #0DH    | DIN WORD FOR LTC1090      |

|        | CLR  | P1.4       | CS GOES LOW               |

|        | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | MOV  | R4, #08H   | LOAD COUNTER              |

| LOOP   | MOV  | C. P1.1    | READ DATA BIT INTO CARRY  |

|        | RLC  | A          | ROTATE DATA BIT INTO ACC  |

|        | MOV  | P1.2, C    | OUTPUT DIN BIT TO LTC1090 |

|        | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | DJNZ | R4, LOOP   | NEXT BIT                  |

|        | MOV  | R2, A      | STORE MSBs IN R2          |

|        | MOV  | C, P1.1    | READ DATA BIT INTO CARRY  |

|        | CLR  | A          | CLEAR ACC                 |

|        | RLC  | A          | ROTATE DATA BIT INTO ACC  |

|        | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | MOV  | C, P1.1    | READ DATA BIT INTO CARRY  |

|        | RRC  | A          | ROTATE RIGHT INTO ACC     |

|        | RRC  | A          | ROTATE RIGHT INTO ACC     |

|        | MOV  | R3, A      | STORE LSBs IN R3          |

|        | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | SETB | P1.4       | CS GOES HIGH              |

|        | MOV  | R4, #2CH   | LOAD COUNTER              |

| LOOP 1 | SETB | P1.3       | SCLK GOES HIGH            |

|        | CLR  | P1.3       | SCLK GOES LOW             |

|        | DJNZ | R4, LOOP 1 | GO TO LOOP 1 IF NOT DONE  |

|        |      |            |                           |

Figure 7. Timing Diagram for Option 2

TLINEAR

Figure 6. 8051 Code for Option 2 (ACLK Tied to SCLK)

### Application Note 26B

## December 1987

## Interfacing the LTC1090 to the MC68HC05 MCU

Guy Hoover William Rempfer

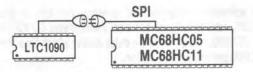

#### Introduction

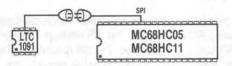

This application note describes an interface between the LTC1090 10-bit data acquisition system and the Motorola SPI family of single chip microcomputers (e.g., 68HC05). The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the 68HC05 in  $49\mu$ s. Configuration of the LTC1090 and the 68HC05 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given, including data throughput rates.

#### Interface Details

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. Data is transferred in a synchronous, full duplex format over  $D_{IN}$  and  $D_{OUT}$ .

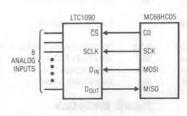

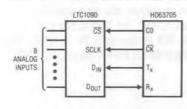

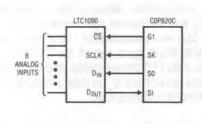

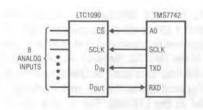

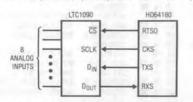

The Motorola Serial Peripheral Interface (SPI) is a synchronous, full duplex, serial port built into the 68HC05 that allows the user to construct a simple communication path to the LTC1090. SPI provides clock, data in and data out lines that are compatible with the LTC1090. The only additional line required is one programmable output pin (CO) to control  $\overline{CS}$  on the LTC1090. The schematic of Figure 1 shows how the two devices are connected.

#### Figure 1. Schematic

TLINEAR

#### **Hardware Description**

The 68HC05 was emulated and the code for this interface was developed on a Motorola M68HC05 EVM.

SS (Pin 34) of the 68HC05 must be held high to enable the SPI properly for this interface.

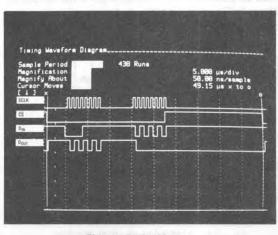

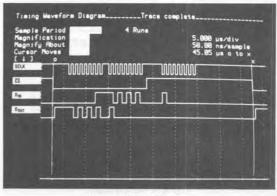

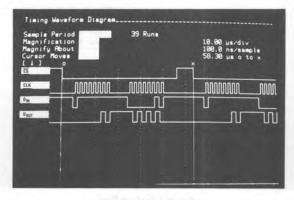

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer using a 2MHz ACLK. The 68HC05 clock was 4MHz.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

#### Figure 2. Timing Diagram

AN26B-1

#### Software Description

The software configures and controls the SPI of the 68HC05. Additionally, the software manipulates CO (CS of the LTC1090) and generates a delay during which time the LTC1090 performs a conversion.

The code first configures the Serial Peripheral Control Register (SPCR) of the SPI. The SPI interrupt is disabled. The SPI outputs are enabled. The SPI is configured as a master. Finally, the SPI clock is set to normally low, for data transfer on the rising edge and for a frequency equal to half the internal processor clock (one fourth the crystal frequency).

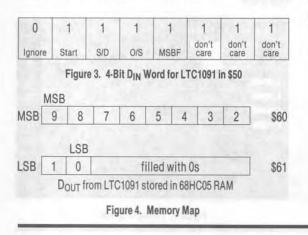

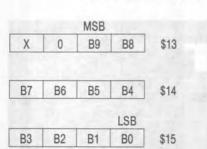

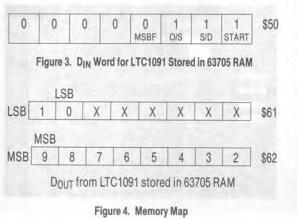

Port C is configured as all outputs by placing ones in the data direction register of port C. A  $D_{IN}$  word that configures the LTC1090 for CH0 with respect to CH1, unipolar, MSB first and a 16-bit word length is stored in \$50. Figure 3 shows how the  $D_{IN}$  word is composed.

CO is made to go low.  $D_{IN}$  for the LTC1090 is loaded into the SPI data register. Storing  $D_{IN}$  in the data register causes the transfer to begin. After waiting for the first eight bits to be transferred (8 NOPs) the status register of the SPI is examined. This clears the SPIF bit of the status register and allows the data register to be read, which is the next step. The first eight bits containing the MSBs from the LTC1090 are then stored in \$61 of the 68HC05 as shown in Figure 4. The LSBs are transferred in the same manner and stored in \$62 of the 68HC05. Notice in Figure 5

| 0   | 0   | 0  | 0  | 1   | 1    | 1   | 1   |

|-----|-----|----|----|-----|------|-----|-----|

| S/D | O/S | S1 | S2 | UNI | MSBF | WL1 | WLO |

Figure 4. Memory Map

that only 6 NOPs are used in transferring the LSBs. This is because after 6 NOPs, time is consumed by the BSET command which sets the CO pin of the 68HC05. The data at this point is left justified.

At this time 44 ACLK cycles must be allowed for the A/D to perform its next conversion. Usually the processor will have other tasks to perform during this time. If this is not the case a string of NOPs or a simple delay loop can be used to generate this delay.

The code was written for the 68HC05. By changing the addresses of the special function registers however, the code should run on all of Motorola's SPI processors including the 68HC11.

#### Summary

A four wire interface between the LTC1090 and the 68HC05 with a combined data conversion and transfer time of  $49\mu$ s was demonstrated. The interface used the serial (SPI) port of the 68HC05. The 10 data bits of the LTC1090 are shifted MSB first in two eight bit transfers. The data is stored left justified in the 68HC05's internal RAM.

| LABEL | MNEMONIC |        | COMMENTS                        |

|-------|----------|--------|---------------------------------|

|       | LDA      | #\$50  | CONFIGURATION DATA FOR SPCR     |

|       | STA      | \$0A   | LOAD DATA INTO SPCR (\$0A)      |

|       | LDA      | #\$FF  | CONFIG. DATA FOR PORT C DDR     |

|       | STA      | \$06   | LOAD DATA INTO PORT C DDR       |

|       | LDA      | #\$0F  | LOAD LTC1090 DIN DATA INTO ACC  |

|       | STA      | \$50   | LOAD LTC1090 DIN DATA INTO \$50 |

| START | BCLR     | 0,\$02 | CO GOES LOW (CS GOES LOW)       |

|       | LDA      | \$50   | LOAD DIN INTO ACC FROM \$50     |

|       | STA      | \$0C   | LOAD DIN INTO SPI. START SCK    |

|       | NOP      |        | 8 NOPs FOR TIMING               |

|       | LDA      | \$0B   | CHECK SPI STATUS REG            |

|       | LDA      | \$0C   | LOAD LTC1090 MSBs INTO ACC      |

|       | STA      | \$61   | STORE MSBs IN \$61              |

|       | STA      | \$0C   | START NEXT SPI CYCLE            |

|       | NOP      |        | 6 NOPs FOR TIMING               |

|       | BSET     | 0,\$02 | CO GOES HIGH (CS GOES HIGH)     |

|       | LDA      | \$0B   | CHECK SPI STATUS REGISTER       |

|       | LDA      | \$0C   | LOAD LTC1090 LSBs INTO ACC      |

|       | STA      | \$62   | STORE LSBs IN \$62              |

|       |          |        | very and a                      |

Figure 5. 68HC05 Code

AN26B-2

Application Note 26C

January 1988

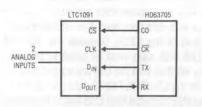

## Interfacing the LTC1090 to the HD63705V0 MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes an interface between the LTC1090 10-bit data acquisition system and the Hitachi 63705 microcomputer. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the 63705 in 45 $\mu$ s. Configuration of the LTC1090 and the 63705 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

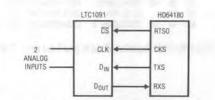

#### **Interface Details**

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. Data is transferred in a full duplex format over  $D_{IN}$  and  $D_{OUT}$ .

The Hitachi Serial Communication Interface (SCI) is a synchronous, full duplex, serial port built into the 63705 that allows the user to construct a simple communication path to the LTC1090. SCI provides clock, transmit and receive lines that are compatible with the LTC1090. The only

Figure 1. Schematic

additional line required is one programmable output pin (C0) to control  $\overline{\text{CS}}$  on the LTC1090. The schematic of Figure 1 shows how the two devices are connected.

#### **Hardware Description**

The 63705 was emulated and the code for this interface was developed on a Hitachi H35MIX3 emulator.

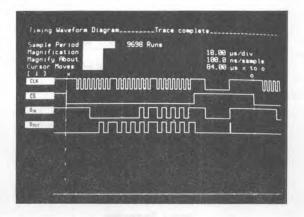

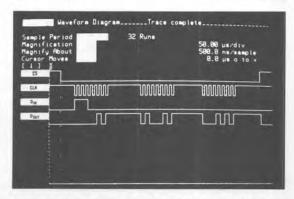

The timing diagram of Figure 2 was obtained using an HP1631A logic analyzer. ACLK of the LTC1090 was 2 MHz and the 63705 clock was 4 MHz.

The analog section of the schematic of Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

Figure 2. Timing Diagram

AN26C-1

#### Software Description

The software configures and controls the SCI of the 63705. Additionally, the software manipulates C0 ( $\overline{CS}$  of the LTC1090) and generates a delay during which time the LTC1090 performs a conversion.

The code first configures the SCI control register (SCR). D3 and D4 are set as the SCI output and input respectively. D5 is selected as a clock output with a frequency one fourth the crystal frequency. Next, the SCI status register (SSR) is configured so that the interrupts are disabled. Data is transmitted on the falling edge of the clock and received on the rising edge of the clock.

Port C is configured as all outputs by setting the data direction register (address \$06). A  $D_{IN}$  word that configures the LTC1090 for CH0 with respect to CH1, bipolar, LSB first and a 16-bit word length is stored in \$50. Figure 3 shows how the  $D_{IN}$  word is composed. Note, that for LSB first format the  $D_{IN}$  word must be constructed opposite from MSB first format. This is so that each bit of the  $D_{IN}$  word is always shifted into the LTC1090 in the same order.

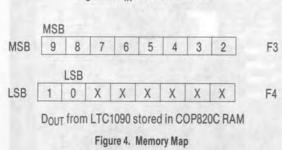

C0 is made to go low. D<sub>IN</sub> for the LTC1090 is loaded into the SCI data register (SDR). Storing D<sub>IN</sub> in the SDR causes the transfer to begin. After waiting for the first eight bits to be transferred (6 NOPs) the data containing the LSBs from the LTC1090 is loaded into the accumulator and then stored in \$61 of the 63705 RAM. The act of reading the LSBs into the ACC causes the next SCI transfer to begin. C0 is set and the MSBs from the LTC1090 are loaded into the ACC and then stored in \$62 of the 63705 RAM.

| LABEL | MNE  | MONIC  | COMMENTS                        |  |

|-------|------|--------|---------------------------------|--|

|       | LDA  | #\$E0  | CONFIGURATION DATA FOR SCR      |  |

|       | STA  | \$10   | LOAD DATA INTO SCR (\$10)       |  |

|       | LDA  | #\$30  | CONFIGURATION DATA FOR SSR      |  |

|       | STA  | \$11   | LOAD DATA INTO SSR (\$11)       |  |

|       | LDA  | #\$FF  | CONFIG. DATA FOR PORT C DDR     |  |

|       | STA  | \$06   | LOAD DATA INTO PORT C DDR       |  |

|       | LDA  | #\$C0  | LOAD LTC1090 DIN DATA INTO ACC  |  |

|       | STA  | \$50   | LOAD LTC1090 DIN DATA INTO \$50 |  |

| START | LDA  | \$50   | LOAD DIN INTO ACC FROM \$50     |  |

|       | BCLR | 0,\$02 | CO GOES LOW (CS GOES LOW)       |  |

|       | STA  | \$12   | LOAD DIN INTO SDR. START SCK    |  |

|       | NOP  |        | 6 NOPs FOR TIMING               |  |

|       | LDA  | \$12   | LOAD LSBs. START NEXT CYCLE     |  |

|       | STA  | \$61   | STORE LSBs IN \$61              |  |

|       | NOP  |        | 1 NOP FOR TIMING                |  |

|       | BSET | 0,\$02 | CO GOES HIGH (CS GOES HIGH)     |  |

|       | LDA  | \$12   | LOAD MSBs                       |  |

|       | STA  | \$62   | STORE MSBs IN \$62              |  |

|       |      |        |                                 |  |

Figure 5. 63705 Code

The data at this point is right justified with the sign bit (B9) being extended into B1–B7 of \$62 as shown in Figure 4.

At this time 44 ACLK cycles must be allowed for the A/D to perform its next conversion. Usually the processor will have other tasks to perform during this time (you have to do something with the data once the processor has it). If this is not the case, a string of NOPs or a simple delay loop can be used to generate this delay.

#### Summary

A four wire interface between the LTC1090 and the Hitachi 63705 with a combined data conversion and transfer time of  $45\mu$ s was demonstrated. The interface used the serial (SCI) port of the 63705. Because the SCI port transfers data LSB first, care must be taken to properly construct the D<sub>IN</sub> word so that the bits are transmitted in the proper order to the LTC1090. The 10 data bits of the LTC1090 are shifted LSB first in two eight bit transfers. The data is stored right justified in the 63705s internal RAM.

AN26C-2

Application Note 26D

MICROWIRE/PLUST

National Semiconductor

COP800

January 1988

## Interfacing the LTC1090 to the COP820C MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes the hardware and software required for communication between the LTC1090 10-bit data acquisition system and the National Semiconductor COP800 microcontroller family which uses the MICROWIRE/PLUS serial interface. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data in 56 $\mu$ s. Configuration of the LTC1090 and the COP820C will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### **Interface Details**

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. Data is transferred in a full duplex format over  $D_{IN}$  and  $D_{OUT}$ .

The National Semiconductor MICROWIRE/PLUS is a synchronous, full duplex, serial port built into the COP800 family that allows easy interface to the LTC1090. MICROWIRE/PLUS provides clock, data in and data out lines that are compatible with the LTC1090. One additional

Figure 1. Schematic

line (G1) is required to control the  $\overline{CS}$  pin on the LTC1090. The schematic of Figure 1 shows how the two devices are

#### **Hardware Description**

connected.

LTC1090

The actual interface was done using the COP820C, a member of the COP800 family. All code shown here should work with any of the COP800 family.

The code for this interface was developed on a COP820 evaluation board operated in the emulation mode.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer using a 2MHz ACLK. The COP820C clock was 5MHz. To obtain a  $56\mu$ s transfer time it is necessary to run the COP820C at 20MHz which requires a high speed version of the part.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

AN26D-1

### Application Note 26D

#### Software Description

The software configures and controls the MICROWIRE/ PLUS serial interface of the COP820C. Additionally, the software manipulates G1 (CS of the LTC1090) and generates a delay during which time the LTC1090 performs a conversion.

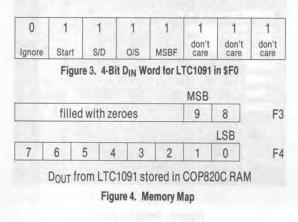

The code first loads the LTC1090 DIN word into memory location. \$F0. This DIN word configures the LTC1090 for CH0 with respect to CH1, MSB first, unipolar and 10 bits as shown in Figure 3. Next port G is configured for MICROWIRE<sup>™</sup> master mode and G1 is configured as an output. The control register is initialized so that SO and SK are outputs. The port G data register address is loaded into the B register. At this point the COP820C is initialized and the data transfer process is ready to begin.

The DIN word for the LTC1090 is then loaded into the ACC from location \$F0. G1 (CS) is cleared and DIN is transferred into the MICROWIRE shift register. The BUSY bit of the PSW register is set which starts the transfer of the first eight bits. A delay consisting of 15 NOPs waits for the data shift to finish at which time the Dour word from the LTC1090 is loaded into the ACC. The busy bit is set again which causes the transfer to continue. Then, the DOUT word in the ACC is stored in location \$F3. The busy bit is cleared which halts the transfer. Two more bits have been shifted at this point. G1 (CS) is set and the contents of the

| 0   | 0   | 0  | 0  | 1   | 1    | 0   | 1   |

|-----|-----|----|----|-----|------|-----|-----|

| S/D | O/S | S1 | S2 | UNI | MSBF | WL1 | WLO |

Figure 3. DIN Word for LTC1090

LABEL

LOOP

MNEMONIC

LD (F0) - 0D

LD (D5)-32

LD (EE)-8

LD (B)-D4

(D(A) - (F0))

| RBIT 1                  | G1 RESET (CS GOES LOW)   |

|-------------------------|--------------------------|

| X (A)                   | LOAD DIN INTO SHIFT REG. |

| LD (B)-EF               | LOAD PSW REG ADDR IN B   |

| SBIT 2                  | TRANSFER BEGINS          |

| NOP                     | 15 NOPs FOR TIMING       |

| X (A)                   | LOAD DOUT INTO ACC       |

| SBIT 2                  | TRANSFER CONTINUES       |

| X (A) (F3)              | LOAD DOUT IN ADDR F3     |

| RBIT 2                  | STOP TRANSFER            |

| LD (B)-D4               | PUT PORT G ADDR IN B     |

| SBIT 1                  | G1 SET (CS GOES HIGH)    |

| X (A)→(E9)              | LOAD DOUT INTO ACC       |

| RC                      | CLEAR CARRY              |

| RRCA                    | SHIFT RIGHT THRU CARRY   |

| RRCA                    | SHIFT RIGHT THRU CARRY   |

| RRCA                    | SHIFT RIGHT THRU CARRY   |

| $X(A) \rightarrow (F4)$ | LOAD DOUT IN ADDR F4     |

|                         |                          |

COMMENTS

CONFIGURE CONTROL REG.

PORT G DATA REG. INTO B

LOAD OD INTO FO (DIN)

CONFIGURE PORT G

LOAD D., INTO ACC.

#### Figure 5. COP820C Code

MICROWIRE shift register are swapped with those of the ACC. The carry is cleared and the data in the ACC is shifted right, through the carry bit three times. This puts the two LSBs of the DOUT word in the MSBs of the ACC. The contents of the ACC are then stored in \$F4. The data at this point is left justified as shown in Figure 4.

44 ACLK cycles must be allowed between transfers for the A/D to perform its next conversion. The instructions, after G1 is set, take enough time so that no additional delay is required by this program.

#### Summary

A four wire interface between the LTC1090 and the COP820C with a combined data conversion and transfer time of 56µs was demonstrated. The interface used the MICROWIRE/PLUS serial port of the COP820C. The 10 data bits of the LTC1090 are shifted MSB first in one eight bit and one two bit transfer. The data is stored left justified in the COP820C's internal RAM.

MICROWIRE and MICROWIRE/PLUS are trademarks of National Semiconductor Corp.

AN26D-2

Application Note 26E

January 1988

## Interfacing the LTC1090 to the TMS7742 MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes an interface between the LTC1090 10-bit data acquisition system and the TMS7000 family of microcomputers (e.g., TMS7742). The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the TMS7742 in 103 $\mu$ s. Configuration of the LTC1090 and the TMS7742 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### Interface Details

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. Data is transferred in a full duplex format over  $D_{IN}$  and  $D_{OUT}$ .

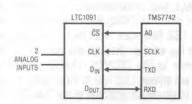

The TMS7742 contains a synchronous, full duplex, serial port that allows the user to construct a simple communication path to the LTC1090. The serial port provides clock, transmit and receive lines that are compatible with the LTC1090. The only additional line required is one pro-

Figure 1. Schematic

grammable output pin (A0) to control  $\overline{\text{CS}}$  on the LTC1090. The schematic of Figure 1 shows how the two devices are connected.

#### Hardware Description

The TMS7742 was chosen because it contains 4k of EPROM which can be programmed using a standard EPROM programmer. Any member of the TMS7000 family which contains a serial port should be able to use this code with only modifications to the peripheral register numbers.

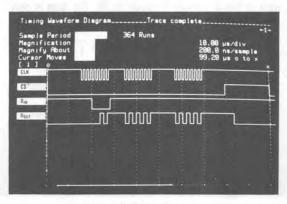

The timing diagram of Figure 2 was obtained using an HP1631A logic analyzer. ACLK of the LTC1090 was 2 MHz and the TMS7742 clock was 5 MHz.

The analog section of the schematic of Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

AN26E-1

## Application Note 26E

#### Software Description

The software configures and controls the serial port of the TMS7742. Additionally, the software manipulates A0 ( $\overline{CS}$  of the LTC1090) and generates a delay during which time the LTC1090 performs a conversion.

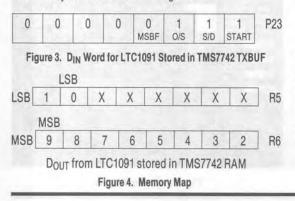

The code first disables all interrupts and initializes the stack. Next the serial port is configured. Tx is enabled, the serial port is reset, and the SMODE register is configured for 8 bits, no parity, and one stop bit. The SCLK rate is set to the processor clock frequency divided by 4. The  $D_{IN}$  word of the LTC1090 is next loaded into the ACC. This  $D_{IN}$  word (\$DF) configures the LTC1090 for CH7 with respect to COM, unipolar mode, LSB first and a 16-bit word length. Examine Figure 3 to see how this is constructed keeping in mind that the TMS7742 transmits data LSB first.

A subroutine SXTNBIT is called next. This is a routine that does the actual data shifting. A0 ( $\overline{CS}$ ) is cleared. Then, the LTC1090 D<sub>IN</sub> word is placed into the transmit buffer. The serial port is turned on and the data is shifted while the processor idles in a loop. The first eight bits containing the LSBs are then placed in the B register. The procedure is repeated for the next eight bits which contain the two MSBs and the result is placed in the A register. A0 ( $\overline{CS}$ ) is then set and the subroutine returns to the original program. The data in the A and B registers is then stored in R5 and R6.

At this time 44 ACLK cycles must be allowed for the A/D to perform its next conversion. Enough time is consumed by this program however that no additional delay for the conversion is required.

AN26E-2

| LABEL   | MM          | EMONIC       | COMMENTS                         |

|---------|-------------|--------------|----------------------------------|

| START   | DINT        |              | DISABLES ALL INTERRUPTS          |

|         | MOVP        | %>2A,P0      | DISABLE INTERRUPT FLAGS          |

|         | MOVP        | %>02,P16     | DISABLE INTERRUPT FLAGS          |

|         | MOV         | %>60,B       | ADDRESS OF STACK                 |

|         | LDSP        |              | PUT ADDRESS INTO POINTER         |

|         | MOVP        | %>DF,P5      | CONFIGURE PORT A                 |

|         | MOVP        | %>08,P6      | ENABLE Tx BY SETTING B3 = 1      |

|         | MOVP        | %>00,P17     | P17 POINTS TO SCTL0              |

|         | MOVP        | %>40,P17     | RESET THE SERIAL PORT            |

|         | MOVP        | %>0C,P17     | CONFIGURE THE SERIAL PORT        |

|         | MOVP        | %>00,P21     | TURN START BIT OFF               |

|         | MOVP        | %>00.P17     | ENABLE THE SERIAL PORT           |

|         | MOVP        | %>00,P20     | SET SCLK RATE (TIMER 3)          |

|         | MOVP        | %>C0.P21     | START TIMER                      |

| LOOP    | MOV         | %>DF.A       | LOAD LTC1090 DIN WORD IN A       |

|         | CALL        | SXTNBIT      | ROUTINE THAT SHIFTS DATA         |

|         | MOV         | B.R5         | PUT FIRST 8 LSBs IN R5           |

|         | MOV         | A,R6         | PUT MSBs IN R6                   |

| SXTNBIT | ANDP        | %>FE,P4      | A0 CLEARED (CS GOES LOW)         |

|         | MOVP        | A,P23        | PUT LTC1090 DIN INTO TXBUF       |

|         | MOVP        | %>40,P21     | SCLK OFF (TIMER 3 DISABLED)      |

|         | MOVP        | %>17,P17     | ENABLE SERIAL PORT               |

|         | MOVP        | %>C0,P21     | SCLK ON (TRANSFER BEGINS)        |

|         | MOVP        | %>14,P17     | TXEN GOES LOW                    |

|         | MOV         | %>02,A       | LOAD COUNTER                     |

| WAIT1   | DJNZ        | A,WAIT1      | LOOP WHILE SHIFT OCCURS          |

|         | NOP         |              | DELAY                            |

|         | MOVP        | P22,B        | PUT DOUT FROM LTC1090 IN B       |

|         | MOVP        | A,P23        | LOAD TXBUF                       |

|         | MOVP        | %>40,P21     | SCLK OFF (TIMER 3 DISABLE)       |

|         | MOVP        | %>17,P17     | ENABLE SERIAL PORT               |

|         | MOVP        | %>C0,P21     | SCLK ON (TRANSFER BEGINS)        |

|         | MOVP        | %>14,P17     | TXEN GOES LOW                    |

|         | MOV         | %>02,A       | LOAD COUNTER                     |

| WAIT2   | DJNZ<br>NOP | A,WAIT2      | LOOP WHILE SHIFT OCCURS<br>DELAY |

|         | MOVP        | P22,A        | PUT DOUT FROM LTC1090 IN A       |

|         | ORP         | %>01,P4      | A0 SET (CS GOES HIGH)            |

|         | RETS        | and a second | RETURN TO MAIN PROGRAM           |

#### Figure 5. TMS7742 Code

#### Summary

A four wire interface between the LTC1090 and the TMS7742 with a combined data conversion and transfer time of  $103\mu$ s was demonstrated. The interface used the serial port of the TMS7742. Because the serial port transfers data LSB first, care must be taken to properly construct the D<sub>IN</sub> word so that the bits are transmitted in the proper order to the LTC1090. The 10 data bits of the LTC1090 are shifted LSB first in two eight bit transfers. The data is stored right justified in the TMS7742's internal RAM.

Application Note 26F

January 1988

# LTC1090

## Interfacing the LTC1090 to the COP402N MCU

Guy Hoover William Rempfer

#### Introduction

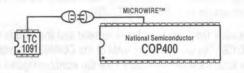

This application note describes the hardware and software required for communication between the LTC1090 10-bit data acquisition system and the National Semiconductor COP400 microcontroller family which uses the MICROWIRE serial interface. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data in 100 $\mu$ s. Configuration of the LTC1090 and the COP402N will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### **Interface Details**

The LTC1090 has two clock lines: ACLK and SCLK. ACLK controls the A/D conversion rate while SCLK controls the data shift rate. Data is transferred in a full duplex format over  $D_{IN}$  and  $D_{OUT}$ .

The National Semiconductor MICROWIRE interface is a synchronous, full duplex, serial port built into the COP400 family that allows the user to easily interface to the LTC1090. MICROWIRE provides clock, data in and data out lines that are compatible with the LTC1090. One addi-

Figure 1. Schematic

tional line (G0) is required to control the  $\overline{CS}$  pin on the LTC1090. The schematic of Figure 1 shows how the two devices are connected.

#### Hardware Description

The actual interface will involve using the COP402N, a member of the COP400 family. All code shown here should work with any of the COP400 family.

The code for this interface was developed on a COP400 evaluation board which allows an external EPROM to be used in place of the internal processor ROM.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer using a 2MHz ACLK. The COP402N clock was 4MHz.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1090 please see the data sheet.

Figure 2. Timing Diagram

AN26F-1

## Application Note 26F

#### Software Description

The software configures and controls the MICROWIRE serial interface of the COP402N. Additionally, the software manipulates G0 ( $\overline{CS}$  of the LTC1090) and generates a delay during which time the LTC1090 performs a conversion.

The code first initializes the B register and then loads the LTC1090  $D_{IN}$  word into the RAM of the COP402 one nibble at a time. As shown in Figure 3 the  $D_{IN}$  word configures the LTC1090 for CH0 with respect to COM, unipolar, MSB first, and 12 bits. SO is configured as an output. The carry is set so that when an XAS instruction is generated the shift clock (SK) will begin clocking data.

The first nibble of the D<sub>IN</sub> word is loaded into the ACC and G0 ( $\overline{CS}$ ) is cleared. The D<sub>IN</sub> nibble is loaded into the shift register and the data begins to shift. The second nibble of the D<sub>IN</sub> word is loaded into the ACC. One NOP is allowed for timing and then the contents of the ACC are swapped with those of the shift register. The MSBs of the LTC1090 D<sub>OUT</sub> word are now in the ACC. This data is then stored in memory location \$13. The ACC is loaded with null data from RAM and another swap between the ACC and the shift register is executed. The next D<sub>OUT</sub> nibble is stored in \$14. The carry is cleared so that on the next XAS instruction the shift clock will stop. The XAS instruction is executed and the final nibble of the LTC1090 D<sub>OUT</sub> word containing the two LSBs and two zeroes is loaded into the

|     | \$  | 10 |    | \$11 |      |     |     |

|-----|-----|----|----|------|------|-----|-----|

| 1   | 0   | 0  | 0  | 1    | 1    | 1   | 0   |

| S/D | O/S | S1 | S2 | UNI  | MSBF | WL1 | WLO |

Figure 3. DIN Word for LTC1090

| <b>ISB</b> |     |    |    |      |

|------------|-----|----|----|------|

| B9         | B8  | B7 | B6 | \$13 |

| B5         | B4  | B3 | B2 | \$14 |

| 00         | LSB | 00 | DZ | φIH  |

| B1         | BO  | 0  | 0  | \$15 |

DOUT from LTC1090 stored in COP402 RAM

Figure 4. Memory Map

| LABEL | MN   | EMONIC | COMMENTS<br>MUST BE FIRST INSTRUCTION |

|-------|------|--------|---------------------------------------|

|       | LBI  | 1.0    | BR = 1 BD = 0 INITIALIZE B REG.       |

|       | STIL | 8      | FIRST DIN NIBBLE IN \$10              |

|       | STII | F      | SECOND DIN NIBBLE IN \$11             |

|       | STIL | 0      | NULL DATA IN \$12, B = \$13           |

|       | LEI  | C      | SET EN TO (1100) BIN                  |

| LOOP  | SC   | 0      | CARRY SET                             |

| LOOI  | LDD  | 1.0    | LOAD FIRST DIN NIBBLE IN ACC          |

|       | OGI  | 50     | G0 (CS) CLEARED                       |

|       | XAS  |        | ACC TO SHIFT REG. BEGIN SHIFT         |

|       | LDD  | 1,1    | LOAD NEXT DIN NIBBLE IN ACC           |

|       | NOP  |        | TIMING                                |

|       | XAS  |        | NEXT NIBBLE, SHIFT CONTINUES          |

|       | XIS  | 0      | FIRST NIBBLE Dout TO \$13             |

|       | LDD  | 1,2    | PUT NULL DATA IN ACC                  |

|       | XAS  |        | SHIFT CONTINUES, DOUT TO ACC          |

|       | XIS  | 0      | NEXT NIBBLE DOUT TO \$14              |

|       | RC   |        | CLEAR CARRY                           |

|       | CLRA |        | CLEAR ACC                             |

|       | XAS  |        | THIRD NIBBLE DOUT TO ACC              |

|       | OGI  | 51     | GO (CS) SET                           |

|       | XIS  | 0      | THIRD NIBBLE DOUT TO \$15             |

|       | LBI  | 1,3    | SET B REG. FOR NEXT LOOP              |

#### Figure 5. COP402 Code

ACC. G0 ( $\overline{CS}$ ) is taken high and the A/D begins its next conversion cycle. The third D<sub>OUT</sub> nibble is stored in location \$15. The B register is then reinitialized so that when the loop is run again the data will always be stored in the same memory locations. The D<sub>OUT</sub> data from the LTC1090 is now in a left justified format as shown in Figure 4.

44 ACLK cycles must be allowed between transfers for the A/D to perform its next conversion. The instructions, after G0 is set, take enough time so that no additional delay is required by this program.

#### Summary

A four wire interface between the LTC1090 and the COP402N with a combined data conversion and transfer time of  $100\mu$ s was demonstrated. The interface used the MICROWIRE serial port of the COP402N. The 10 data bits of the LTC1090 are shifted MSB first in three four bit transfers with the last two bits filled with zeroes. The data is stored left justified in the COP402N's internal RAM. The code demonstrated will work on any member of the COP400 family.

MICROWIRE is a trademark of National Semiconductor Corp.

AN26F-2

Application Note 26G

February 1988

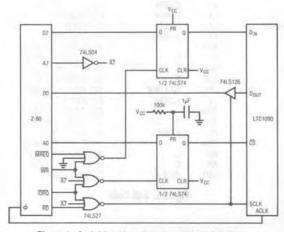

## Interfacing the LTC1091 to the 8051 MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes the hardware and software required for communication between the LTC1091 10-bit data acquisition system and the MCS-51 family of microcontrollers (e.g., 8051). The three wire interface is capable of completing a 10-bit conversion and transferring the data to the 8051 in  $57\mu$ s. Configuration of the 8051 and the LTC1091 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be discussed. Finally, a summary of results including data throughput rates will be provided.

#### **Interface Details**

The serial port of the 8051 does not support the synchronous, half duplex format used by the LTC1091. Therefore it is necessary for the user to construct a serial port using three lines from one of the parallel ports available on the 8051. The lines are set or cleared using the bit manipulation features of the 8051. This provides a very flexible serial port.

The data lines ( $D_{IN}$  and  $D_{OUT}$ ) of the LTC1091 can be tied together as shown in Figure 1. This can be done because

Figure 1. Schematic

the I/O pins on the 8051 can be configured as either inputs or outputs independently of one another during the data transfer.

#### **Hardware Description**

The 8051 was simulated and the code for this interface was developed on an Intel ICE252 emulator.

Due to the weak pullups of the 8051, excess loading should be avoided when examining the output of the microcontroller.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer. The 8051 clock rate was 2MHz. The clock could be run as high as 12MHz yielding the minimum conversion and transfer time of  $57\mu$ s.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

Figure 2. Timing Diagram

AN26G-1

## Application Note 26G

#### Software Description

The software simulates a serial port through bit manipulation instructions of the 8051.

$\overline{\text{CS}}$  is initialized by setting it high. Next the D<sub>IN</sub> word for the LTC1091 is loaded into the accumulator. The LTC1091 is configured for MSB first and CH1 with respect to ground. Note that only the first four most significant bits of the byte loaded into the accumulator are sent to the LTC1091. The four LSBs of the D<sub>IN</sub> word are don't cares.

CS is then cleared and a counter is set to four (the number of bits in the  $D_{IN}$  word). For each of the four  $D_{IN}$  bits the accumulator is shifted left with the MSB going into the carry bit. SCLK is cleared. The carry bit is output to  $D_{IN}$  and SCLK is set. The counter is decremented and checked and if all four bits have been output, P1.2 ( $D_{IN}$  and  $D_{OUT}$ ) is set. This allows the pin to be used as an input now, to read the data in from the LTC1091.

SCLK is then cleared and the counter is set to nine (the first bit shifted out from the LTC1091 is a dummy, so nine shifts are required to fill the first byte.). The eight MSBs are read in the same manner as the  $D_{IN}$  word was output. The eight MSBs are stored in R2 and the remaining two LSBs are read into the accumulator. The LSBs are shifted into the MSBs of the accumulator and the remainder of the accumulator is masked to zeroes. The LSBs are then stored in R3 as shown in Figure 4.  $\overline{CS}$  is then set and the process is completed. At this point the data is left justified.

| LABEL | MNE  | MONIC      | COMMENTS                   |

|-------|------|------------|----------------------------|

| BEGIN | SETB | P1.4       | CS GOES HIGH               |

| AGAIN | MOV  | A, #FFH    | DIN WORD FOR LTC1091       |

|       | CLR  | P1.4       | CS GOES LOW                |

|       | MOV  | R4, #04H   | LOAD COUNTER               |

| LOOP1 | RLC  | A          | ROTATE DIN BIT INTO CARRY  |

|       | CLR  | P1.3       | SCLK GOES LOW              |

|       | MOV  | P1.2, C    | OUTPUT DIN BIT TO LTC1091  |

|       | SETB | P1.3       | SCLK GOES HIGH             |

|       | DJNZ | R4, LOOP 1 | NEXT BIT                   |

|       | MOV  | P1, #04H   | BIT 2 BECOMES AN INPUT     |

|       | CLR  | P1.3       | SCLK GOES LOW              |

|       | MOV  | R4, #09H   | LOAD COUNTER               |

| LOOP  | MOV  | C, P1.2    | READ DATA BIT INTO CARRY   |

|       | RLC  | A          | ROTATE DATA BIT INTO CARRY |

|       | SETB | P1.3       | SCLK GOES HIGH             |

|       | CLR  | P1.3       | SCLK GOES LOW              |

|       | DJNZ | R4, LOOP   | NEXT BIT                   |

|       | MOV  | R2, A      | STORE MSBs IN R2           |

|       | MOV  | C, P1.2    | READ DATA BIT INTO CARRY   |

|       | SETB | P1.3       | SCLK GOES HIGH             |

|       | CLR  | P1.3       | SCLK GOES LOW              |

|       | CLR  | A          | CLEAR ACC                  |

|       | RLC  | A          | ROTATE DATA BIT TO ACC     |

|       | MOV  | C, P1.2    | READ DATA BIT INTO CARRY   |

|       | RRC  | A          | ROTATE RIGHT INTO ACC      |

|       | RRC  | A          | ROTATE RIGHT INTO ACC      |

|       | ANL  | A, #COH    | MASK UNUSED BITS           |

|       | MOV  | R3, A      | STORE LSBs IN R3           |

|       | SETB | P1.4       | CS GOES HIGH               |

Figure 5. Code

#### Summary

A three wire interface between the LTC1091 and the 8051 with a combined data conversion and transfer time of  $57\mu$ s was demonstrated. The data is transferred MSB first and resides in two bytes of the 8051 RAM in a left justified format. The code shown applies to all MCS-51 family members. The same technique can be used on any parallel port processor which allows individual bits to be programmed as inputs or outputs.

AN26G-2

Application Note 26H

## February 1988

## Interfacing the LTC1091 to the MC68HC05 MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes an interface between the LTC1091 10-bit data acquisition system and the Motorola SPI family of single chip microcomputers (e.g., 68HC05). The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the 68HC05 in  $58\mu$ s. Configuration of the LTC1091 and the 68HC05 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given, including data throughput rates.

#### Interface Details

The LTC1091 has one clock line which controls the A/D conversion rate and the data shift rate. Data is transferred in a half duplex, synchronous format over D<sub>IN</sub> and D<sub>OUT</sub>.

The Motorola Serial Peripheral Interface (SPI) is a synchronous, full duplex, serial port built into the 68HC05 that allows the user to construct a simple communication path to the LTC1091. SPI provides clock, data in and data out lines that are compatible with the LTC1091. The only

Figure 1. Schematic

TUNER

additional line required is one programmable output pin (C0) to control  $\overline{CS}$  on the LTC1091. The schematic of Figure 1 shows how the two devices are connected.

#### **Hardware Description**

The 68HC05 was emulated and the code for this interface was developed on a Motorola M68HC05 EVM.

SS (Pin 34) of the 68HC05 must be held high to enable the SPI properly for this interface.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer using a 4MHz clock for the 68HC05.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

Figure 2. Timing Diagram

AN26H-1

## Application Note 26H

#### Software Description

The software configures and controls the SPI of the 68HC05. Additionally, the software manipulates C0 (CS of the LTC1091).

The code first configures the Serial Peripheral Control Register (SPCR) of the SPI. The SPI interrupt is disabled. The SPI outputs are enabled. The SPI is configured as a master. Finally, the SPI clock is set to normally low, for data transfer on the rising edge and for a frequency equal to one fourth the internal processor clock (one eighth the crystal frequency).

Port C is configured as all outputs by placing ones in the data direction register of port C. A  $D_{IN}$  word that configures the LTC1091 for CH1 with respect to ground and MSB first is stored in \$50. Figure 3 shows how the  $D_{IN}$  word is composed. Leading zeroes in the  $D_{IN}$  word are ignored. This makes it easy to position the  $D_{OUT}$  word on exact byte boundaries so that shifting the data to right justify it is not necessary.

C0 is made to go low.  $D_{IN}$  for the LTC1091 is loaded into the SPI data register. Storing  $D_{IN}$  in the data register causes the transfer to begin. The status register of the SPI is tested until the SPIF bit is set which indicates the transfer is finished. Reading the SPI status register clears the SPIF bit and allows the data register to be read, which is the next step. The first eight bits containing the MSBs from the LTC1091 are then stored in \$60 of the 68HC05 as shown in Figure 4. The LSBs are transferred in the same manner and stored in \$61 of the 68HC05.

LABEL MNEMONIC COMMENTS DATA FOR SPCR LDA #\$51 STA \$0A LOAD DATA INTO SPCR LDA #\$FF DATA FOR DDR STA \$06 CONFIGURE PORT C DDR LDA #\$7F DIN WORD FOR LTC1091 STA \$50 PUT DIN WORD IN \$50 START BCLR 0.\$02 CO (CS) GOES LOW LDA PUT DIN WORD IN ACC \$50 STA \$0C START TRANSFER TST TEST IF DONE TEST \$0B BPL TEST IF NOT TRY AGAIN LDA \$0C LOAD MSBs IN ACC STA \$0C START NEXT TRANSFER AND #\$03 MASK UNUSED BITS STA \$60 STORE MSBs IN \$60 TEST1 TST \$0B TEST IF DONE BPL TEST1 IF NOT TRY AGAIN **BSET** 0,\$02 C0 (CS) GOES HIGH LDA \$0C PUT LSBs IN ACC STA \$61 PUT LSBs IN \$61

#### Figure 5. 68HC05 Code

The code was written for the 68HC05. By changing the addresses of the special function registers however, the code should run on all of Motorola's SPI processors including the 68HC11.

#### Summary

A four wire interface between the LTC1091 and the 68HC05 with a combined data conversion and transfer time of  $58\mu$ s was demonstrated. The interface used the serial (SPI) port of the 68HC05. The 10 data bits of the LTC1091 are shifted MSB first in two eight bit transfers. The data is stored left justified in the 68HC05's internal RAM.

AN26H-2

Application Note 26

## February 1988

## Interfacing the LTC1091 to the COP820C MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes the hardware and software required for communication between the LTC1091 10-bit data acquisition system and the National Semiconductor COP800 microcontroller family which uses the MICROWIRE/PLUS serial interface. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data in 45 $\mu$ s. Configuration of the LTC1091 and the COP820C will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### **Interface Details**

The LTC1091 clock line controls the A/D conversion rate and the data shift rate. Data is transferred in a half duplex, synchronous, format over  $D_{IN}$  and  $D_{OUT}$ .

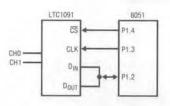

The National Semiconductor MICROWIRE/PLUS is a synchronous, full duplex, serial port built into the COP800 family that allows easy interface to the LTC1091. MICROWIRE/PLUS provides clock, data in and data out lines that are compatible with the LTC1091. One additional line (G1) is required to control the  $\overline{CS}$  pin on the LTC1091. The schematic of Figure 1 shows how the two devices are connected.

#### Figure 1. Schematic

#### Hardware Description

The actual interface was done using the COP820C, a member of the COP800 family. All code shown here should work with any of the COP800 family.

The code for this interface was developed on a COP820 evaluation board operated in the emulation mode.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer. A 5MHz COP820C clock (2 $\mu$ s instruction cycle) was used. By operating the MCU with a 1 $\mu$ s instruction cycle (high speed option) the minimum conversion and transfer time of 45 $\mu$ s is achieved.

The analog section of the schematic in Figure 1 is omitted for clarity, for a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

Figure 2. Timing Diagram

AN261-1

## Application Note 26

#### Software Description

The software configures and controls the MICROWIRE/ PLUS serial interface of the COP820C. Additionally, the software manipulates G1 ( $\overline{CS}$  of the LTC1091).

The code first loads the  $D_{\rm IN}$  word of the LTC1091 into the memory address \$F0. The  $D_{\rm IN}$  word (\$7F) contains a leading zero which is ignored, followed by a start bit. The next two bits configure the LTC1091 for CH1 with respect to ground. The fifth bit configures the A/D for MSB first mode and the remaining three LSBs are ignored as shown in Figure 3.

Next port G is configured such that pin G1 is an output and the MICROWIRE/PLUS serial port is a master. The control register is configured to enable SO and SK. Also the SK divide by is set up in such a way that the SK clock rate is equal to the crystal frequency divided by 20. The address of the port G data register is put into the B register so that the individual bits of port G can be manipulated. G1 ( $\overline{CS}$ ) is then initialized by setting it high.

The D<sub>IN</sub> word is then loaded into the accumulator. G1 is cleared and the LTC1091 D<sub>IN</sub> word is loaded into the MICROWIRE<sup>TM</sup> shift register. The busy bit is set which begins the data transfer. 16 NOPs are used as a timer to allow the transfer to be completed. After the transfer is complete the D<sub>OUT</sub> information is loaded into the accumulator and the next eight bits start to shift. The six MSBs in the accumulator are set to zeroes and the result is stored in \$F3. Nine NOPs are then used to wait until the second eight bits have been shifted. G1 ( $\overline{CS}$ ) is then set and the

| MNEMONIC                | COMMENTS                           |

|-------------------------|------------------------------------|

| LD (F0)-\$7F            | LOAD DIN WORD INTO \$F0            |

| LD (D5)-\$32            | G1 IS OUT, MICROWIRE MASTER        |

| LD (EE)-\$08            | ENABLE SO, SK                      |

| LD (B)-\$D4             | PORT G DATA ADDR INTO B            |

| SBIT 1                  | G1 SET (CS GOES HIGH)              |

| LD (A)-(F0)             | PUT LTC1091 DIN WORD IN ACC        |

| RBIT 1                  | G1 CLEARED (CS GOES LOW)           |

| X (A)→(E9)              | DIN IN MICROWIRE SHIFT REG.        |

| LD (B)-\$EF             | PUT PSW REG. ADDR. INTO B          |

| SBIT 2                  | BUSY BIT SET TRANSFER START        |

| NOP                     | 16 NOPs FOR TIMING                 |

| X (A)                   | LOAD DOUT INTO ACC                 |

| SBIT 2                  | BUSY BIT SET TRANSFER START        |

| AND #03                 | MASK OUT UNUSED BITS               |

| $X(A) \rightarrow (F3)$ | LOAD D <sub>OUT</sub> INTO ADDR F3 |

| NOP                     |                                    |

| LD (B)-\$D4             | PORT G DATA REG. ADDR. IN B        |

| SBIT 1                  | G1 SET (CS GOES HIGH)              |

| X (A)                   | LOAD DOUT INTO ACC                 |

| $X(A) \rightarrow (F4)$ | LOAD LSB INTO ADDR. F4             |

|                         |                                    |

#### Figure 5. Code

data is loaded into the accumulator. The LSBs are then loaded into memory location \$F4. The data at this point is right justified. With the appropriate shift routine the data can be easily left justified.

#### Summary

LABEL

LOOP

A four wire interface between the LTC1091 and the COP820C with a combined data conversion and transfer time of  $45\mu$ s was demonstrated. The interface used the MICROWIRE/PLUS serial port of the COP820C. The 10 data bits of the LTC1091 are shifted MSB first in two eight bit transfers. The data is stored right justified in the COP820C's internal RAM.

MICROWIRE and MICROWIRE/PLUS are trademarks of National Semiconductor Corp.

## January 1988

## Interfacing the LTC1091 to the TMS7742 MCU

Guy Hoover

#### Introduction

This application note describes an interface between the LTC1091 10-bit data acquisition system and the TMS7000 family of microcomputers (e.g., TMS7742). The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the TMS7742 in 99 $\mu$ s. Configuration of the LTC1091 and the TMS7742 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### Interface Details

TLINEAR

The LTC1091 clock line controls the A/D conversion rate and the data shift rate. Data is transferred in a synchronous, half duplex format over D<sub>IN</sub> and D<sub>OUT</sub>.

The TMS7742 contains a synchronous, full duplex, serial port that allows the user to construct a simple communication path to the LTC1091. The serial port provides clock, transmit and receive lines that are compatible with the LTC1091. The only additional line required is one programmable output pin (A0) to control  $\overline{CS}$  on the LTC1091.

Figure 1. Schematic

The schematic of Figure 1 shows how the two devices are connected.

#### **Hardware Description**

The TMS7742 was chosen because it contains 4k of EPROM which can be programmed using a standard EPROM programmer. Any member of the TMS7000 family which contains a serial port should be able to use this code with only modifications to the peripheral register numbers.

The timing diagram of Figure 2 was obtained using an HP1631A logic analyzer. The TMS7742 clock was 5 MHz.

The analog section of the schematic of Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

Figure 2. Timing Diagram

AN26J-1

## Application Note 26J

#### Software Description

The software configures and controls the serial port of the TMS7742. Additionally, the software manipulates A0 ( $\overline{CS}$  of the LTC1091).

The code first disables all interrupts and initializes the stack. The data direction register for the A port then sets A5 (RXD) as an input and all other bits including A0 ( $\overline{CS}$ ) as outputs. Next the serial port is configured. Tx is enabled, the serial port is reset, and the SMODE register is configured for 8 bits, no parity, and one stop bit. The SCLK rate is set to the processor clock frequency divided by 4.

The SCLK is turned off and A0 (CS) is cleared. The DIN word of the LTC1091 is loaded into the TXBUF. This DIN word (07) configures the LTC1091 for CH1 with respect to ground and LSB first. Examine Figure 3 to see how this is constructed keeping in mind that the TMS7742 transmits data LSB first. The serial port and SCLK are turned on and the data is shifted while the processor idles in a loop. The first eight bits contain the DIN word and the first three MSBs of the DOUT word. (The LTC1091 clocks out the data MSB first and then LSB first when in the LSB first mode.) The serial port is turned on again and the next eight bits containing the rest of the MSB first data and the first two bits of the LSB first data are shifted while the processor idles in a loop. The data containing the LSBs is then placed in the B register. The procedure is repeated for the next eight bits which contain the MSBs and the result is placed in the A register. A0 (CS) is then set. The data in the B register is stored in R5. If desired the lowest six bits of the B register can be cleared by adding them with \$C0. The data in the A register is stored in R6. The data is now stored left justified as shown in Figure 4.

AN26J-2

| LABEL | MA   | EMONIC   | COMMENTS                               |

|-------|------|----------|----------------------------------------|

| START | DINT | Linomo   | DISABLES ALL INTERRUPTS                |

|       | MOVP | %>2A.P0  | DISABLE INTERRUPT FLAGS                |

|       | MOVP | %>02.P16 | DISABLE INTERRUPT FLAGS                |

|       | MOV  | %>60.B   | ADDRESS OF STACK                       |

|       | LDSP |          | PUT ADDRESS INTO POINTER               |

|       | MOVP | %>DF.P5  | CONFIGURE PORT A                       |

|       | MOVP | %>08,P6  | ENABLE Tx BY SETTING B3 = 1            |

|       | MOVP | %>00,P17 | P17 POINTS TO SCTL0                    |

|       | MOVP | %>40,P17 | RESET THE SERIAL PORT                  |

|       | MOVP | %>0C,P17 | CONFIGURE THE SERIAL PORT              |

|       | MOVP | %>00,P21 | TURN START BIT OFF                     |

|       | MOVP | %>00,P17 | ENABLE THE SERIAL PORT                 |

|       | MOVP | %>00,P20 | SET SCLK RATE (TIMER 3)                |

| LOOP  | MOVP | %>40,P21 | SCLK OFF                               |

|       | ANDP | %>FE,P4  | A0 CLEARED (CS GOES LOW)               |

|       | MOVP | %>07,P23 | PUT LTC1091 DIN INTO TXBUF             |

|       | MOVP | %>17,P17 | ENABLE SERIAL PORT                     |

|       | MOVP | %>C0,P21 | SCLK ON (TRANSFER BEGINS)              |

|       | MOVP | %>14,P17 | TXEN GOES LOW                          |

|       | MOV  | %>02,A   | LOAD COUNTER                           |

| WAIT  | DJNZ | A,WAIT   | LOOP WHILE SHIFT OCCURS                |

|       | NOP  |          | MORE DELAY                             |

|       | MOVP | %>17,P17 | ENABLE SERIAL PORT                     |

|       | MOVP | %>14,P17 | TXEN GOES LOW                          |

|       | MOV  | %>02,A   | LOAD COUNTER                           |

| WAIT1 | DJNZ | A,WAIT1  | LOOP WHILE SHIFT OCCURS                |

|       | NOP  |          | DELAY                                  |

|       | MOVP | P22,B    | PUT D <sub>OUT</sub> FROM LTC1091 IN B |

|       | MOVP | %>17,P17 | ENABLE SERIAL PORT                     |

|       | MOVP | %>14,P17 | TXEN GOES LOW                          |

|       | MOV  | %>02,A   | LOAD COUNTER                           |

| WAIT2 | DJNZ | A,WAIT2  | LOOP WHILE SHIFT OCCURS<br>DELAY       |

|       | MOVP | P22,A    | PUT DOUT FROM LTC1091 IN A             |

|       | ORP  | %>01,P4  | A0 SET (CS GOES HIGH)                  |

|       | MOV  | B,R5     | PUT FIRST 2 LSBs IN R5                 |

|       | MOV  | A,R6     | PUT MSBs IN R6                         |

#### Figure 5. TMS7742 Code

#### Summary

A four wire interface between the LTC1091 and the TMS7742 with a combined data conversion and transfer time of  $99_{\mu}s$  was demonstrated. The interface used the serial port of the TMS7742. Because the serial port transfers data LSB first, care must be taken to properly construct the D<sub>IN</sub> word so that the bits are transmitted in the proper order to the LTC1091. The 10 data bits of the LTC1091 are shifted LSB first in three eight bit transfers. The data is stored left justified in the TMS7742's internal RAM.

January 1988

## Interfacing the LTC1091 to the COP402N MCU

Guy Hoover

#### Introduction

This application note describes the hardware and software required for communication between the LTC1091 10-bit data acquisition system and the National Semiconductor COP400 microcontroller family which uses the MICROWIRE serial interface. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data in 116 $\mu$ s. Configuration of the LTC1091 and the COP402N will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### **Interface Details**

The LTC1091 clock line controls the A/D conversion rate and the data shift rate. Data is transferred in a half duplex format over  $D_{IN}$  and  $D_{OUT}$ .

The National Semiconductor MICROWIRE interface is a synchronous, full duplex, serial port built into the COP400 family that allows the user to easily interface to the LTC1091. MICROWIRE provides clock, data in and data out lines that are compatible with the LTC1091. One addi-

Figure 1. Schematic

tional line (G0) is required to control the CS pin on the LTC1091. The schematic of Figure 1 shows how the two devices are connected.

#### **Hardware Description**

The actual interface will involve using the COP402N, a member of the COP400 family. All code shown here should work with any of the COP400 family.

The code for this interface was developed on a COP400 evaluation board which allows an external EPROM to be used in place of the internal processor ROM.

The timing diagram of Figure 2 was obtained with an HP1631A logic analyzer. The COP402N clock was 4MHz.

The analog section of the schematic in Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

Figure 2. Timing Diagram

## Application Note 26K

#### Software Description

The software configures and controls the MICROWIRE serial interface of the COP402N. Additionally, the software manipulates G0 (CS of the LTC1091).

The code first initializes the B register and then loads the LTC1091  $D_{IN}$  word into the RAM of the COP402 one nibble at a time. As shown in Figure 3 the  $D_{IN}$  word configures the LTC1091 for CH1 with respect to GND and MSB first. SO is configured as an output. The carry is set so that when an XAS instruction is generated the shift clock (SK) will begin clocking data.

The first nibble of the  $D_{IN}$  word is loaded into the ACC and G0 ( $\overline{CS}$ ) is cleared. The  $D_{IN}$  nibble is loaded into the shift register and the data begins to shift. The second nibble of the  $D_{IN}$  word is loaded into the ACC. One NOP is allowed for timing and then the contents of the ACC are swapped with those of the shift register. The transfer continues. One NOP is allowed for timing. The second  $D_{IN}$  nibble is loaded into the ACC again and the contents of the ACC are swapped with those of the shift register. The MSBs of the LTC1091  $D_{OUT}$  word are now in the ACC. This data is then stored in memory location \$13. The ACC is loaded with the second  $D_{IN}$  nibble from RAM and another swap

|   | \$1        | 1        |          |           |   | \$ | 12 |

|---|------------|----------|----------|-----------|---|----|----|

| 0 | 1<br>START | 1<br>S/D | 1<br>0/s | 1<br>MSBF | 0 | 0  | 0  |

Figure 3. DIN Word for LTC1090

DOUT from LTC1091 stored in COP402 RAM

Figure 4. Memory Map

| MN   | EMONIC | COMMENTS<br>MUST BE FIRST INSTRUCTION |

|------|--------|---------------------------------------|

| LBI  |        | BR = 1 BD = 1 INITIALIZE B REG.       |

| STIL | 1,1    | FIRST DIN NIBBLE IN \$11              |

|      |        |                                       |

| STIL | 8      | SECOND DIN NIBBLE IN \$12             |

| LEI  | 8      | SET EN TO (1000) BIN                  |

| SC   | A      | CARRY SET                             |

| LDD  | 1,1    | LOAD FIRST DIN NIBBLE IN ACC          |

| OGI  | 50     | G0 (CS) CLEARED                       |

| XAS  |        | ACC TO SHIFT REG. BEGIN SHIFT         |

| LDD  | 1,2    | LOAD NEXT DIN NIBBLE IN ACC           |

| NOP  |        | TIMING                                |

| XAS  |        | NEXT NIBBLE, SHIFT CONTINUES          |

| NOP  |        | TIMING                                |

| LDD  | 1.2    | LOAD NULL DATA IN ACC                 |

| XAS  |        | NEXT NIBBLE, SHIFT CONTINUES          |

| XIS  | 0      | FIRST NIBBLE Dout TO \$13             |

| LDD  | 1.2    | LOAD NULL DATA IN ACC                 |

| XAS  |        | SHIFT CONTINUES, DOUT - ACC           |

| XIS  | 0      | NEXT NIBBLE DOUT TO \$14              |

| RC   |        | CLEAR CARRY                           |

| CLRA |        | CLEAR ACC                             |

| XAS  |        | THIRD NIBBLE DOUT TO ACC              |

| OGI  | 51     | G0 (CS) SET                           |

| XIS  | 0      | THIRD NIBBLE DOUT TO \$15             |

| LBI  | 1.3    | SET B REG. FOR NEXT LOOP              |

| LDI  | 1,0    | SET BINES, FOR NEXT LOOP              |

|      |        |                                       |

#### Figure 5. COP402 Code

between the ACC and the shift register is executed. The next  $D_{OUT}$  nibble is stored in \$14. The carry is cleared so that on the next XAS instruction the shift clock will stop. The XAS instruction is executed and the final nibble of the LTC1091  $D_{OUT}$  word containing the LSBs is loaded into the ACC. G0 ( $\overline{CS}$ ) is taken high. The third  $D_{OUT}$  nibble is stored in location \$15. The B register is then reinitialized so that when the loop is run again the data will always be stored in the same memory locations. The  $D_{OUT}$  data from the LTC1091 is now in a right justified format as shown in Figure 4.

#### Summary

LABEL

A four wire interface between the LTC1091 and the COP402N with a combined data conversion and transfer time of  $116\mu$ s was demonstrated. The interface used the MICROWIRE serial port of the COP402N. The 10 data bits of the LTC1091 are shifted MSB first in four four bit transfers. The data is stored right justified in the COP402N's internal RAM. The code demonstrated will work on any member of the COP400 family.

MICROWIRE is a trademark of National Semiconductor Corp.

AN26K-2

Application Note 26L

January 1988

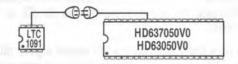

## Interfacing the LTC 1091 to the HD637050 MCU

Guy Hoover William Rempfer

#### Introduction

This application note describes an interface between the LTC1091 10-bit data acquisition system and the Hitachi 63705 microcomputer. The simple four wire interface is capable of completing a 10-bit conversion and shifting the data to the 63705 in  $84\mu$ s. Configuration of the LTC1091 and the 63705 will be discussed as it applies to this interface. Schematics, code, and timing diagrams will be shown. Finally, a summary of the key points of this interface will be given including data throughput rates.

#### **Interface Details**

The LTC1091 clock line controls the A/D conversion rate and the data shift rate. Data is transferred in a half duplex synchronous format over  $D_{IN}$  and  $D_{OUT}$ .

The Hitachi Serial Communication Interface (SCI) is a synchronous, full duplex, serial port built into the 63705 that allows the user to construct a simple communication path to the LTC1091. SCI provides clock, transmit and receive lines that are compatible with the LTC1091. The only additional line required is one programmable output pin

Figure 1. Schematic

LINEAR

(C0) to control CS on the LTC1091. The schematic of Figure 1 shows how the two devices are connected.

#### **Hardware Description**

The 63705VOC was chosen for this application because it contains 4k bytes of EPROM which can be programmed by a 27256 EPROM programmer. The code shown will work on the 6305VO without modification.

The timing diagram of Figure 2 was obtained using an HP1631A logic analyzer. The 63705 clock was 4 MHz.

The analog section of the schematic of Figure 1 is omitted for clarity. For a complete discussion of the analog considerations involved in using the LTC1091 please see the data sheet.

AN26L-1

## Application Note 26L

#### Software Description

The software configures and controls the SCI of the 63705. Additionally, the software manipulates C0 ( $\overline{\text{CS}}$  of the LTC1091).

The code first configures the SCI control register (SCR). D3 and D4 are set as the SCI output and input respectively. D5 is selected as a clock output with a frequency one eighth the crystal frequency. Next, the SCI status register (SSR) is configured so that the interrupts are disabled. Data is transmitted on the falling edge of the clock and received on the rising edge of the clock.

Bit 0 of Port C is configured as an output by setting the first bit of the data direction register (address \$06) to one. A  $D_{IN}$  word that configures the LTC1091 for CH1 with respect to ground and LSB first is stored in \$50. Figure 3 shows how the  $D_{IN}$  word is composed. Note, that for LSB first format the  $D_{IN}$  word must be constructed opposite from MSB first format.

C0 is made to go low. D<sub>IN</sub> for the LTC1091 is loaded into the SCI data register (SDR). Storing D<sub>IN</sub> in the SDR causes the transfer to begin. When LSB first is selected, the LTC1091 first clocks out the data MSB first and then clocks out the data LSB first. After waiting for the first eight bits to be transferred the data containing the MSBs is loaded into the ACC. This starts the next transfer. The next eight bits are then shifted out and the first two LSBs from the LTC1091 are loaded into the accumulator and then stored in \$61 of the 63705 RAM. The act of reading the

AN26L-2

| LABEL | M    | NEMONIC | COMMENTS                                    |

|-------|------|---------|---------------------------------------------|

|       | LDA  | #\$E1   | CONFIGURATION DATA FOR SCR                  |

|       | STA  | \$10    | LOAD DATA INTO SCR (\$10)                   |

|       | LDA  | #\$30   | CONFIGURATION DATA FOR SSR                  |

|       | STA  | \$11    | LOAD DATA INTO SSR (\$11)                   |

|       | LDA  | #\$01   | CONFIG. DATA FOR PORT C DDR                 |

|       | STA  | \$06    | LOAD DATA INTO PORT C DDR                   |

|       | LDA  | #\$07   | LOAD LTC1091 DIN DATA INTO ACC              |

|       | STA  | \$50    | LOAD LTC1091 D <sub>IN</sub> DATA INTO \$50 |

| LOOP  | LDA  | \$50    | LOAD DIN INTO ACC FROM \$50                 |

|       | BCLR | 0,\$02  | CO GOES LOW (CS GOES LOW)                   |