## Synchronous pulsing cuts three-phase motor's dissipation

by D. J. Greenland Cambridge, England

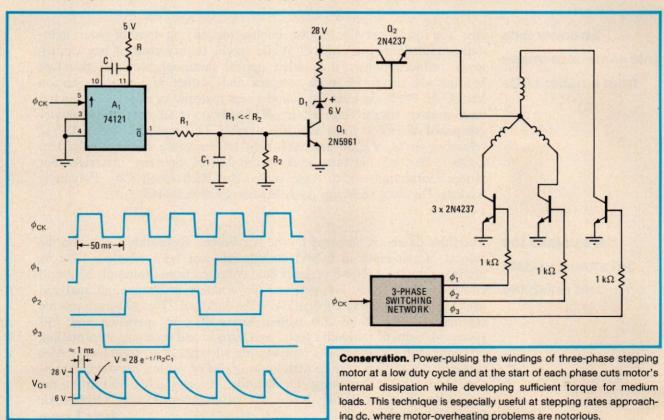

At very low clock rates, below 20 hertz, the windings of a three-phase motor dissipate excessive power. But this problem may be overcome if the motor is not heavily loaded—that is, the torque is less than 20 gramcentimeters. The circuit described here momentarily switches on the motor's supply line synchronously with the phase-generator clock pulse that activates each winding in sequence. Pulsing the windings at a low duty cycle and at the start of each phase increases circuit efficiency, yet enables the motor to develop sufficient torque.

Consider the savings in power. If each winding has a dc resistance of 15 ohms and is periodically energized from a 28-volt source, the power dissipated by each winding as the clock rate approaches zero is  $P = (28)^2/15$ , or 52.26, watts. Even when working at 20 hertz, or a 50-millisecond period, each winding would be energized for the same 50 ms or so and the power consumed per phase would be  $P = (28^2/15)(50)(10^{-3})$

= 2.61 w. But if the energizing time can be reduced to 1 ms, say, the power consumed will be  $P = (28^2/15)(1)(10^{-3}) = 52.26$  milliwatts.

The energizing time,  $T_c$ , is controlled by elements R and C of the 74121 monostable multivibrator,  $A_1$ , as shown in the figure. The one-shot is driven by the same phase generator clock,  $\phi_{CK}$ , that also drives the three-phase switching circuit. (Since many well-known arrangements exist for deriving the required phase voltages for the windings, the actual schematic for the network is not shown here.)

$A_1$  fires on the positive edge of  $\phi_{CK}$  and generates a 1-ms pulse that charges  $C_1$ , switches  $Q_1$ , and brings its collector to 28 v.  $Q_2$  then turns on, driving the particular windings that happen to be activated at that instant by the switching network. The  $\overline{Q}$  output of  $A_1$  then moves back to 1 after the 1-ms interval and  $C_1$  discharges through  $R_2$  exponentially.  $C_1$ ,  $R_1$ , and  $R_2$  are selected once the frequency of  $\phi_{CK}$ , R, and C are known.

It should be mentioned that at clock rates above 1 kilohertz, this circuit offers no power-saving advantage. This is because the period of 1-kHz waveform is 1 ms, comparable to the duty cycle required to reduce the dissipation for the 20-Hz clock previously discussed.

Engineer's notebook is a regular feature in *Electronics*. We invite readers to submit original design shortcuts, calculation aids, measurement and test techniques, and other ideas for saving engineering time or cost. We'll pay \$50 for each item published.