TEXAS Instruments Incorporated The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor-Components Division

# Circuit Design for Audio, AM/FM, and TV

Circuit Design for Audio, AM/FM, and TV

cGraw-Hill 63740

621.3.317

Texas Instruments Electronics Series McGraw-Hill Book Company

### CIRCUIT DESIGN FOR AUDIO, AM / FM, AND TV

#### By the Engineering Staff of TEXAS INSTRUMENTS INCORPORATED

Here is the fifth book in the popular Texas Instruments Electronics Series which brings you the latest advances in electronic design and application. This volume deals with circuit design in the audio, AM/FM, and television areas and represents the results of several years of research and development by TI communications applications engineers. Based on two earlier books originally published as part of the Texas Instruments Microlibrary, the present onevolume edition is an updated version detailing the most current techniques and newest devices available.

This practical guide for the circuit designer emphasizes time- and cost-saving procedures throughout. Design examples have been chosen to suggest the broad application of the procedures: in the television section, specific design examples are given for each major system comprising a television receiver. In the AM/FM section, the stress is on the

(continued on back flap)

621.38171

9.70

#### TEXAS INSTRUMENTS ELECTRONICS SERIES

The Engineering Staff of Texas Instruments Incorporated . CIRCUIT DESIGN FOR AUDIO, AM/FM, AND TV The Engineering Staff of Texas Instruments Incorporated

SOLID-STATE COMMUNICATIONS The Engineering Staff of Texas Instruments Incorporated

TRANSISTOR CIRCUIT DESIGN Runyan SILICON SEMICONDUCTOR TECHNOLOGY

Sevin = FIELD-EFFECT TRANSISTORS

Prepared by the Engineering Staff of Texas Instruments Incorporated

Edited by Wm. A. Stover Technical Publications

#### Contributors

K. G. Cherry R. C. Grimes W. C. Harrison R. S. Henley S. H. Kuehler D. N. Leonard D. E. Pippenger M. P. Schreiner R. E. Smith S. M. Weaver D. W. Whitten D. L. Wilcox

#### CIRCUIT DESIGN FOR AUDIO, AM/FM, AND TV

Copyright © 1967 by Texas Instruments Incorporated. All Rights Reserved. Printed in the United States of America. This book, or parts thereof, may not be reproduced in any form without permission of Texas Instruments Incorporated. *Library of Congress Catalog Card Number* 67-12332.

63740

#### 234567890-HDMB-987

Information contained in this book is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others which may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

#### Preface

v

This book was originally published by the Texas Instruments Microlibrary as two separate paperback books, "Audio and AM/FM Circuit Design Handbook" and "Television Circuit Design Handbook." The result of several years of research and development by Texas Instruments communications applications engineers; the book provides a practical guide for practicing circuit designers and a valuable supplemental text for the advanced engineering student.

Time- and cost-saving procedures have been stressed throughout. Design examples have been chosen to suggest the broad application of the procedures. Inquiries regarding material in this book may be addressed to Communications Applications Branch, Semiconductor-Components Division, Texas Instruments Incorporated, Post Office Box 5012, Dallas, Texas 75222.

> Texas Instruments Incorporated Semiconductor-Components Division

### Contents

|            | Preface                                                                                                                                                                                                                                                                                                                                           | v                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| PART I     | AUDIO DESIGN                                                                                                                                                                                                                                                                                                                                      | 1                                      |

| Chapter 1. | Audio Design Considerations                                                                                                                                                                                                                                                                                                                       | 3                                      |

|            | Amplifier Circuit Selection<br>Transistor Selection<br>Symbols<br>Bibliography                                                                                                                                                                                                                                                                    | 3<br>4<br>6<br>8                       |

| Chapter 2. | Class A Output and Driver Design Procedures                                                                                                                                                                                                                                                                                                       | 9                                      |

|            | Transformer-coupled Input, Transformer-coupled Output<br>RC-coupled Input, Transformer-coupled Output<br>Direct-coupled Input, Direct-coupled Output<br>Direct-coupled Input, Transformer-coupled Output                                                                                                                                          | 9<br>17<br>23<br>29                    |

| Chapter 3. | Class B Output and Driver Design Procedures                                                                                                                                                                                                                                                                                                       | 35                                     |

|            | Transformer-coupled Input, Transformer-coupled Output<br>Transformer-coupled Input, RC-coupled Output                                                                                                                                                                                                                                             | 35<br>42                               |

| Chapter 4. | Class A Design Examples                                                                                                                                                                                                                                                                                                                           | 51                                     |

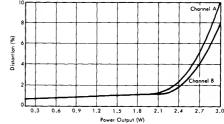

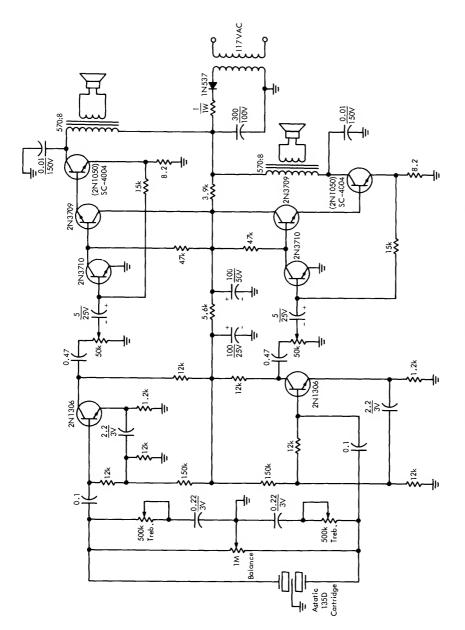

|            | Three-watt Transformer-coupled Input, Transformer-coupled<br>Output<br>One-watt RC-coupled Input, Transformer-coupled Output<br>One-hundred-milliwatt Direct-coupled Input, Direct-coupled<br>Output<br>Additional Class A Amplifiers<br>2-watt Amplifier<br>850-milliwatts-per-channel Stereo Amplifiers<br>3-watts-per-channel Stereo Amplifier | 51<br>57<br>63<br>70<br>70<br>71<br>72 |

|            |                                                                                                                                                                                                                                                                                                                                                   | vii                                    |

#### viii Contents

| Chapter 5. | Class B Design Examples                                               | 75         |

|------------|-----------------------------------------------------------------------|------------|

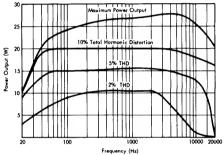

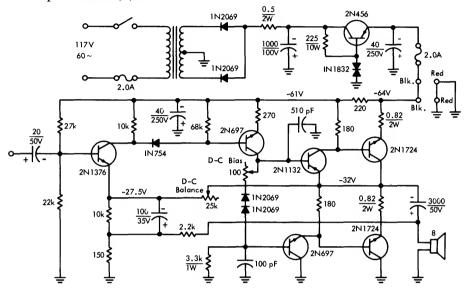

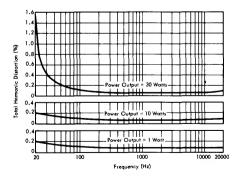

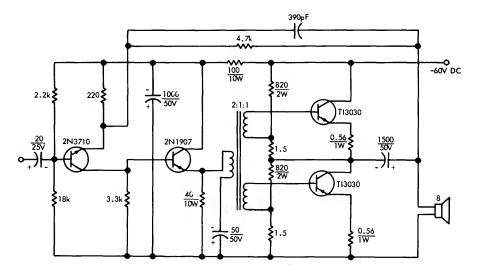

|            | Fifteen-watt Transformer-coupled Input, Transformer-coupled<br>Output | 75         |

|            | Ninety-five-watt Transformer-coupled Input, RC-coupled Output         | 81         |

|            | Additional Class B Amplifiers                                         | 88         |

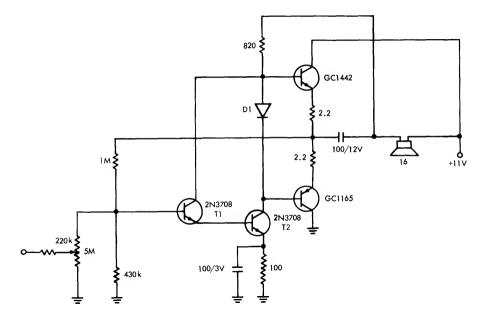

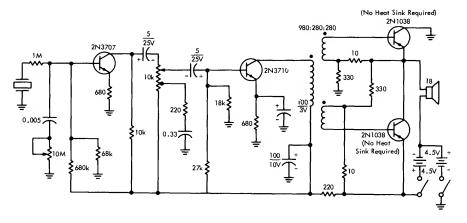

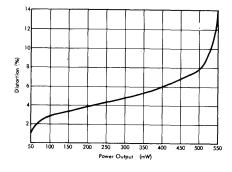

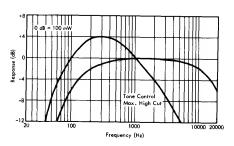

|            | 500-milliwatt Complementary-symmetry Amplifier                        | 88         |

|            | 500-milliwatt Amplifier                                               | 89         |

|            | 2-watt Amplifier                                                      | 90         |

|            | 8-watt Amplifier                                                      | 91         |

|            | 15-watt Amplifier                                                     | 92         |

|            | 30-watt Amplifier                                                     | 94         |

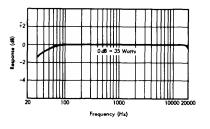

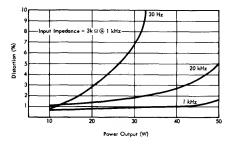

|            | 50-watt Amplifier                                                     | 95         |

| Chapter 6. | Audio Design Equation Derivations                                     | 97         |

| anapro. a. |                                                                       |            |

|            | Class A (Chapter 2)                                                   | 97         |

|            | Class B (Chapter 3)                                                   | 103        |

| PART II    | AM/FM DESIGN                                                          | 109        |

|            |                                                                       |            |

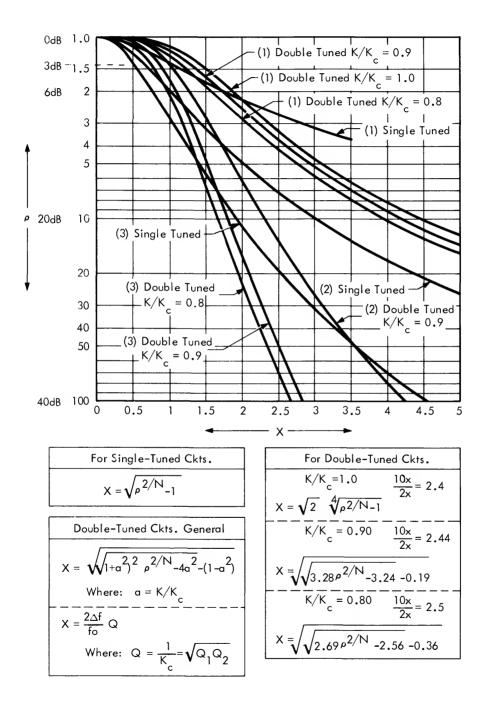

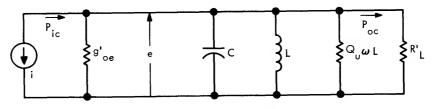

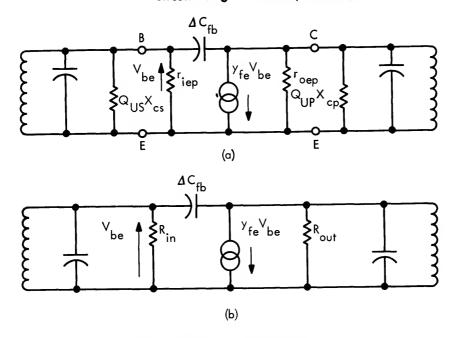

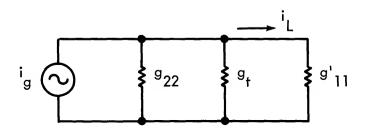

| Chapter 7. | AM IF Amplifier Design                                                | 111        |

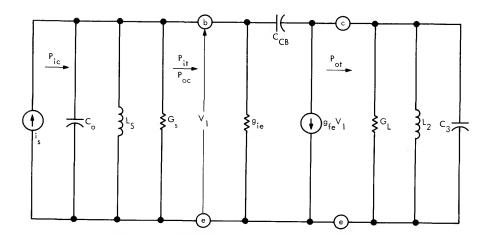

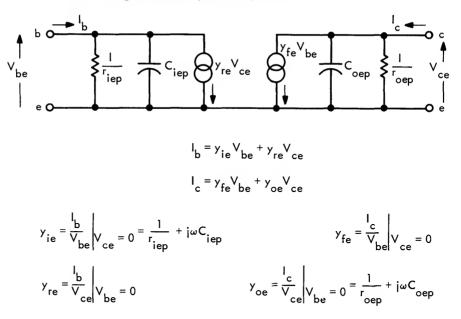

|            | Transistor Model                                                      | 111        |

|            | Single-tuned Circuits                                                 | 113        |

|            | Transformer Loss                                                      | 113        |

|            | Stage Gain                                                            | 113        |

|            | Stable Stage Gain                                                     | 113        |

|            | Bandwidth                                                             | 115        |

|            | Large-signal Handling Ability<br>Design Method                        | 115<br>117 |

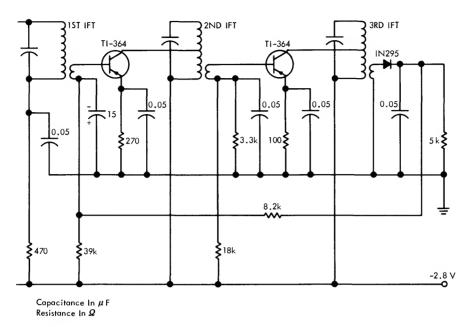

|            | Design Example                                                        | 119        |

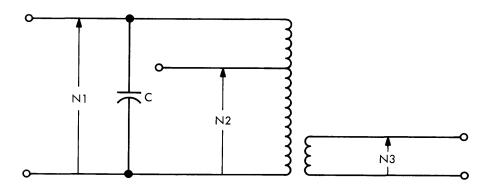

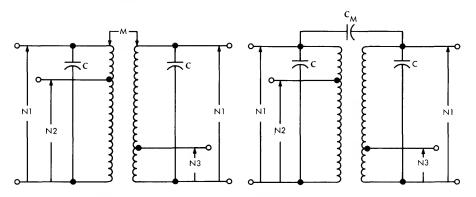

|            | Double-tuned Circuits                                                 | 123        |

|            | Stage Power Gain                                                      | 124        |

|            | Parameter Limits for Design                                           | 124        |

|            | Large-signal Handling Ability                                         | 125        |

|            | Design Method                                                         | 125        |

|            | Design Example                                                        | 127        |

|            | Equation Derivations                                                  | 132        |

|            | Symbols                                                               | 137<br>139 |

|            | References                                                            | 109        |

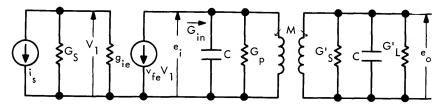

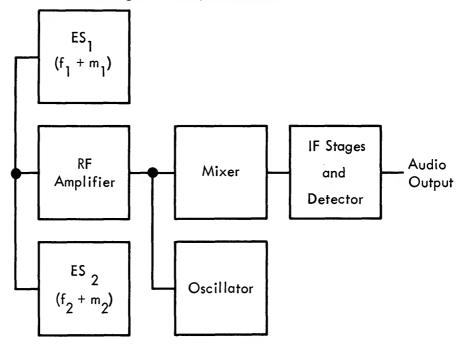

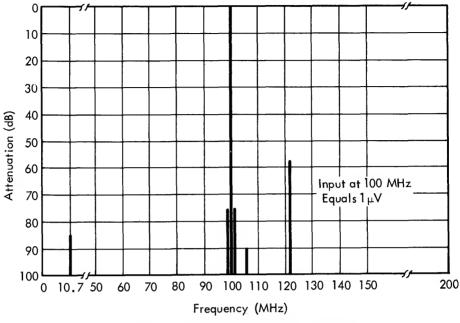

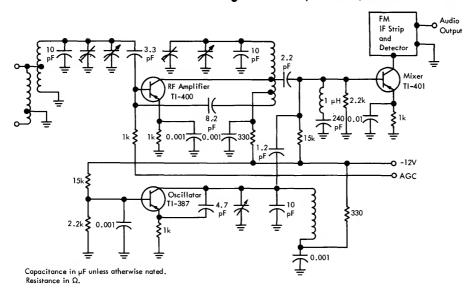

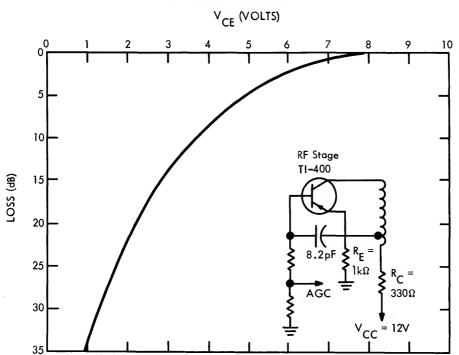

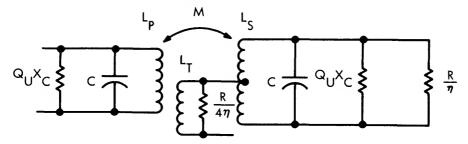

| Chapter 8. | FM Tuner Design                                                       | 141        |

|            | Noise Performance                                                     | 141        |

|            | Spurious Response                                                     | 142        |

| Conten | ts | íx |

|--------|----|----|

|--------|----|----|

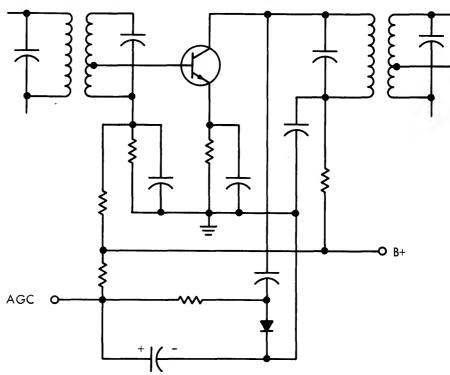

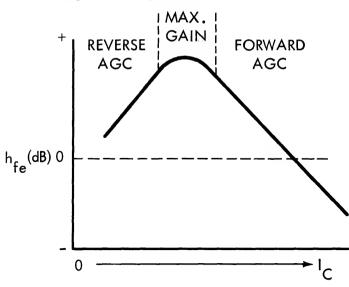

|         |     | Automatic Gain Control<br>Reverse AGC<br>Forward AGC<br>Specifications for FM Tuner Transistors | 146<br>146<br>146<br>148 |

|---------|-----|-------------------------------------------------------------------------------------------------|--------------------------|

|         |     | References                                                                                      | 149                      |

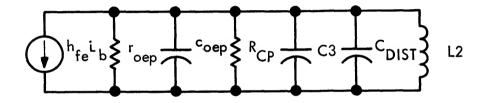

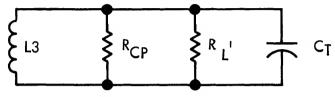

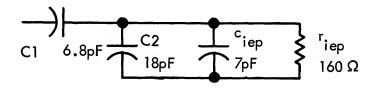

| Chapter | 9.  | FM IF Amplifier Design                                                                          | 151                      |

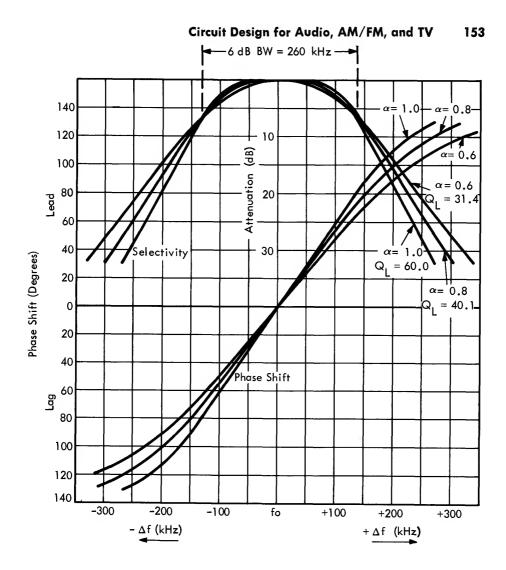

|         |     | Amplitude Response                                                                              | 151                      |

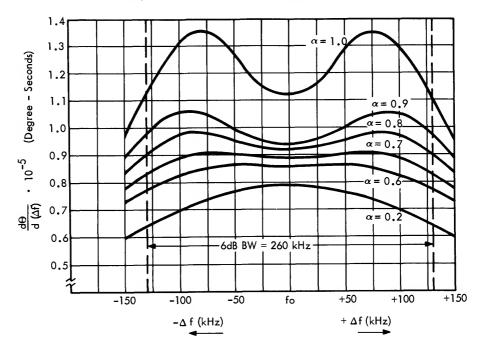

|         |     | Phase Response                                                                                  | 152                      |

|         |     | Design Equations                                                                                | 164                      |

|         |     | Design Procedures                                                                               | 169                      |

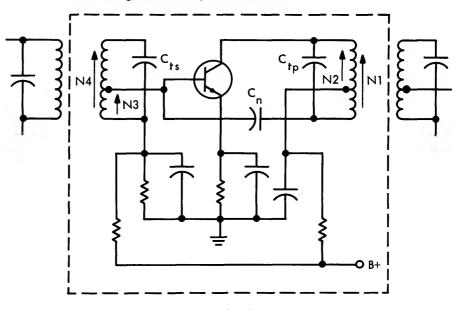

|         |     | Neutralized Procedure                                                                           | 169                      |

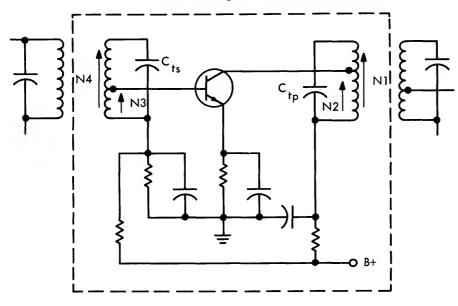

|         |     | Unneutralized Procedure                                                                         | 171                      |

|         |     | Design Examples                                                                                 | 171                      |

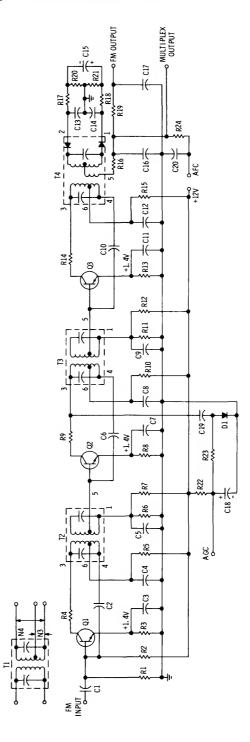

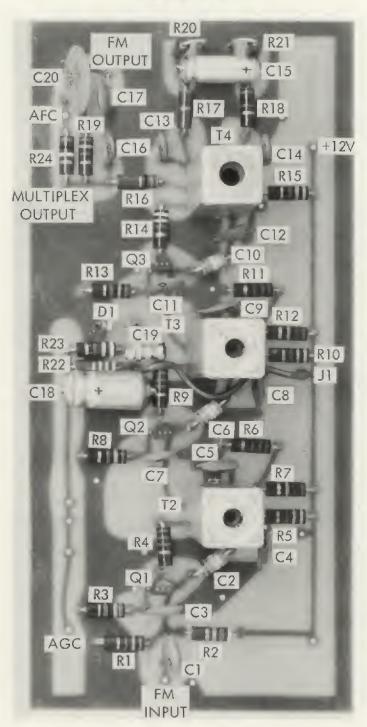

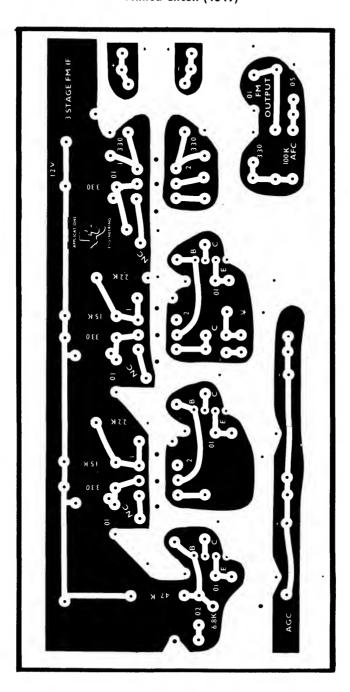

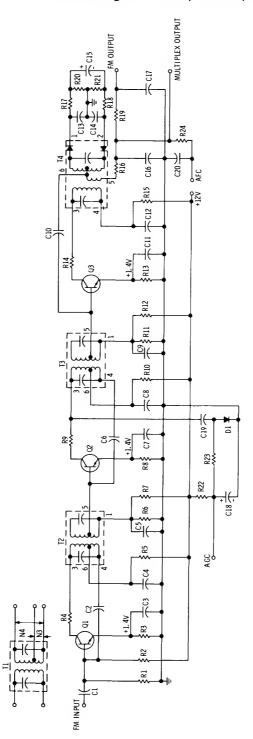

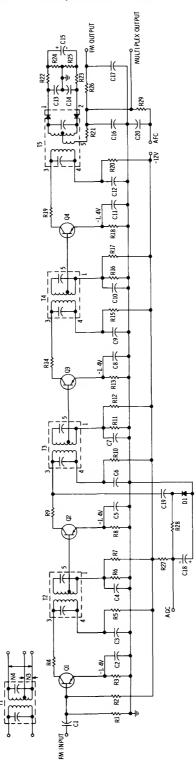

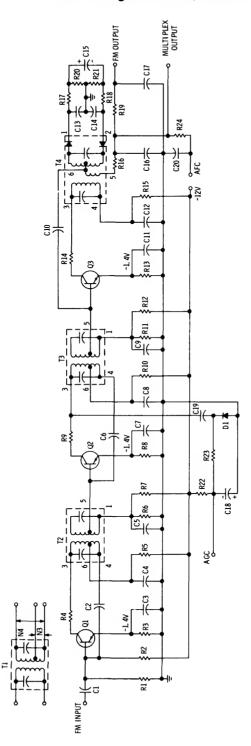

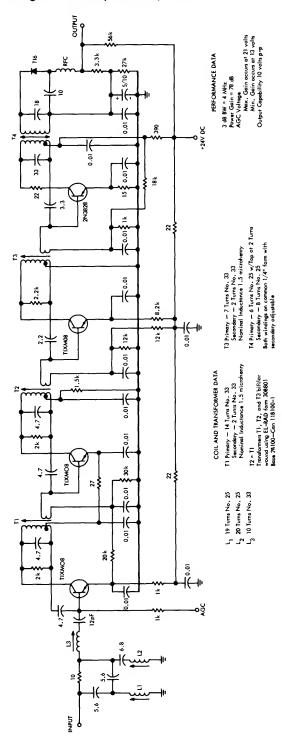

|         |     | Four-stage Neutralized 10.7-MHz IF Amplifier                                                    | 171                      |

|         |     | Three-stage Unneutralized 10.7-MHz IF Amplifier                                                 | 175                      |

|         |     | Equation Derivations                                                                            | 177                      |

|         |     | Symbols                                                                                         | 181                      |

|         |     | References                                                                                      | 182                      |

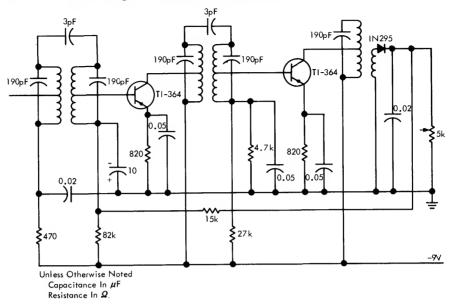

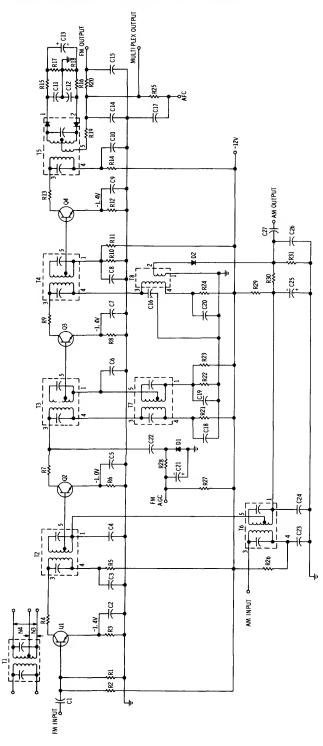

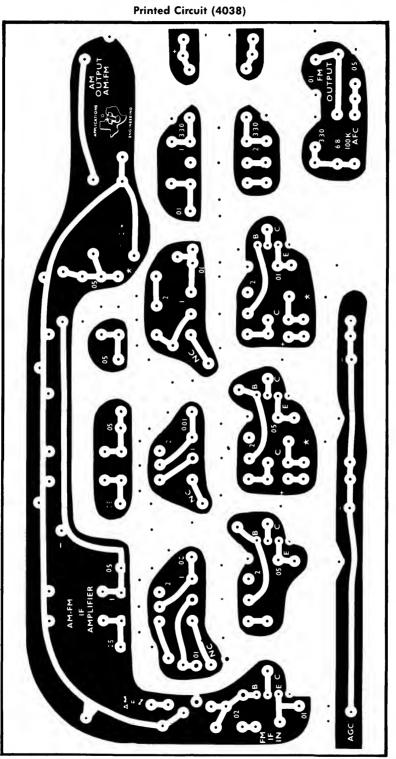

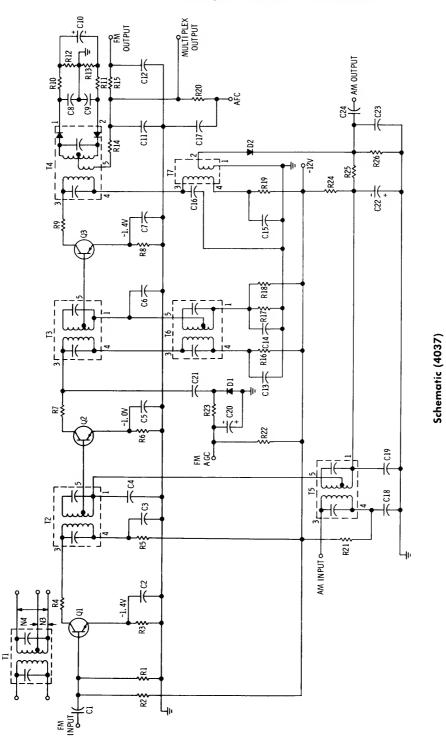

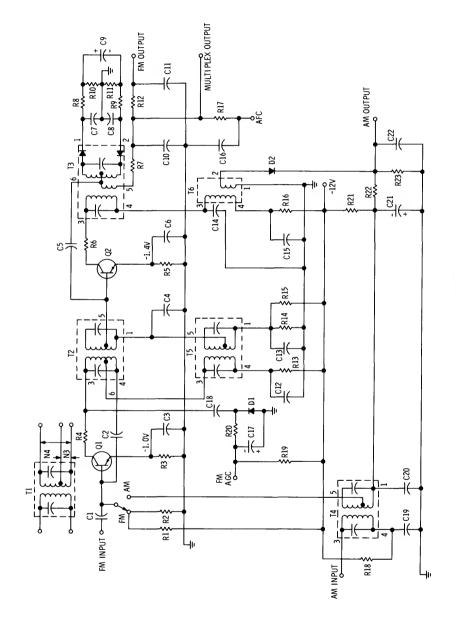

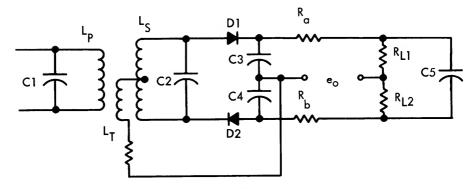

| Chapter | 10. | AM/FM IF Amplifier Circuit Applications                                                         | 183                      |

|         |     | Introduction                                                                                    | 183                      |

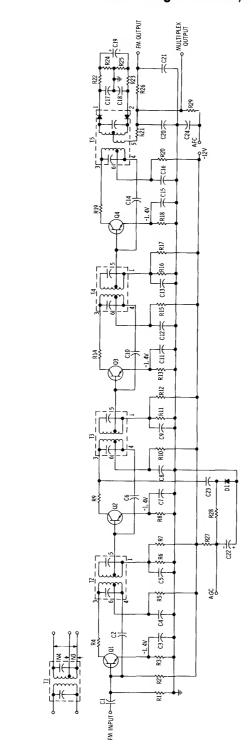

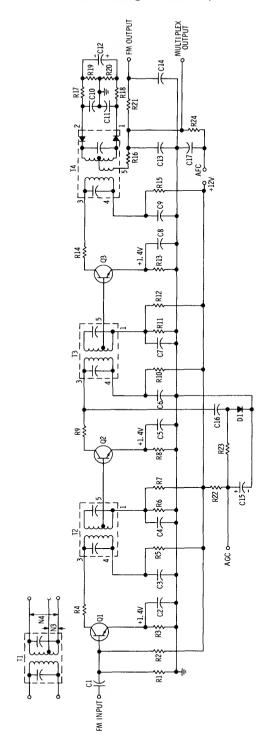

|         |     | Four-stage FM, Two-stage AM Unneutralized IF Amplifier                                          | 185                      |

|         |     | Three-stage FM, Two-stage AM, Unneutralized IF Amplifier                                        | 190                      |

|         |     | Two-stage FM, Two-stage AM Neutralized IF Amplifier                                             | 193                      |

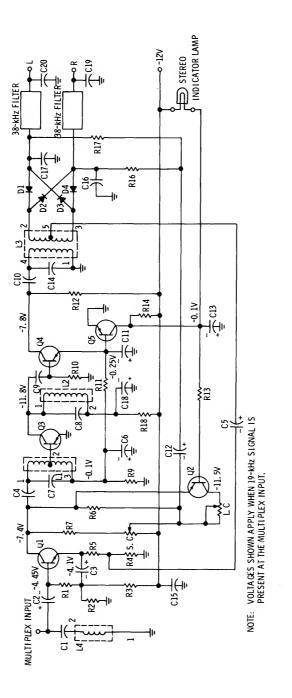

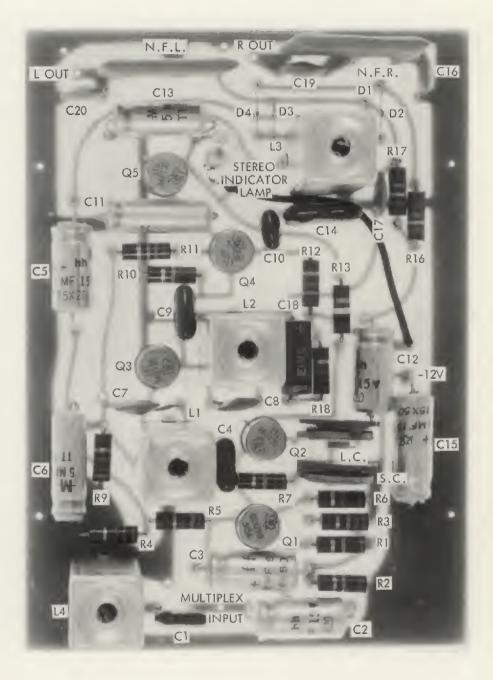

|         |     | Multiplex Adapter                                                                               | 196                      |

|         |     |                                                                                                 |                          |

| Chapter | 11. | FM IF Amplifier Circuit Applications                                                            | 201                      |

|         |     |                                                                                                 |                          |

|         |     | Introduction                                                                                    | 201                      |

|         |     | Four-stage Neutralized Amplifier Using Silicon Transistors 2N3826                               | 202                      |

|         |     | Three-stage Neutralized Amplifier Using Silicon Transistors                                     | 207                      |

|         |     | 2N3826                                                                                          | 207                      |

|         |     | Three-stage Neutralized Amplifier Using Silicon Transistors<br>TI408                            | 212                      |

|         |     | Four-stage Unneutralized Amplifier Using Germanium Transistors<br>TIXM04                        | 215                      |

|         |     | Three-stage Neutralized Amplifier Using Germanium Transistors                                   | 217                      |

|         |     | TIXM204                                                                                         | 218                      |

|         |     |                                                                                                 |                          |

|         |     |                                                                                                 |                          |

| PART    | ш   | TY DESIGN                                                                                       | 221                      |

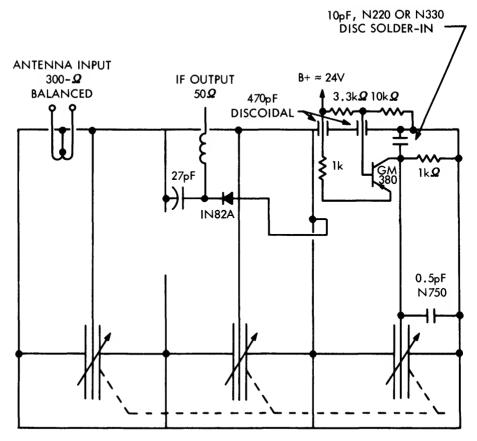

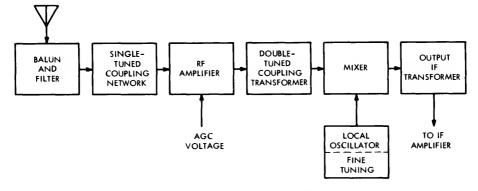

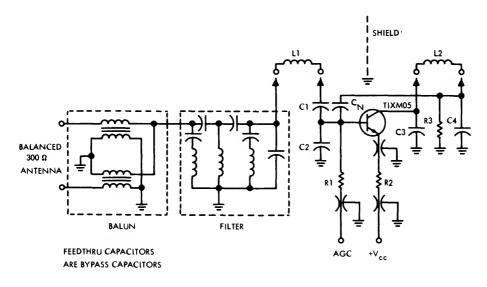

| Chapter 13. | VHF TV Tuners                 | 227        |

|-------------|-------------------------------|------------|

|             | Tuner Functions               | 227        |

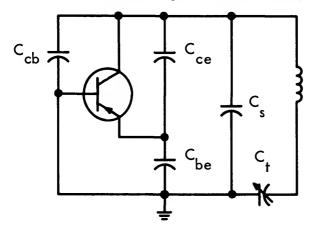

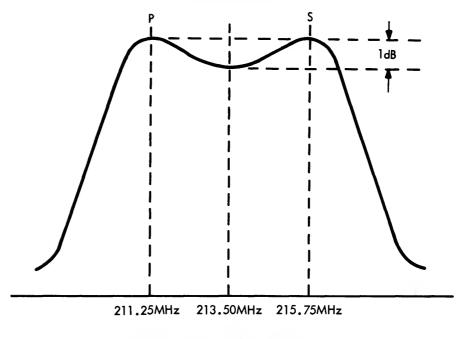

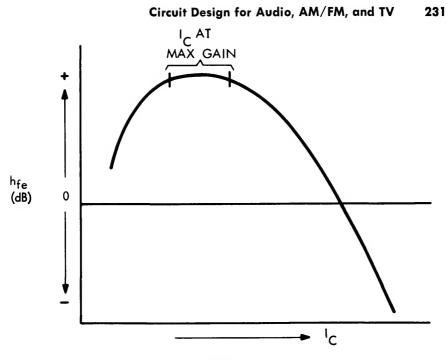

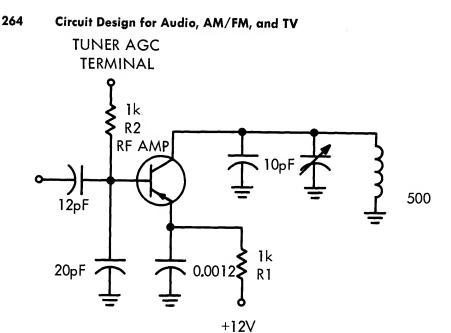

|             | RF Amplifier                  | 228        |

|             |                               |            |

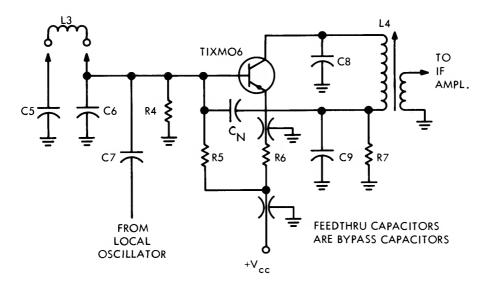

|             | Mixer                         | 230        |

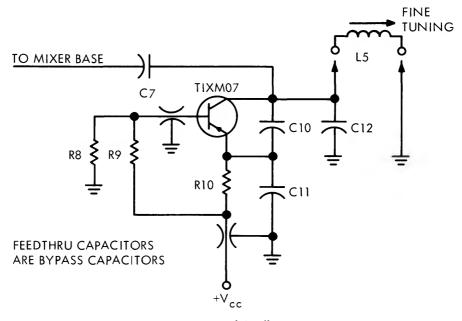

|             | Oscillator                    | 232        |

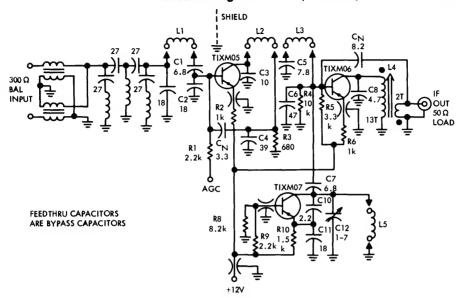

|             | Design Example                | 233        |

|             | Mixer                         | 233        |

|             | RF Amplifier                  | 239<br>247 |

|             | Balun<br>Oscillator           | 247        |

|             |                               | 247        |

|             | Packaging                     | 248        |

|             | References                    | 240        |

| Chambon 14  | Video IF Amplifier            | 249        |

| Chapter 14. |                               | 249        |

|             | C-i-                          | 240        |

|             | Gain                          | 249        |

|             | Power Output                  | 249        |

|             | A-C Stability                 | 250        |

|             | Design Procedure              | 251        |

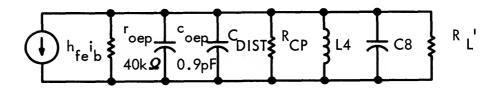

|             | Design Example                | 252        |

|             | Equation Derivations          | 256        |

|             | References                    | 258        |

|             |                               |            |

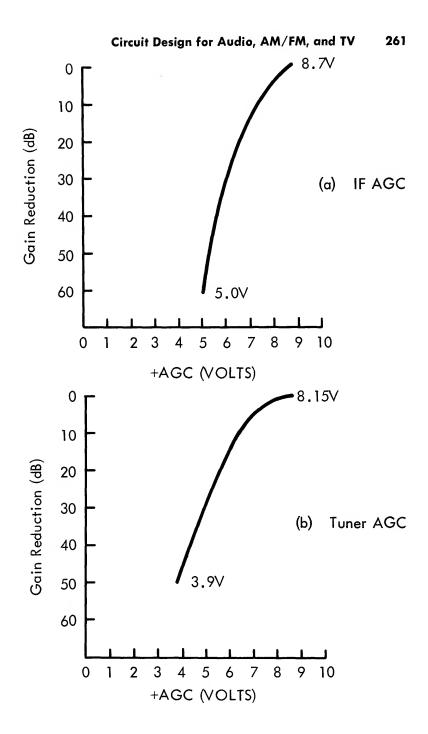

| Chapter 15. | TV Automatic Gain Control     | 259        |

|             |                               |            |

|             | Requirements                  | 259        |

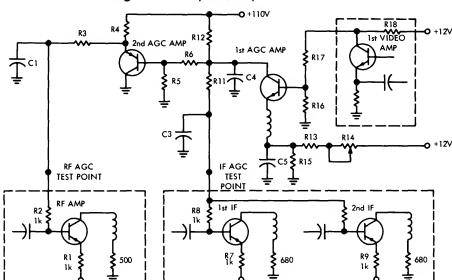

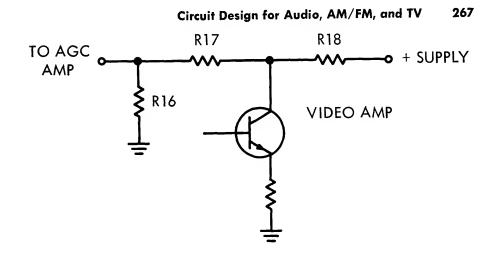

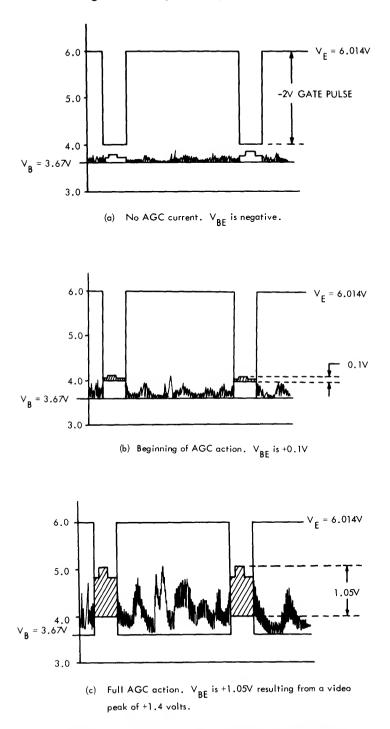

|             | Circuit Evaluation            | 263        |

|             | Equation Derivations          | 272        |

|             | References                    | 274        |

|             |                               |            |

| Chapter 16. | Video Amplifier System        | 275        |

| 4           |                               |            |

|             | System Requirements           | 275        |

|             | Video Output Stage            | 276        |

|             | D-C Considerations            | 277        |

|             | D-C Stability                 | 277        |

|             | Supply Voltage                | 278        |

|             | Breakdown Voltage             | 278        |

|             | Power Rating                  | 278        |

|             | High-frequency Considerations | 279        |

|             | Compensation                  | 281        |

|             | Emitter Resistance            | 282        |

|             | Emitter-follower Stage        | 283        |

|             | Contents                                                     | xi         |

|-------------|--------------------------------------------------------------|------------|

|             | Detector Stage                                               | 284        |

|             | References                                                   | 287        |

|             |                                                              | -0.        |

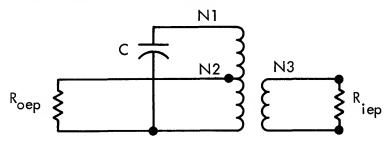

| Chapter 17, | Sound IF Amplifier System                                    | 289        |

|             |                                                              |            |

|             | System Requirements                                          | 289        |

|             | Amplifier-Limiter                                            | 290        |

|             | Gain                                                         | 290        |

|             | Stability                                                    | 290        |

|             | Transformer                                                  | 291<br>293 |

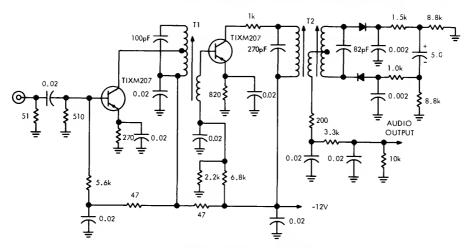

|             | Transformer Design Procedure<br>Design Example Using TIXM207 | 295        |

|             | Ratio Detector                                               | 296        |

|             | Amplifier Design Procedure                                   | 299        |

|             | Measured Performance                                         | 301        |

|             | References                                                   | 302        |

|             |                                                              |            |

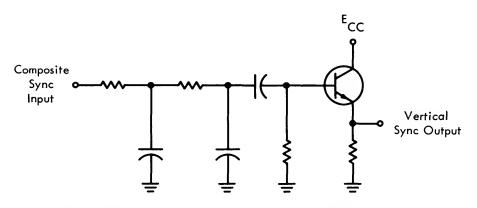

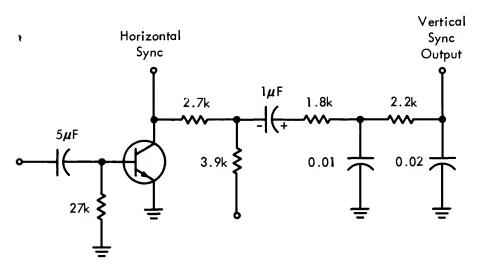

| Chapter 18. | Sync Separator                                               | 303        |

|             |                                                              |            |

|             | D-C Stability                                                | 303        |

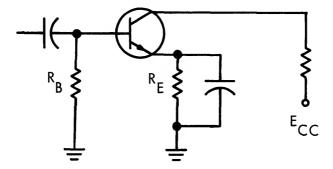

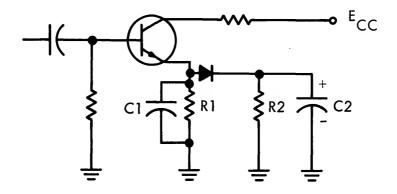

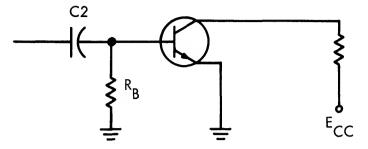

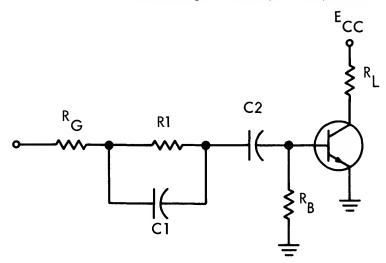

|             | Bias and Drive Methods                                       | 305        |

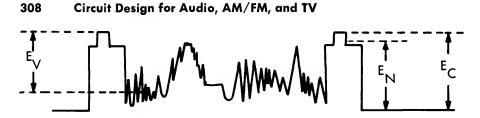

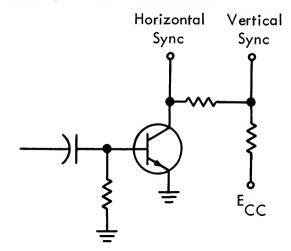

|             | Output Characteristics                                       | 309        |

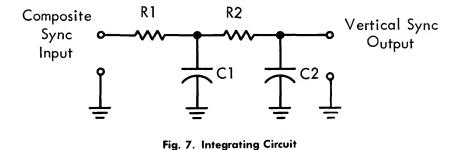

|             | Circuit Example                                              | 311        |

|             | References                                                   | 313        |

| cl          | Martin L O. Illing and Group Online                          | 015        |

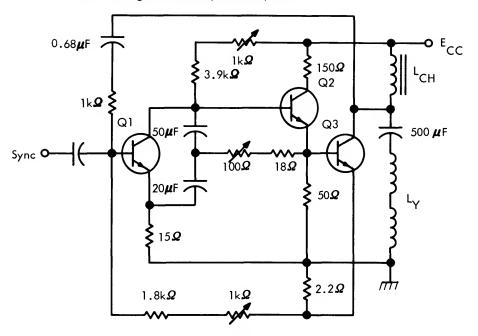

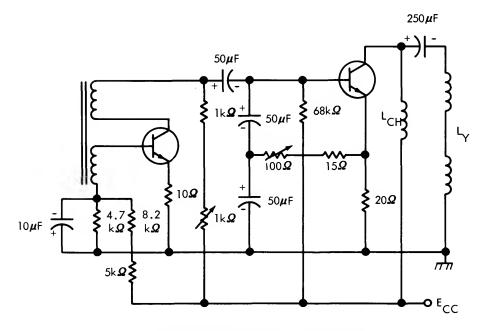

| Chapter 19. | Vertical Oscillator and Sweep Output                         | 315        |

|             | Blocking Oscillator                                          | 315        |

|             | Transistor Requirements                                      | 317        |

|             | Vertical Output Driver                                       | 317        |

|             | Vertical Output Considerations                               | 318        |

|             | Design Example                                               | 321        |

|             | References                                                   | 323        |

|             |                                                              |            |

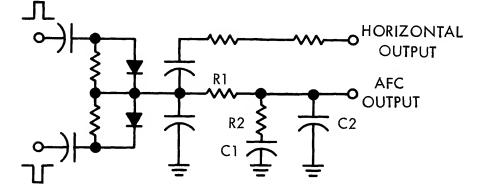

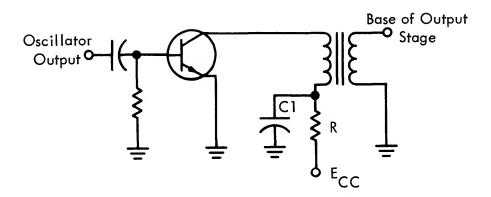

| Chapter 20. | Horizontal AFC and Oscillator                                | 325        |

|             | Automatic Frequency Control                                  | 325        |

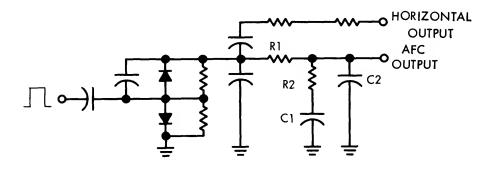

|             | Horizontal Oscillator                                        | 329        |

|             | References                                                   | 331        |

|             |                                                              |            |

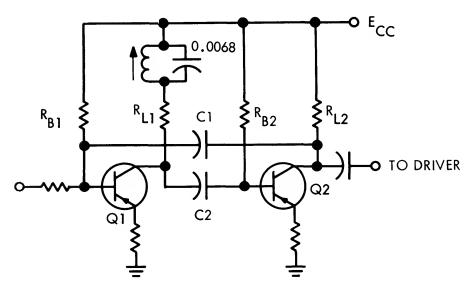

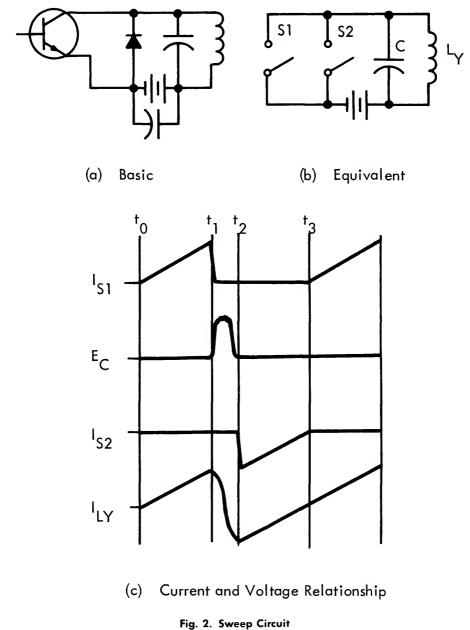

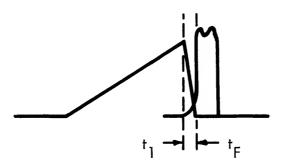

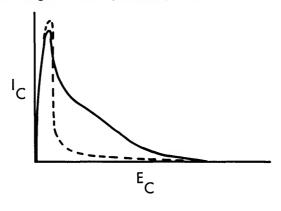

| Chapter 21. | Horizontal Driver and Sweep Output                           | 333        |

|             | Index                                                        | 345        |

|             | - # F889 \$P\$                                               | 222        |

# PART I Audio Design

#### **Audio Design Considerations**

As an introduction to the following chapters on practical audio amplifier design, this chapter discusses the merits of Class A versus Class B amplifiers, characteristics of various coupling schemes, and criteria for semiconductor device selection. Following this discussion, a list of symbols used in this and subsequent chapters is given. Finally, a bibliography of reference works used in the preparation of this text is presented.

Subjects which do not directly affect design parameters have been omitted in the discussions which follow. Many excellent texts are available to those interested in pursuing subjects such as semiconductor physics and rigorous stability criteria.

#### AMPLIFIER CIRCUIT SELECTION

**Class A Versus Class B.** Class A amplifiers generally provide lower distortion but lower power output than Class B. Class A amplifiers feature the highest power gain per stage but provide poor power efficiency. This low efficiency seriously limits Class A application where power consumption is a limiting factor; for example, in portable radios. Class B design provides higher power efficiency than Class A, but requires more components per stage. Class B is suitable for high power outputs, and in applications where power consumption is a limiting factor. The foregoing comments provide a guide for choosing between Class A and Class B amplifiers. After selection of the class, the designer must choose a coupling scheme. Selection of the coupling circuit depends on the performance and economy required. The following description gives an outline of coupling characteristics. These characteristics are not hard and fast rules. Indeed, a careful design can blend the virtues of several schemes into one, but usually at higher cost.

#### **Class A Amplifier Coupling Characteristics**

- Transformer-coupled Input, Transformer-coupled Output design provides fair frequency response and distortion. Bias stability is very good and easily obtained and the design is relatively inexpensive below three watts.

- RC-coupled Input, Transformer-coupled Output design provides fair frequency response and distortion. Bias stability is nearly as easily obtained as for the transformer input design. The design is less expensive because the transformer is replaced with a capacitor.

- Direct-coupled Input, Direct-coupled Output design provides excellent frequency response and low distortion. Bias stability is not as easily obtained as in the first two designs. This design is the least expensive for outputs below 0.1 watt.

- Direct-coupled Input, Transformer-coupled Output design provides good frequency response and fair distortion. Bias stability is not as good as in the transformer and RC input designs. This design is the least expensive for outputs above 0.1 watt.

#### Class B Amplifier Coupling Characteristics

- Transformer-coupled Input, Transformer-coupled Output design provides fair frequency response and distortion. Bias stability is good and easily obtained and power efficiency is high. Relative cost is high below one watt.

- Transformer-coupled Input, RC-coupled Output design provides good frequency response and fair distortion. Bias stability is good and easily obtained and power efficiency is high. Relative cost is high below 1 watt, but low above 20 watts.

#### TRANSISTOR SELECTION

The performance and reliability of an amplifier depend upon careful selection of the transistor type. Parameter considerations which are most important in making this selection are discussed here.

#### **Power Considerations**

- $P_{(Rate)}$  The maximum power rating of the device, normally referenced to 25°C. The power rating is always related to the device temperature (case or ambient) at which this power can be delivered. Data sheets generally specify a derating factor (K<sub>1</sub>) from which P<sub>(Rate)</sub> at temperatures above 25°C may be calculated.

- $P_{(Diss)}$  The power dissipated by the device while delivering the specified power output to the load. The device temperature, while dissipating this power, must be maintained below the device temperature rating  $T_1$  calculated at  $P_{(Diss)}$ .

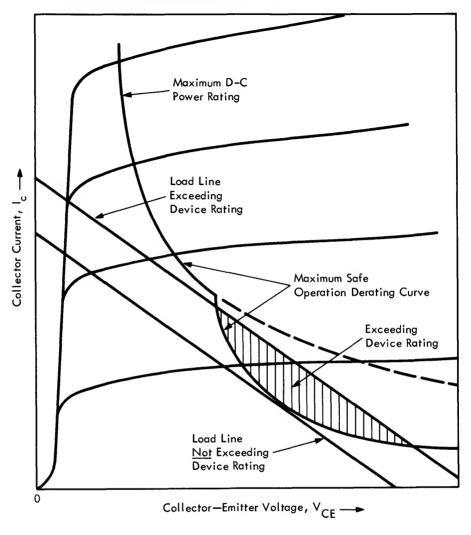

- Safe Operating Curve. At a given temperature, the permissible  $V_{CE}$ -I<sub>c</sub> combinations are determined by the hyperbola  $P_{(Rate)} = V_{CE}I_{c}$ .

At high voltages, secondary breakdown phenomena require that the power be further derated below the hyperbolic curve. The new derating line is called the safe operating curve. For circuits with heavy inductive loading, the a-c load line becomes an ellipse with an appreciable minor axis. The ellipse may exceed the safe operating curve and result in device failure unless precautions are taken. The manufacturer includes a safe operating curve on the data sheet of devices which require this consideration.

#### **Current Considerations**

- $I_{CM}$ —The maximum collector current of the device while operating at maximum output power.  $I_{CM}$  must be smaller than the maximum collector current rating of the device. The value of  $I_{CM}$  may correspond to impractical circuit values of  $h_{FE}$  and  $V_{CE(sat)}$ . The designer should select a transistor which not only provides sufficient  $I_{CM}$  but also maintains practical gain and saturation characteristics at that current. In Class B design, the peak current output greatly exceeds the average current.  $I_{CM}$  is then determined by the peak current requirement of the circuit.

- $I_{CBO}$  The collector-base reverse current with the emitter open.  $I_{CBO}$  is generally specified near the maximum collector-base voltage rating of the device. This reverse leakage current consists of two components: saturation current and surface current. Saturation current increases with an increase in base resistivity and voltage, and it is the dominant leakage mode at high temperatures. Surface current is voltage dependent and prevails at low temperatures.  $I_{CBO}$  is important in determining the circuit quiescent point stability. The stability criteria should be evaluated using the high-temperature  $I_{CBO}$  specification. This assures stability under worst-case leakage conditions.

#### **Voltage Considerations**

- $V_{(BR)EBO}$  Emitter-base reverse breakdown voltage with the collector open. This parameter is of importance in Class B amplifiers since the emitter-base junctions are alternately reverse biased each half-cycle.  $V_{(BR)EBO}$  should always be specified greater than the peak voltage input  $V_{ip}$  delivered to the base.

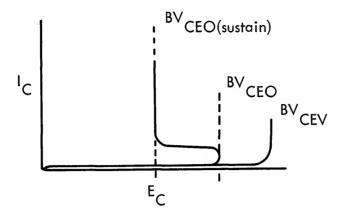

- V<sub>(BR)CE0</sub>-Collector-emitter reverse breakdown voltage with the base open. This specification gives the lowest collector-emitter voltage rating of the device.

- $V_{(BR)CES}$  Collector-emitter reverse breakdown voltage, with the emitter shorted to the base. This specification can be as high as  $V_{(BR)CBO}$ , but is normally slightly lower.

- $V_{(BR)CER}$  Collector-emitter reverse breakdown voltage with a resistance R terminated between the base and emitter. This parameter is of importance in circuits having emitter-base resistance terminations. For large values of R,  $V_{(BR)CER}$  approaches  $V_{(BR)CE0}$ . For low resistances,  $V_{(BR)CER}$  appraoches  $V_{(BR)CES}$ .

- $V_{(BR)CEV}$  Collector-emitter reverse breakdown voltage with the base returned to a negative bias back to the emitter terminal.  $V_{(BR)CEV}$  approaches  $V_{(BR)CBO}$  on most devices with a few volts reverse bias.

#### **Other Considerations**

$h_{FE}$  – The static value of the common-emitter short-circuit current gain.  $h_{FE}$  may usually be assumed to be equal to  $h_{fe}$  for audio frequencies. This approximation does not hold true at low current levels where reverse saturation current becomes appreciable. At higher collector currents, the device emitter efficiency falls off due to conductivity

modulation. This drop in emitter efficiency reduces the  $h_{\rm FE}$  of the device at higher currents.

As junction temperature increases,  $h_{FE}$  increases. However, the  $h_{FE}$  normally starts to fall off at a lower collector current level with increasing temperature. Because several effects are present, calculation of collector-to-base current ratios should be performed using the  $h_{FE(min)}$  value. This assures sufficient gain under all operating conditions.

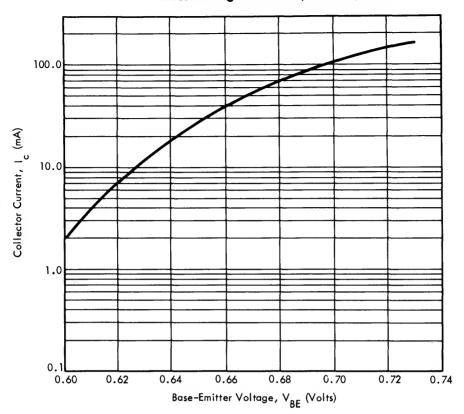

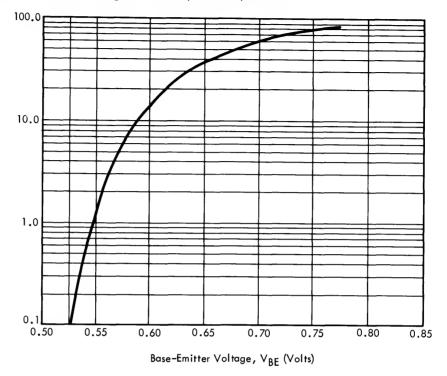

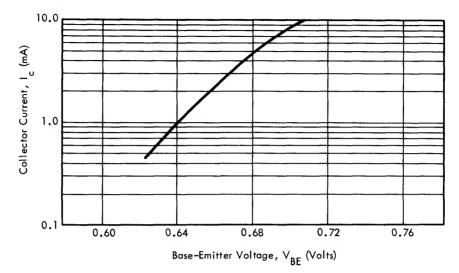

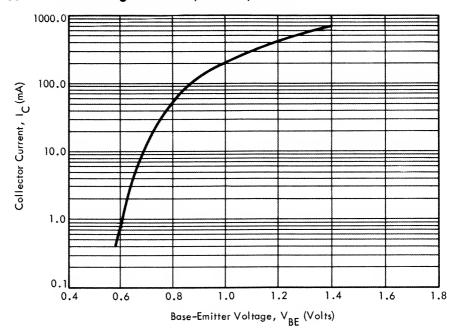

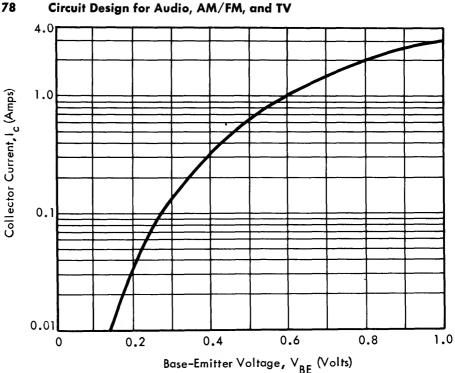

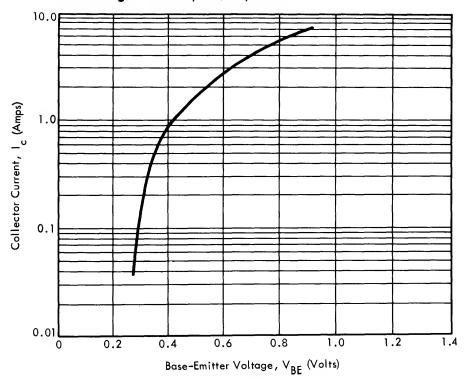

$y_{FE}$ —The plot of  $V_{BE}$  versus  $I_c$  is called the  $y_{FE}$  curve. For collector currents above one milliampere the  $y_{FE}$  curve is fairly linear.  $V_{BE}$  varies with individual devices and semiconductor materials. The  $V_{BE}$  voltage falls off with increasing temperature. For silicon, the reduction is about 2.0 millivolts per °C; for germanium, about 1.3 millivolts per °C. The  $y_{FE}$  curve is very useful for selecting the operating Q point. The base voltage drive requirements and peak collector current linearity can be evaluated also.

In Class A operation, the Q point is chosen so that the peak collector current excursion is within the linear region of the curve. In Class B operation, the  $y_{FE}$  curve is used to determine  $V_{BEQ}$ . By selecting proper  $V_{BEQ}$ , crossover distortion is reduced and the quiescent power dissipation is at a minimum.

$V_{CE(sat)}$ —The collector-to-emitter saturation voltage with both emitterbase and collector-base junctions forward biased. This parameter is generally measured with several times the minimum amount of base current required by the device  $h_{FE}$  for the required collector current. This base current overdrive ensures the device saturation. The ideal value of  $V_{CE(sat)}$  would be zero, allowing maximum voltage swings on the a-c load line and maximum power output. This ideal voltage is never achieved in practice and actual voltages are usually from 0.2 to 2.0 volts. Certain high-voltage devices are found with  $V_{CE(sat)}$  as high as 15 volts measured with usable base drives. This can be a considerable problem in direct-coupled Class B circuits where one of the driver pairs must saturate to a very low value in order to drive the output stage to the maximum collector swing.

#### SYMBOLS

6

- A<sub>v</sub> Voltage Gain

- C<sub>1</sub> Bypass Capacitor

- C<sub>c</sub> Coupling Capacitor

- C<sub>o</sub> Output Capacitor

- $\eta$  Transformer Efficiency

- f Frequency

- h<sub>fe</sub> Device a-c Short Circuit Current Gain, Common Emitter

h<sub>FE</sub> Device d-c Short Circuit Current Gain, Common Emitter

- $h_{FE(min)}$  Minimum  $h_{FE}$  Specified on Data Sheet

- h<sub>ie</sub> Device Input Impedance, Common Emitter

- Hz Hertz (cycles per second)

- I<sub>BB</sub> Circuit d-c Base Bias Current

- I<sub>BM</sub> Maximum Base Current, Referenced to d-c Zero

| _                    |                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| I <sub>bp</sub>      | Peak Base Current, Referenced to a-c Zero                                                                                    |

| I <sub>BQ</sub>      | Base Current, Quiescent Point                                                                                                |

| I <sub>c</sub>       | Collector Current                                                                                                            |

| I <sub>CBO</sub>     | Reverse Collector-to-base Current, Emitter Open                                                                              |

| $\Delta I_{CBO}$     | Change In Collector-to-base Current Due to Temperature Variations                                                            |

| I <sub>CM</sub>      | Maximum Collector Current, Referenced to d-c Zero                                                                            |

| I <sub>cp</sub>      | Peak Collector Current, Referenced to a-c Zero                                                                               |

| I <sub>CQ</sub>      | Collector Current, Quiescent Point                                                                                           |

| K <sub>1</sub>       | Thermal Derating Factor                                                                                                      |

| $\mathbf{K}_2$       | Base-emitter Temperature-dependent Term                                                                                      |

| K <sub>4</sub>       | Empirical Material-dependent Constant                                                                                        |

| K <sub>T</sub>       | Empirical Temperature-dependent Constant                                                                                     |

| $P_{(Diss)}$         | Device Power Dissipation                                                                                                     |

| P <sub>i(rms)</sub>  | RMS Power Input                                                                                                              |

| P <sub>o(rms)</sub>  | RMS Power Output                                                                                                             |

| P <sub>(Rate)</sub>  | Device Maximum Power Rating                                                                                                  |

| P.G.                 | Power Gain                                                                                                                   |

| P.G.(T)              | Total Power Gain                                                                                                             |

|                      | Quiescent Point                                                                                                              |

| $R_{cc}'$            | Collector-to-collector Reflected Load Impedance                                                                              |

| R <sub>D</sub>       | Decoupling Resistance                                                                                                        |

| R <sub>E</sub>       | External Emitter Resistance                                                                                                  |

| r <sub>e</sub>       | Device Internal Emitter Diffusion Resistance                                                                                 |

| R <sub>i</sub>       | Circuit Input Resistance                                                                                                     |

| R <sub>L</sub>       | Load Impedance                                                                                                               |

| $R_{L}'$             | Reflected Load Impedance                                                                                                     |

| Ro                   | Equivalent to $R_1$ , $R_2$ in Parallel                                                                                      |

| S<br>T               | Siemans $(1/\Omega)$                                                                                                         |

| T <sub>i</sub><br>T  | Maximum Device Operating Temperature At Full Load                                                                            |

| $T_2$                | Temperature Related to Maximum Device Power Rating                                                                           |

| $T_3$                | Maximum Temperature $I_{CBO}$ Specified on Data Sheet                                                                        |

| $T_4$                | Minimum Device Operating Temperature                                                                                         |

| T <sub>A</sub>       | Ambient Temperature                                                                                                          |

| V <sub>B</sub>       | Base-to-ground Voltage, Referenced to d-c Zero                                                                               |

|                      | Base-to-emitter Voltage<br>Change in Base-to-emitter Voltage Due to Temperature Variations                                   |

| $\Delta V_{BE}$      | Maximum Base-to-emitter Voltage                                                                                              |

| $V_{BEM}$            |                                                                                                                              |

| $V_{BEQ}$            | Base-to-emitter Voltage, Quiescent Point<br>Reverse Breakdown Voltage, Collector-to-base                                     |

| V <sub>(BR)CBO</sub> | Reverse Breakdown Voltage, Collector-to-emitter, Base Open                                                                   |

| V <sub>(BR)CEO</sub> | Reverse Breakdown Voltage, Collector-to-emitter, Base Open<br>Reverse Breakdown Voltage, Collector-to-emitter, Base Resistor |

| V (BR)CER            | termination to emitter                                                                                                       |

| V                    | Reverse Breakdown Voltage, Collector-to-emitter, Base shorted to                                                             |

| V (BR)CES            | emitter                                                                                                                      |

| V                    | Reverse Breakdown Voltage, Collector-to-emitter, Base                                                                        |

| ▼ (BR)CEV            | reverse-biased to emitter                                                                                                    |

| V                    | Reverse Breakdown Voltage, Emitter-to-base, Collector Open                                                                   |

| $V_{cc}^{(BR)EBO}$   | Circuit Supply Voltage                                                                                                       |

| V cc                 | Collector to emitter Voltage                                                                                                 |

V<sub>CE</sub> Collector-to-emitter Voltage

| V <sub>CE(sat)</sub> | Collector-to-emitter Saturation Voltage                      |

|----------------------|--------------------------------------------------------------|

| $V_{CEM}$            | Maximum Collector-to-emitter Voltage, Referenced to d-c Zero |

| $V_{cep}$            | Peak Collector-to-emitter Voltage, Referenced to a-c Zero    |

| $V_{CEQ}$            | Collector-to-emitter Voltage, Quiescent Point                |

| $V_{ip}$             | Peak Input Voltage, Referenced to a-c Zero                   |

| $V_{R1}$             | Voltage Across Resistance R <sub>1</sub>                     |

| $V_{RE}$             | Voltage Across the Emitter Resistance                        |

| <b>y</b> fe          | D-C Transconductance                                         |

| y <sub>fe</sub>      | A-C Transconductance                                         |

| $Z_b$                | Base Secondary Impedance, Input Transformer                  |

| $Z_{bb}$             | Base-to-base Secondary Impedance, Input Transformer          |

| $Z_{e}$              | Collector Primary Impedance, Input Transformer               |

The notation (D) in parentheses means the symbol has the above meaning but is referenced to the driver circuit. All symbols without the notation (D) are referenced to the output stage.

#### REFERENCES

- 1. Wheatley, C. F.: Reliability Considerations In The Application of Power Transistors To Consumer Products, *IRE Transactions*, Vol. BTR-8, July 1962.

- 2. Engineering Staff of Texas Instruments Incorporated: "Transistor Circuit Design," McGraw-Hill Book Co., Inc., New York, 1963.

- 3. Shea, Richard F.: "Transistor Applications," John Wiley & Sons, Inc., New York.

- 4. Kuehler, Hank: Small Signal Audio Design, Applications Report, Texas Instruments Incorporated.

- 5. Reference Data for Radio Engineers, International Telephone and Telegraph Corporation, 4th Edition, American Book – Stratford Press, Inc.

- 6. Corcoran, G. F., and H. W. Price: "Electronics," John Wiley & Sons, Inc., New York.

## 2

#### Class A Output and Driver Design Procedures

This chapter presents design procedures for four common combinations of amplifier coupling between the driver device and the power output stage and between the power output stage and the load. In providing complete procedures for the most common combinations, practical, simple solutions to design problems are given. This practical approach requires many approximations and assumptions based on design experience. All assumptions are noted in the text.

To make the design procedure complete for each coupling combination, some of the design equations and the comments prefacing these equations are repeated. Boldface numbers are used to designate equations appearing for the first time. Where equations are repeated, lightface numbers are used. Derivations of important equations are given in Chapter 6.

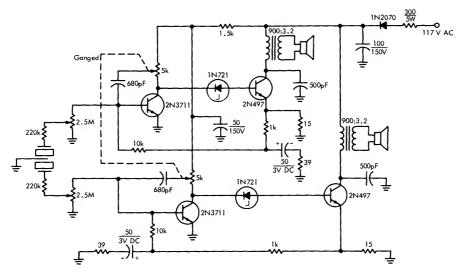

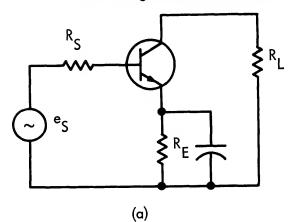

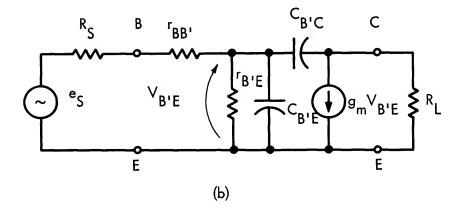

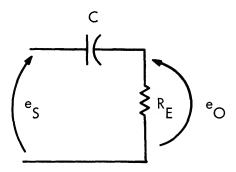

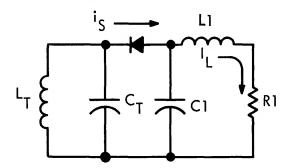

#### TRANSFORMER-COUPLED INPUT, TRANSFORMER-COUPLED OUTPUT

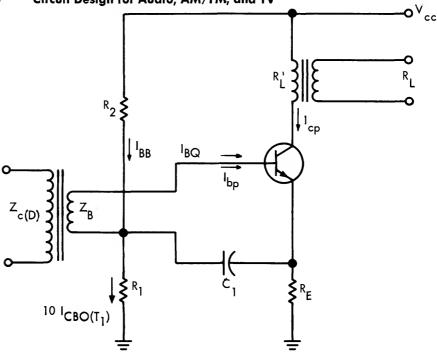

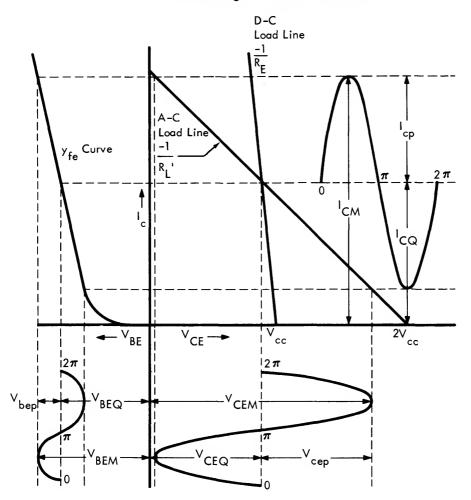

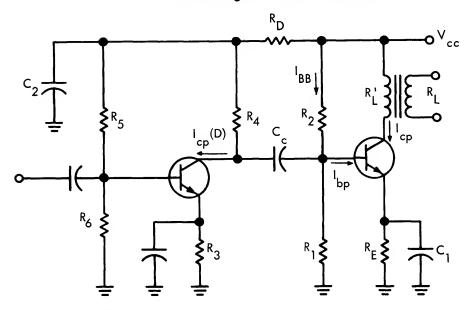

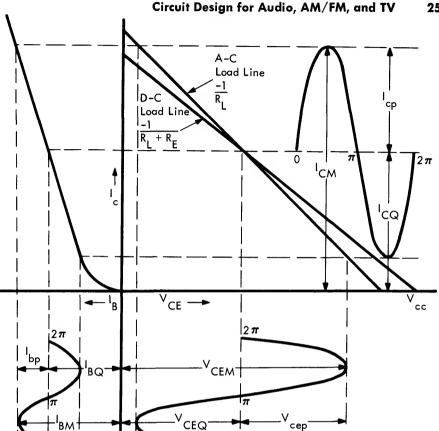

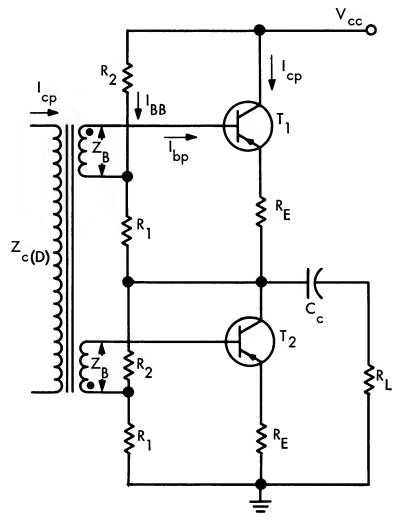

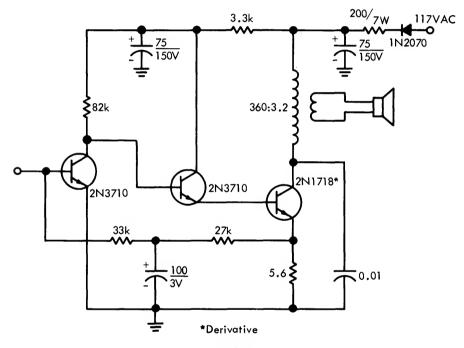

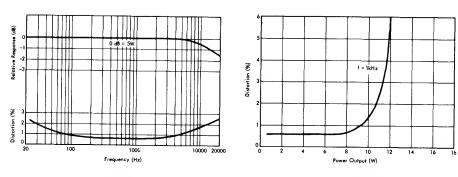

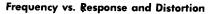

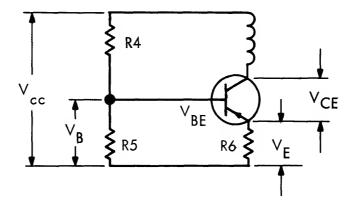

A circuit diagram is shown in Fig. 1 and dynamic characteristics are given in Fig. 2 for this coupling combination.

1. Maximum dissipation occurs in Class A amplifiers at the zero-signal-input quiescent point. Normally, Class A stages are biased for a 25% overload current to account for a shift in the circuit quiescent point caused by temperature variations. Power output  $P_{o(rms)}$  is therefore related to the device power dissipation  $P_{(Diss)}$  as shown in Eq. (1):

$$P_{(Diss)} = 3.12 P_{o(rms)}$$

(1)\*

2. This power dissipation capability of the device must be satisfied at the operating temperature conditions. The maximum permissible device temperature that can be tolerated without exceeding the device ratings is calculated

<sup>\*</sup>Equation derived in Chapter 6.

Fig. 1. Class A Transformer-coupled Input, Transformer-coupled Output Schematic

in Eq. (2). The transistor derating slope, the maximum device power rating, and corresponding temperature  $T_2$  are all taken from the device data sheet.

$$T_{1} = \frac{P_{(Rate)} - P_{(Diss)} + K_{1}T_{2}}{K_{1}}$$

(2)\*

where

$K_1 = Transistor Derating Slope - mW/^{\circ}C$

$T_1$  = Maximum Device Operating Temperature at  $P_{(Diss)} - {}^{\circ}C$

$T_2 =$  Temperature Related to Maximum Device  $P_{(Rate)} - {}^{\circ}C$

$P_{(Rate)} = Maximum Device Power Rating - mW.$

If the device is in a stud-mounted package, the heat sink should be evaluated to determine if it is able to dissipate the required  $P_{(Diss)}$  while maintaining the device temperature at or below  $T_1$ . This requirement must be calculated at the highest desired ambient temperature.

3. Now consider the device voltage requirements. In power stages, higher load impedances result in higher power gain per stage. Therefore, the device voltage capabilities should be determined from the data sheet to allow the selection of optimum circuit voltages. Class A circuits with transformer loads require:

<sup>\*</sup>Equation derived in Chapter 6.

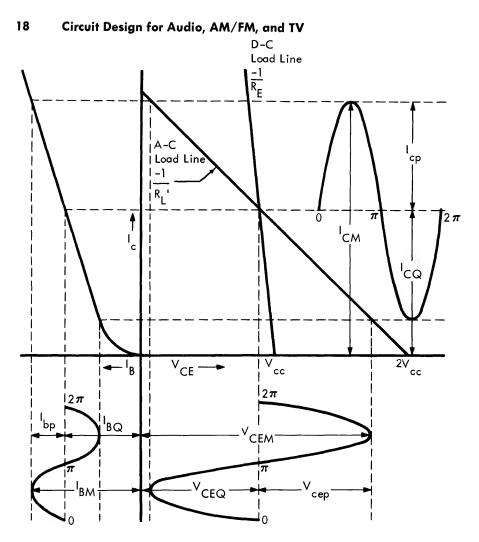

Fig. 2. Class A Transformer-coupled Input, Transformer-coupled Output Dynamic Characteristics

$$V_{cc} < \frac{V_{(BR)CER}}{2}$$

(3)

While this relationship represents the absolute maximum value of  $V_{cc}$  possible without exceeding the device maximum ratings, it is generally good design procedure to select  $V_{cc}$  equal to about 90% of the  $V_{cc}$  derived in Eq. (3). Additional care should be exercised in selecting the maximum circuit voltages for power devices that exhibit a reduction in the power rating of the device at high voltage levels. This derating is normally referred to as the Safe Operating Curve (Fig. 3). The a-c load line must be checked to make sure that a value of collector voltage has been chosen that will allow the load line to remain below the safe operating curve.

11

Fig. 3. Safe Operating Curve

4. One of the first considerations given worst-case circuit design is the effect of temperature variations on the critical device parameters. One of the most important parameters to evaluate for temperature stability is the change in the base-emitter voltage over the operating temperature range. This  $\Delta V_{BE}$  is calculated in Eq. (4):

$$\Delta V_{BE} = K_2 (T_1 - T_4)$$

(4)

where

$$K_2 = Base-Emitter Temperature-Dependent Term$$

Silicon - 2.0 × 10<sup>-3</sup> V/°C

Germanium - 1.3 × 10<sup>-3</sup> V/°C

T<sub>4</sub> = Minimum Device Operating Temperature.

5. With  $V_{cc}$  established, the reflected load impedance  $R_L'$  can be calculated. The load voltage  $V_{cep}$  is approximated by  $(V_{cc} - 8\Delta V_{BE} - V_{CE(sat)})$ . The  $\Delta V_{BE}$  term comes from assuming a maximum permissible change in collector quiescent current of 10% over the operating temperature range. This condition sets a value for the voltage drop across the emitter resistance  $R_E$  in terms of  $\Delta V_{BE}$ .

$$\mathbf{R}_{\mathrm{L}}' = \frac{(\mathbf{V}_{\mathrm{cc}} - 8\Delta \mathbf{V}_{\mathrm{BE}} - \mathbf{V}_{\mathrm{CE(sat)}})^2 \,\eta}{2\mathbf{P}_{\mathrm{o(rms)}}} \tag{5}$$

6. The peak a-c collector current can now be calculated in terms of the power output and the  $V_{cep}$  equivalent.

$$I_{cp} = \frac{2P_{o(rms)}}{(V_{cc} - 8\Delta V_{BE} - V_{CE(sat)}) \eta}$$

(6)

7. The quiescent collector current should be designed to be 25% greater than the peak a-c collector current to ensure operation in the linear portion of the  $y_{FE}$  curve. Linear operation on the device  $y_{FE}$  curve is necessary to prevent output distortion.

$$I_{CQ} = 1.25 I_{CP}$$

(7)

8. The maximum d-c collector current requirement is the sum of the quiescent point current and the a-c peak collector current during maximum signal operation. This maximum collector current  $I_{CM}$  must be less than the maximum collector current rating of the device and within the range of collector currents having a useable  $h_{FE}$  value.

$$I_{CM} = 2.25 I_{cp}$$

(8)

9. The maximum circuit requirements of power, voltage, and current have now been described, and the transistor type can be confirmed for the particular application in question.

10. The collector-base leakage current  $I_{CBO}$  is important in evaluating the circuit stability criteria. This leakage is a function of temperature and can be calculated at any temperature by assuming that the current doubles for an increase in temperature of 8°C for germanium and 12°C for silicon where

$$I_{CBO(T_1)} = I_{CBO(T_3)} 2^{(T_1 - T_3)/K_T}$$

(9)

where

<sup>\*</sup>Equation derived in Chapter 6.

14

#### Circuit Design for Audio, AM/FM, and TV

- $K_T = Empirical temperature-dependent constants Silicon 12 Germanium 8$

- $T_3 = Maximum$  temperature  $I_{CBO}$  specified on data sheet

- $I_{CBO(T_3)} = Maximum I_{CBO}$  specified on data sheet at temperature  $T_3$

11. The quiescent point base current  $I_{BQ}$  is calculated from the relationship of the quiescent collector current  $I_{CQ}$  and the device minimum  $h_{FE}$  specification taken from the data sheet.

$$I_{BQ} = \frac{I_{CQ}}{h_{FE(min)}}$$

(10)

12. The base bias that will provide the desired quiescent currents can now be calculated. To ensure minimum temperature effects on the Q-Point stability caused by  $I_{CBO}$  increasing the  $V_{BEQ}$  quiescent point, the base bias current  $I_{BB}$  is made considerably larger than the maximum  $I_{CBO(T_1)}$  calculated in Eq. (9).

$$I_{BB} = I_{BQ} + 10 I_{CBO(T_1)}$$

(11)

13. The Q-point base-emitter voltage  $V_{BEQ}$  may be obtained from the  $y_{FE}$  specification or curve on the data sheet. The value of  $V_{BEQ}$  is read off the curve at the quiescent collector current  $I_{CQ}$ .

$$V_{BEQ} = Data$$

Sheet Value at  $I_{CQ}$  (12)

14. Series resistances are used in the emitter circuit of Class A amplifiers to provide d-c stability in the output stage. There are two main sources that cause shifts in the d-c Q point with temperature. The base-emitter voltage  $\Delta V_{BE}$  decreases with temperature and the collector-base current I<sub>CB0</sub> increases with temperature. I<sub>BB</sub> has been designed 10 times I<sub>CB0(T1)</sub> so that I<sub>CB0</sub> through R<sub>1</sub> cannot change V<sub>BEQ</sub> more than 10% due to  $\Delta I_{CB0}$ . If also I<sub>CQ</sub>R<sub>E</sub> is calculated to be 10 times the  $\Delta V_{BE}$  contribution, the collector current I<sub>CQ</sub> should not change more than 10% due to increasing temperature effects on the device parameters. Equation (13) shows the minimum value of emitter resistance necessary to maintain the  $\Delta I_{CQ}$  within 10% of the nominal value calculated:

$$\mathbf{R}_{\mathrm{E}} \ge \frac{100\Delta \mathbf{V}_{\mathrm{BE}} + \mathbf{V}_{\mathrm{BEQ}}}{10 \ \mathrm{I_{CO}}} \tag{13}^*$$

If more regulation is required in the collector current stability point, the resistance  $R_E$  may be increased with a resultant increase in power loss from the d-c power source. Calculated values of  $R_E$  may become unreasonably large in circuits requiring strict control of the Q-point stability. In such instances, a compromise may be necessary between the permissible power loss in  $R_E$  and the collector-current Q-point stability. Feedback arrangements other than  $R_E$ have not been considered here, but this is a possible solution to improve the compromise should better Q-point stability be required.

15. The peak a-c base current  $I_{bp}$  is calculated from the peak collector current and device  $h_{FE}$  relationship in Eq. (14):

<sup>\*</sup>Equation derived in Chapter 6.

$$I_{bp} = \frac{I_{cp}}{h_{FE(min)}}$$

(14)

16. The bias resistor  $R_1$  is calculated to provide the required Q-point baseemitter voltage and corresponding collector current as described by the device  $y_{FE}$  curve.

$$R_{1} = \frac{I_{CQ}R_{E} + V_{BEQ}}{10 I_{CBO(T_{1})}}$$

(15)

17. The bias resistance  $R_2$  can now be determined from the base bias current and  $R_1$ .

$$R_2 = \frac{V_{cc} - 10 I_{CBO(T_1)} R_1}{I_{BB}}$$

(16)

18. To prevent degeneration of the a-c circuit gain caused by the emitter resistance  $R_{E_2}$ , a capacitor  $C_1$  is used to bypass  $R_E$  and  $R_1$  back to the common input transformer terminal. The necessary value of capacitance is determined by the amount of gain reduction that can be tolerated over the desired frequency range limits. The equation shown assumes an output falloff of three dB at the lowest desired frequency.

$$C_1 \ge \frac{I_{cp}}{2\pi f K_4} \tag{17}$$

where

$\begin{aligned} K_4 &= \text{Empirical constant dependent on material} \\ & \text{Silicon} - 35 \times 10^{-3} \\ & \text{Germanium} - 25 \times 10^{-3} \\ & \text{f} = \text{Lowest desired frequency.} \end{aligned}$

19. The power gain of the stage can now be calculated in terms of the rms power output and the input base-emitter parameters.

$$P.G. = \frac{2P_{o(rms)}}{V_{bep}}$$

(18)

20. The secondary impedance of the input transformer to the power stage is required for transformer design and later for calculation of the primary driver impedance. Since both series elements  $R_E$  and  $R_1$  in the input circuit have been bypassed, the input transformer secondary impedance  $Z_b$  may be calculated from the peak base currents and voltages:

$$Z_{b} = \frac{V_{bep}}{I_{bp}}$$

(19)

All of the necessary components and device parameters for the output stage have now been determined. Normally, a power output stage requires a driver input, and the collector circuit constants of a driver stage will now be evaluated.

<sup>\*</sup>Equation derived in Chapter 6.

21. Maximum power gain in the driver stage is accomplished by maximum collector load impedance. The driver power output requirement is usually low and this allows a high-impedance primary input transformer. Since with a high-impedance load, the collector voltage swing requirements are normally easily obtained, a practical high-impedance value for the driver transformer primary  $Z_{c(D)}$  may be assumed. Practical values are as high as 20 kilohms. A compromise may be necessary in applications where the driver supply voltage  $V_{cc(D)}$  is extremely limited and a sacrifice in maximum power gain is necessary. A value of  $Z_{c(D)}$  may be approximated in Eq. (20) in terms of the  $V_{cc(D)}$  available.

$$Z_{c(D)} = \frac{(V_{cc(D)} - 3V_{CE(sat)(D)})^2 \eta}{V_{bep} I_{bp}}$$

(20)

22. The peak collector current of the driver is dependent upon the power input requirements of the output stage and the transformer primary impedance  $Z_{c(D)}$ . This peak current requirement may be calculated in Eq. (21).

$$I_{cp(D)} = I_{bp} \sqrt{\frac{Z_b}{\eta Z_{c(D)}}}$$

(21)

23. The driver collector-current quiescent point is determined by the peak collector current calculated above. The quiescent current must be greater than the peak collector current to prevent operation of the device in the nonlinear portion of the  $y_{FE}$  curve. Distortion of the driver signal will result if the device is allowed to operate to cut-off, so a minimum value of collector current is chosen that will always be above the knee of the  $y_{FE}$  curve. The collector quiescent current may be calculated in Eq. (22):

$$I_{CQ(D)} = I_{cp(D)} + 1.0 \times 10^{-3} A$$

(22)

24. The driver supply voltage requirements can be considerably smaller than the power output stage requirements due to the smaller power output of the driver. The minimum driver supply voltage may be calculated in Eq. (23) in terms of the base-emitter parameters of the output stage and the collector saturation voltage of the driver device. This driver supply voltage may then be obtained by dropping the output stage supply voltage through a decoupling resistor or by providing a separate voltage source.

$$V_{cc(D)} = \frac{V_{bep} I_{bp}}{\eta I_{cp(D)}} + 3V_{CE(sat)(D)}$$

(23)\*

25. The critical driver collector requirements have now been calculated and the remainder of the driver parameters and components may be determined by using the appropriate equations derived for the same coupling scheme in a power output stage. The power output requirement of the driver device may be calculated in Eq. (24) in terms of the collector requirements.

$$P_{o(rms)(D)} = \frac{I_{cp(D)}^{2} Z_{c(D)} \eta}{2}$$

(24)

<sup>\*</sup>Equation derived in Chapter 6.

Fig. 4. Class A RC-coupled Input, Transformer-coupled Output Schematic

#### RC-COUPLED INPUT, TRANSFORMER-COUPLED OUTPUT

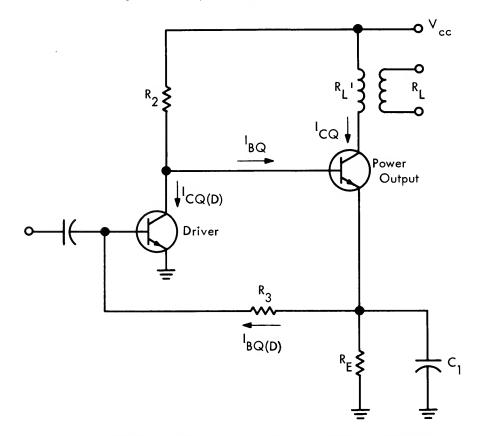

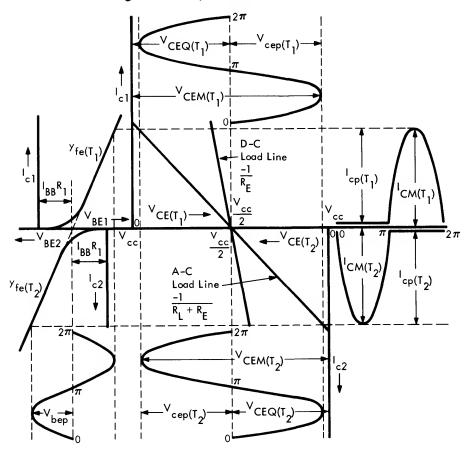

A circuit diagram is shown in Fig. 4 and dynamic characteristics are given in Fig. 5 for this coupling combination.

1. Maximum dissipation occurs in Class A amplifiers at the zero-signal-input quiescent point. Normally, Class A stages are biased for a 25% overload current to account for a shift in the circuit quiescent point caused by temperature variations. Power output  $P_{o(rms)}$  is therefore related to the device power dissipation  $P_{(Diss)}$  as shown in Eq. (1):

$$P_{(Diss)} = 3.12 P_{o(rms)}$$

(1)\*

2. This power dissipation capability of the device must be satisfied at the operating temperature conditions. The maximum permissible device temperature that can be tolerated without exceeding the device ratings is calculated in Eq. (2). The transistor derating slope, the maximum device power rating, and corresponding temperature  $T_2$  are all taken from the device data sheet.

$$T_{1} = \frac{P_{(Rate)} - P_{(Diss)} + K_{1}T_{2}}{K_{1}}$$

(2)\*

where

$K_1 = Transistor Derating Slope - mW/^{\circ}C$

$T_1$  = Maximum Device Operating Temperature at  $P_{(Diss)} - {}^{\circ}C$

$T_2$  = Temperature Related to Maximum Device  $P_{(Rate)} - {}^{\circ}C$

$P_{(Rate)} = Maximum Device Power Rating - mW.$

<sup>\*</sup>Equation derived in Chapter 6.

Fig. 5. Class A RC-coupled Input, Transformer-coupled Output and Direct-coupled Input, Transformer-coupled Output Dynamic Characteristics

If the device is in a stud-mounted package, the heat sink should be evaluated to determine if it is able to dissipate the required  $P_{(Diss)}$  while maintaining the device temperature at or below  $T_1$ . This requirement must be calculated at the highest desired ambient temperature.

3. Now consider the device voltage requirements. In power stages, higher load impedances result in higher power gain per stage. Therefore, the device voltage capabilities should be determined from the data sheet to allow the selection of optimum circuit voltages. Class A circuits with transformer loads require:

$$V_{cc} < \frac{V_{(BR)CER}}{2}$$

(3)

While this relationship represents the absolute maximum value of  $V_{cc}$  possible without exceeding the device maximum ratings, it is generally good design procedure to select  $V_{cc}$  equal to about 90% of the  $V_{cc}$  derived in Eq. (3). Additional care should be exercised in selecting the maximum circuit voltages for power devices that exhibit a reduction in the power rating of the device at high voltage levels. This derating is normally referred to as the Safe Operating Curve (Fig. 3). The a-c load line must be checked to make sure that a value of collector voltage has been chosen that will allow the load line to remain below the safe operating curve.

4. One of the first considerations given worst-case circuit design is the effect of temperature variations on the critical device parameters. One of the most important parameters to evaluate for temperature stability is the change in the base-emitter voltage over the operating temperature range. This  $\Delta V_{BE}$  is calculated in Eq. (4):

$$\Delta V_{BE} = K_2 (T_1 - T_4)$$

(4)

where

$K_{2} = Base-emitter temperature-dependent term$ Silicon - 2.0 × 10<sup>-3</sup> V/°CGermanium - 1.3 × 10<sup>-3</sup> V/°C

$T_4$  = Minimum device operating temperature.

5. With  $V_{cc}$  established, the reflected load impedance  $R_L'$  can be calculated. The load voltage  $V_{cep}$  is approximated by  $(V_{cc} - 8\Delta V_{BE} - V_{CE(sat)})$ . The  $\Delta V_{BE}$  term comes from assuming a maximum permissible change in collector quiescent current of 10% over the operating temperature range. This condition sets a value for the voltage drop across the emitter resistance  $R_E$  in terms of  $\Delta V_{BE}$ .

$$R_{L}' = \frac{(V_{cc} - 8\Delta V_{BE} - V_{CE(sat)})^2 \eta}{2P_{o(rms)}}$$

(5)\*

6. The peak a-c collector current can now be calculated in terms of the power output and the  $V_{cep}$  equivalent.

$$I_{cp} = \frac{2P_{o(rms)}}{(V_{cc} - 8\Delta V_{BE} - V_{CE(sat)}) \eta}$$

(6)

7. The quiescent collector current should be designed to be 25% greater than the peak a-c collector current to ensure operation in the linear portion of the  $y_{FE}$  curve. Linear operation on the device  $y_{FE}$  curve is necessary to prevent output distortion.

$$I_{CQ} = 1.25 I_{cp}$$

(7)

8. The maximum d-c collector current requirement is the sum of the quiescent point current and the a-c peak collector current during maximum signal operation. This maximum collector current  $I_{CM}$  must be less than the maximum collector current rating of the device and within the range of collector currents having a useable  $h_{FE}$  value.

<sup>\*</sup>Equation derived in Chapter 6.

$$I_{CM} = 2.25 I_{cp}$$

(8)

9. The maximum circuit requirements of power, voltage, and current have now been described, and the transistor type can be confirmed for the particular application in question.

10. The collector-base leakage current  $I_{CBO}$  is important in evaluating the circuit stability criteria. This leakage is a function of temperature and can be calculated at any temperature by assuming that the current doubles for an increase temperature of 8°C for germanium and 12°C for silicon.

$$I_{CBO(T_1)} = I_{CBO(T_3)} 2^{(T_1 - T_3)/K_T}$$

(9)

where

$K_T = Empirical temperature-dependent constants$ Silicon - 12Germanium - 8 $<math>T_3 = Maximum temperature I_{CBO}$  specified on data sheet

$I_{CBO(T_3)} = Maximum I_{CBO}$  specified on data sheet at temperature  $T_3$

11. The quiescent point base current  $I_{BQ}$  is calculated from the relationship of the quiescent collector current  $I_{CQ}$  and the device minimum  $h_{FE}$  specification taken from the data sheet.

$$I_{BQ} = \frac{I_{CQ}}{h_{FE(min)}}$$

(10)

12. The base bias that will provide the desired quiescent currents can now be calculated. To ensure minimum temperature effects on the Q-point stability caused by  $I_{CBO}$  increasing the  $V_{BEQ}$  quiescent point, the base bias current  $I_{BB}$  is made considerably larger than the maximum  $I_{CBO(T_1)}$  calculated from Eq. (9).

$$I_{BB} = I_{BQ} + 10 \ I_{CBO(T_1)}$$

(11)

13. The Q-point base-emitter voltage  $V_{BEQ}$  may be obtained from the  $y_{FE}$  specification or curve on the data sheet. The value of  $V_{BEQ}$  is read off of the curve at the quiescent collector current  $I_{CQ}$ .

$$V_{BEQ} = Data$$

Sheet Value at  $I_{CQ}$  (12)

14. Series resistances are used in the emitter circuit of Class A amplifiers to provide d-c stability in the output stage. There are two main sources that cause shifts in the d-c Q-point with temperature. The base-emitter voltage  $\Delta V_{BE}$  decreases with temperature and the collector-base current I<sub>CBO</sub> increases with temperature. I<sub>BB</sub> has been designed 10 times I<sub>CBO(T1)</sub> so that  $\Delta I_{CBO}$  through R<sub>1</sub> cannot change V<sub>BEQ</sub> more than 10% due to  $\Delta I_{CBO}$ . If also I<sub>CQ</sub>R<sub>E</sub> is calculated to be 10 times the  $\Delta V_{BE}$  contribution, the collector current I<sub>CQ</sub> should not change more than 10% due to increasing temperature effects on the device parameters. Equation (13) shows the minimum value of emitter resistance necessary to maintain the  $\Delta I_{CQ}$  within 10% of the nominal value calculated:

$$R_{E} \ge \frac{100 \,\Delta V_{BE} + V_{BEQ}}{10 \,I_{CQ}} \tag{13}$$

\*Equation derived in Chapter 6.

If more regulation is required in the collector current stability point, the resistance  $R_E$  may be increased with a resultant increase in power loss from the d-c power source. Calculated values of  $R_E$  may become unreasonably large in circuits requiring strict control of the Q-point stability. In such instances, a compromise may be necessary between the permissible power loss in  $R_E$  and the collector-current Q-point stability. Feedback arrangements other than  $R_E$  have not been considered here, but this is a possible solution to improve the compromise should better Q-point stability be required.

15. The peak a-c base current  $I_{bp}$  is calculated from the peak collector current and device  $h_{FE}$  relationship in Eq. 14:

$$I_{bp} = \frac{I_{cp}}{h_{FE(min)}}$$

(14)

16. The bias resistor  $R_1$  is calculated to provide the required Q-point baseemitter voltage and corresponding collector current as described by the device  $y_{FE}$  curve.

$$R_{1} = \frac{I_{CQ}R_{E} + V_{BEQ}}{10 \ I_{CBO(T_{1})}}$$

(15)

17. The bias resistance  $R_2$  can now be determined from the base bias current and  $R_1$ .

$$R_2 = \frac{V_{cc} - 10 \ I_{CBO(T_1)} \ R_1}{I_{BB}}$$

(16)

18. The input impedance to the output stage  $R_i$  is the parallel configuration of the device common-emitter input impedance and the equivalent resistance  $R_o$ .

$$\mathbf{R}_{i} = \frac{\mathbf{h}_{FE} \mathbf{R}_{o}}{\mathbf{h}_{FE} + \mathbf{y}_{fe} \mathbf{R}_{o}}$$

(25)\*

where

$$R_o = rac{R_1 R_2}{R_1 + R_2}$$

19. Degeneration of the a-c gain of the stage is eliminated by bypassing the emitter resistance  $R_E$ . The value of capacitance necessary is determined by the amount of gain falloff that can be tolerated over the desired frequency range. Equation (17) assumes an output falloff of three dB at the lowest frequency.

$$C_1 \ge \frac{I_{\rm cp}}{2\pi f K_4} \tag{17}$$

where

$K_4$  = Empirical constant dependent on material Silicon - 35 × 10<sup>-3</sup> Germanium - 25 × 10<sup>-3</sup> f = Lowest desired frequency.

\*Equation derived in Chapter 6.

20. The power gain for the stage can then be calculated as a function of the device  $h_{fe}$  and the ratios of the collector reflected load impedance and the input impedance.

P.G. =

$$\frac{h_{fe}^2 R_L' \eta}{R_i}$$

(26)

21. The decoupling resistance  $R_D$  in conjunction with capacitor  $C_2$  (usually approximately 10  $\mu$ F) prevents signal feedback through the internal resistance of the power source. The decoupling resistor is assumed to be at least equal to the internal resistance of the source delivering 20 mA at half the terminal voltage.

$$\mathbf{R}_{\mathrm{D}} = \frac{\mathbf{V}_{\mathrm{cc}} \times 10^3}{40} \tag{27}$$

22. The driver emitter resistance  $R_3$  can now be approximated in terms of the decoupling resistance  $R_D$ . The value shown is an empirical value, and it is not normally very critical due to the low peak collector currents and small collector voltage swing present in the driver stage.

$$\mathbf{R}_3 = 3\mathbf{R}_D \tag{28}$$

23. The driver collector load is resistive and therefore the maximum collector-emitter voltage is equal to the supply voltage  $V_{cc}$ . The output of the driver stage is capacitive coupled to the input of the output stage. This requires  $V_{bep}$  to equal  $V_{cep(D)}$ . It is common practice to allow for a 50% voltage overload to ensure an undistorted driver signal. The maximum collector-emitter requirements for the driver device are given in Eq. (30) when the assumption of Eq. (29) is made:

$$V_{cep(D)} = V_{bep} = V_{BEM} - V_{BEQ}$$

(29)

$$V_{CEM(D)} = 3(V_{cep(D)} + V_{CE(sat)(D)})$$

(30)\*

24. The collector-emitter quiescent voltage of the driver is calculated in terms of the driver saturation voltage and the peak collector-emitter voltage of the driver.

$$V_{CEQ(D)} = 2V_{cep(D)} + 3V_{CE(sat)(D)}$$

(31)

25. The driver stage is designed to be capable of delivering 180% of base current  $I_{bp}$  to the output stage in addition to the parallel resistance losses caused by  $R_0$ . This prevents driver overload under maximum output conditions:

$$I_{cp(D)} = 1.8 \left( I_{bp} + \frac{V_{BEQ}}{R_o} \right)$$

(32)

26. The driver quiescent collector current is calculated from  $I_{CP(D)}$  using the same factor derived for ensuring linear operation in the output stage collector current.

<sup>\*</sup>Equation derived in Chapter 6.

$$I_{CQ(D)} = 1.25 I_{cp(D)}$$

(33)

27. The driver load resistance  $R_4$  is calculated at the quiescent collector current  $I_{CQ(D)}$ .

$$R_4 = \frac{V_{cc} - V_{CEQ(D)}}{I_{CQ(D)}} - (R_D + R_3)$$

(34)

28. The output of the driver stage is coupled to the power output stage through the coupling capacitor  $C_e$  and the driver load resistance  $R_4$ . The minimum coupling capacitance required can be calculated in terms of the lowest desired frequency response of the circuit.

$$C_{c} \geq \frac{1}{2\pi f R_{4}}$$

(35)

29. The remainder of the driver circuit parameters may be calculated from the appropriate bias and quiescent equations derived for the power output stages.

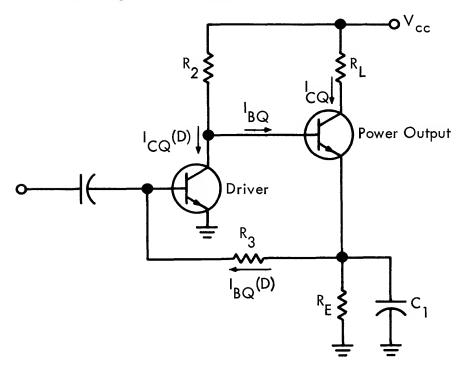

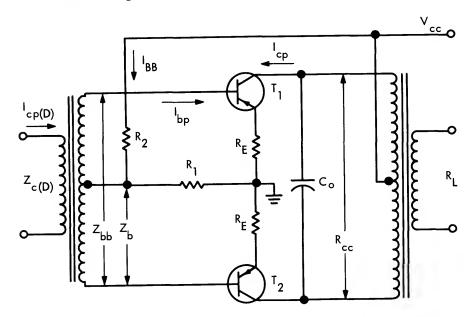

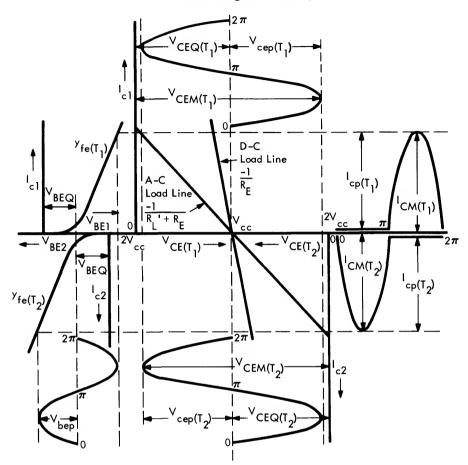

#### DIRECT-COUPLED INPUT, DIRECT-COUPLED OUTPUT

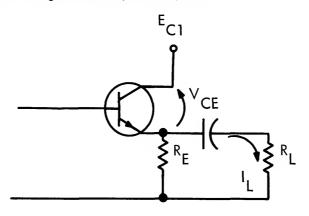

A circuit diagram is shown in Fig. 6 and dynamic characteristics are given in Fig. 7 for this coupling configuration.

1. Class A direct-coupled amplifiers are becoming more popular where cost and frequency response are the most important considerations. While there are some inherent advantages there are also some disadvantages concerning stability criteria in direct-coupled amplifiers. Because the driver and output stages are coupled directly, any variations in one device parameter will be reflected to the other device with a resultant change in its operating point. One of the most severe causes of parameter drift is due to the device temperature during maximum power operation.

2. Maximum power dissipation occurs in Class A amplifiers at the zerosignal-input quiescent point. Normally, Class A stages are biased for a 25% current overload to account for a shift in the quiescent point as described above. Power output is therefore related to the device power dissipation as shown in Eq. (36).

$$P_{(Diss)} = 2.5 P_{o(rms)}$$

(36)\*

3. This maximum power dissipation capability of the device must be satisfied at the full-load temperature conditions. The maximum permissible device temperature that can be tolerated without exceeding the device rating is calculated in Eq. (2). The transistor derating slope, the maximum device power rating, and corresponding temperature  $T_2$  are all taken from the transistor data sheet. Care must be observed to keep the rating units the same when the derating slope and the device power ratings are taken from the data sheet.

<sup>\*</sup>Equation derived in Chapter 6.

Fig. 6. Class A Direct-coupled Input, Direct-coupled Output Schematic

$$T_{1} = \frac{P_{(\text{Rate})} - P_{(\text{Diss})} + K_{1}T_{2}}{K_{1}}$$

(2)\*

where

$K_1 = Transistor derating slope - mW/^{\circ}C$

$T_1 =$  Maximum device operating temperature at  $P_{(Diss)} - {}^{\circ}C$

$T_2 =$  Temperature related to maximum device  $P_{(Rate)} - {}^{\circ}C$

$P_{(Rate)} = Maximum device power rating - mW.$

If the device is in a stud-mounted package, the heat sink should be evaluated to determine if it is able to dissipate the required  $P_{(Diss)}$  while maintaining the device temperature at or below  $T_1$ . This requirement must be calculated at the highest desired ambient temperature.

4. The maximum collector current in a direct-coupled stage must be less than the maximum collector current rating of the device and within the range of collector currents having a useable  $h_{FE}$  value. The maximum current  $I_{CM}$  is equal to the sum of the peak load current and the quiescent operating current

<sup>\*</sup>Equation derived in Chapter 6.

Fig. 7. Class A Direct-coupled Input, Direct-coupled Output Dynamic Characteristics

in the collector of the device. The quiescent collector current is increased 25% over the peak load current requirement to ensure device operation in the linear portion of the h<sub>FE</sub> curve over the desired temperature range. The peak collector current is calculated in Eq. (37) and the maximum device collector current is calculated in Eq. (8):

$$I_{\rm cp} = \sqrt{\frac{2P_{\rm o(rms)}}{R_{\rm L}}}$$

(37)

$$I_{CM} = 2.25 I_{cp}$$

(8)

5. Now consider the device voltage requirements. In Class A power stages with resistive loads, the maximum collector-emitter voltage requirement of the device is:

$$V_{(BR)CER} > V_{cc}$$

(38)

Low-impedance speaker loads can be considered almost resistive as far as the device collector circuit is concerned and therefore the above relationship can be used for almost any direct-coupled speaker loads. This value represents the minimum device voltage rating that may be used in this application. The minimum collector voltage requirement is given in terms of the power output and load resistance in Eq. (39). This equation contains a maximum approximation for the voltage drop across the emitter resistance  $R_E$ . Therefore the calculated value represents a maximum approximation for estimating the collector voltage requirements of the circuit.

$$\mathbf{V}_{(\text{BR})\text{CER}} \ge 2 \sqrt{2\mathbf{P}_{\text{o(rms)}} \mathbf{R}_{\text{L}}} + 4\mathbf{V} + 2\mathbf{V}_{\text{CE(sat)}}$$

(39)

6. The quiescent collector current is set at 25% greater than the peak collector load current to ensure operation in the linear portion of the  $h_{FE}$  curve. This requirement allows maximum power output with minimum output distortion. The output-stage collector quiescent current is calculated in Eq. (7):

$$I_{cq} = 1.25 I_{cp}$$

(7)

7. The quiescent point base current in the output stage is calculated from the relationship of the quiescent collector current  $I_{CQ}$  and the device minimum  $h_{FE}$  specification taken from the data sheet.

$$I_{BQ} = \frac{I_{CQ}}{h_{FE(min)}}$$

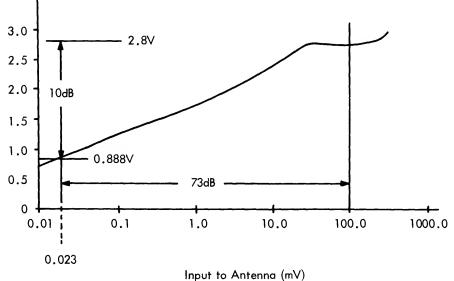

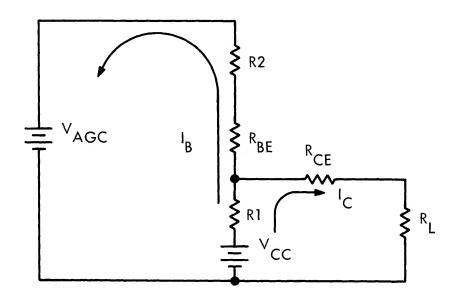

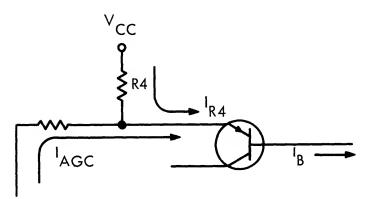

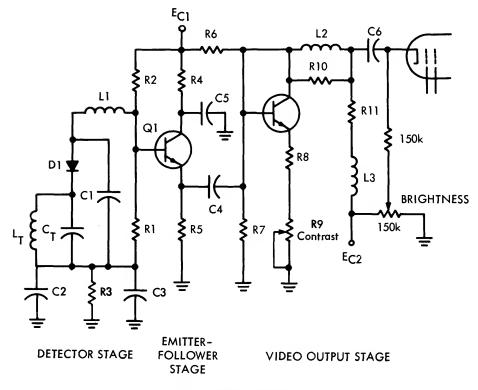

(10)