# APPLICATION NOTE

6730 S. TUCSON BLVD. • TUCSON, ARIZONA 85734 • TEL: (602) 294-1431

# protect op amps from overloads

JERALD GRAEME, Burr-Brown Research Corp.

THOUGH ENGINEERS ARE BECOMING MORE AND more aware of the subtleties of operational-amplifier characteristics, there are still far too many situations where op-amps are being destroyed by voltage and current overloads. This is due, in part, to the proliferation of op-amps in unusual applications.

Some overload conditions are obvious: input breakdown under excessive input voltages or output overheating under short circuits. Most op-amps are protected to some degree against these two conditions.

Other overload conditions, however, are less evident. These include voltages maintained by capacitors after the power supplies are turned off. A voltage retained at an amplifier input by a capacitor or other source can forward-bias and destroy a substrate junction when the negative supply voltage becomes less negative than the input voltage.

To help prevent op-amp failures like these, there are several protection circuits that the designer can build. They will guard op-amps against power-supply faults and input and output overloads.

### PROTECTION FROM POWER-SUPPLY FAULTS

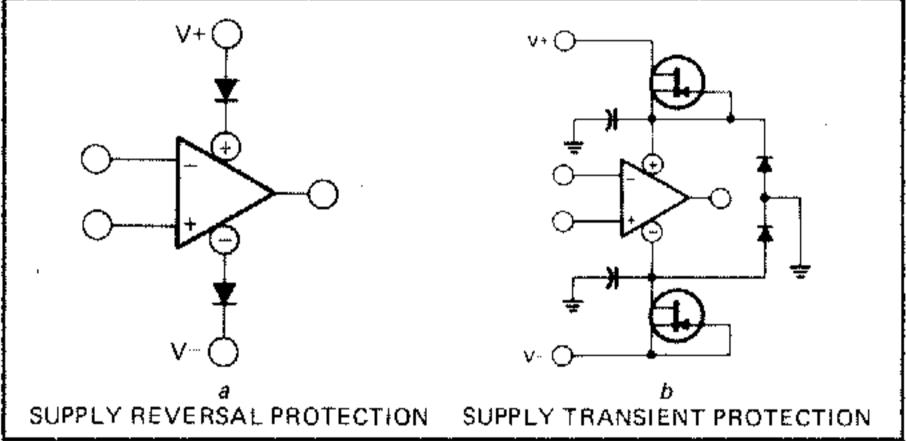

The most common power-supply faults in op-amp circuits are supply reversals and voltage transients. Damage from these overloads is prevented by the circuits shown in Fig. 1. To protect against damage by voltage reversal, a diode is added in series with each power supply to block reverse current flow (Fig. 1-a). This protection also prevents forward-bias of an integrated-circuit substrate junction, since a reverse-biased diode will now disconnect the negative supply. However, for the latter protection alone, resistors can be added in series with the inputs to limit the substrate current to a few milliamperes.

Protection against transient voltages is provided by the Zener diode clamps and the voltage-absorbing FET current

FIG. 1—DAMAGE FROM POWER SUPPLY faults is prevented because diodes block currents during voltage reversals as shown in a, and clamp the power supply terminals to limit transient voltages as shown in b.

sources (Fig. 1-b). The Zener diodes have "on" voltages that are greater than the normal supply voltages but less than the maximum supply ratings on the op-amp. Thus, the Zener diodes will be off under normal supply voltages, and they will clamp the supply transient voltages.

The current-source-connected FET's are chosen with  $I_{DSS}$  levels above the normal current drains of the op-amp. Below the  $I_{DSS}$  level, the FET's are below pinchoff and appear as small resistances in series with the supply lines. If transients appear on the supply lines, the Zener diodes turn on to clamp the supply voltages, and their current drains raise the FET currents to  $I_{DSS}$ . Now the FET's are in pinchoff and they appear as high-impedance current sources to support excess voltages. As long as the transients do not cause voltage breakdown in the FET's, the transient currents are limited to  $I_{DSS}$ .

#### KEEPING INPUT VOLTAGES AT SAFE LEVELS

Overload conditions at op-amp inputs are essentially those of excessive common-mode and differential voltages. Either can induce a voltage breakdown that will damage

or destroy the input transistors. Because of the precise matching needed between the input transistors, even minor damage from breakdown can significantly degrade the DC input characteristics of the op-amp. Such damage can result from quite moderate differential input voltages, since bipolar transistors typically have about a 6V emitter-base breakdown voltage. Input stages with FET's are less vulnerable to overloads of this magnitude, but they are more sensitive to the low-energy, high-voltage discharges that are frequently encountered.

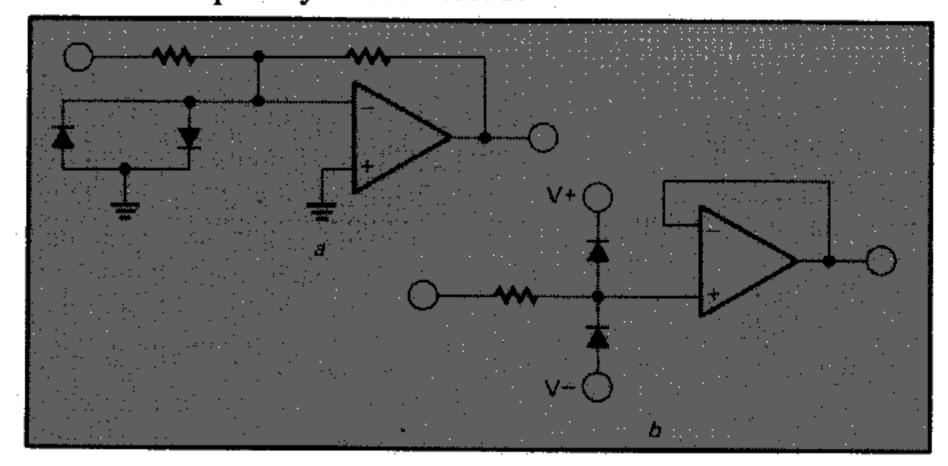

FIG. 2—INPUT CLAMPS protect against any level of input transient voltage that does not force excessive current through the diodes from the input resistor, in either the inverting (shown in a) or non-inverting (shown in b) configuration.

Protection from very high input voltages is provided by the diode clamps shown in Fig. 2. For both the inverting and noninverting configurations, the diodes limit the voltages reaching the amplifiers to safe levels without restricting signal swing. Input transients of thousands of volts can be withstood in this manner, so long as the diode currents are adequately limited by the input resistors. To permit amplifier common-mode swing in the noninverting configuration, the clamp diodes are connected to the power supplies rather than to ground (Fig. 2-b). Here, however, diode leakages will add to the input error current.

Input protection against differential signals up to the level of power-supply voltages is usually incorporated in op-amps. However, larger voltage overloads can still damage the amplifiers. Further protection against differential voltage overloads can be provided (Fig. 3-a) so long as the overloads don't raise either input beyond the supply-voltage levels. Where this latter condition is possible, the supply-level clamps shown in Fig. 2-b should be added.

Once again, diode clamps are used as in Fig. 2-a, but in this case (Fig. 3-a) the current-limiting resistance is divided equally between the two inputs. Thus, the error-voltage drops produced with the input bias currents will tend to match and cancel. Some error will remain, however, due to the differences in input bias currents.

Another error with this clamp circuit can result from the input current that it draws under overload. This current can be a serious error in comparator circuits, where high input resistance is needed in the overload state. To lower the overload input current, the values of input resistors can be increased, but this also increases the error voltage produced by the input offset current of the op-amp.

The weaknesses of the clamp circuit in Fig. 3-a can be avoided<sup>2</sup> with a second protection circuit (Fig. 3-b). In this case the differential input voltage is limited by a high-resistance divider for low current under overload. In normal operation the large resistors would develop significant error voltages, but they are shunted by low FET resistances. Specifically, DC error would be significant only at the

comparator trip point, where the added voltage would produce an offset. But with the protection circuit, the differential input voltage at the trip point is zero, leaving the diodes off, and hence providing zero gate bias for the FET's.

With this bias, both FET's have a low channel resistance, ron, that produces only a small error voltage because of the input bias current. When the input signal moves away from the trip point, the gate-source voltage of one FET or the other increases. This, in turn, increases the channel resist-

FIG 3—THE EFFECT of differential input overloads can be eliminated by one of these two protection circuits. Amplifier input voltage can be reduced by either clamping as shown in a, or by selectively dividing as shown in b.

ance of the FET until it reaches the megohm level of  $r_{ds}$  at pinchoff. Then, the input current must flow through the resistor in parallel with this FET and through the other FET, which is zero-biased. This, in effect, leaves an input divider, R2/(R1 + R2), to reduce the input signal.

The most common types of output overloads are excess power dissipation and output-stage breakdown when the output is shorted. Most op-amps incorporate current-limiting circuits to control power dissipation. External current limits can be added if they are not in the op-amp or if a lower level of limiting current is desired to protect a load. Also, such a reduced current limit may be needed when the output is shorted to a point above or below ground potential. In this case the added potential may increase the output-stage dissipation. And if the output is shorted to a voltage beyond the power-supply levels, voltage breakdown can result.

## LIMITING OUTPUT CURRENTS

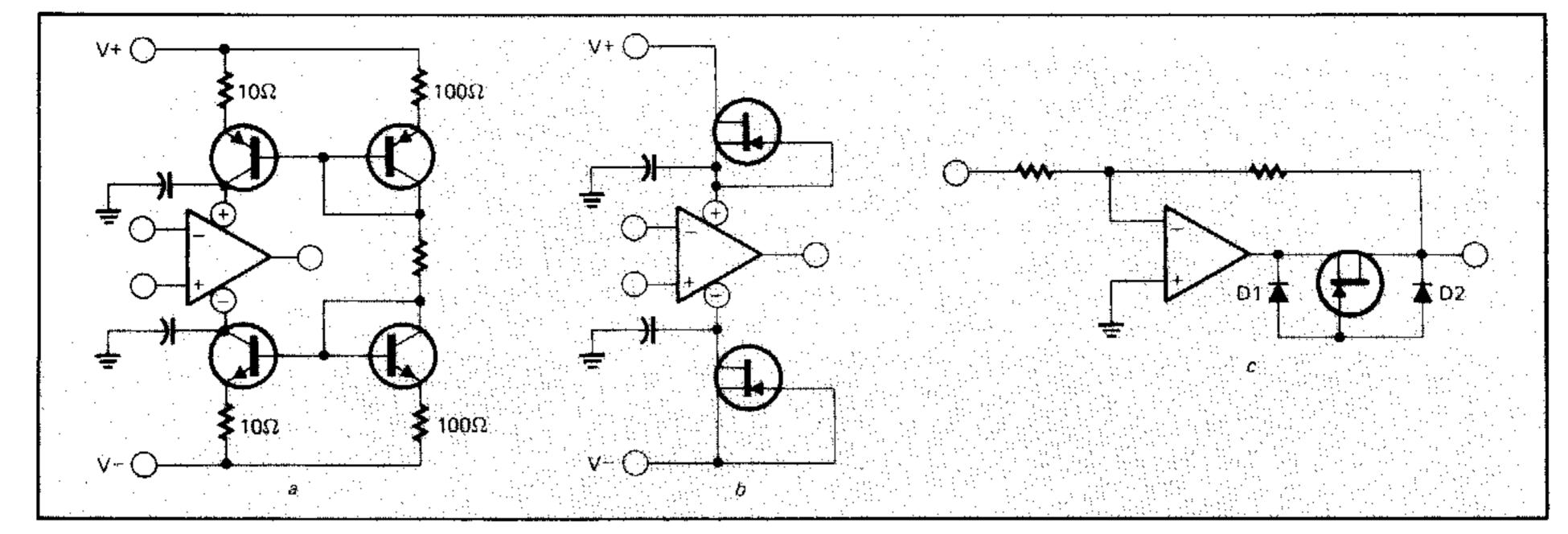

One way of providing an external current limit is to connect current sources in series with the power supplies (Fig. 4). When the supply-current drains are below the design level of the current sources, the transistors add low resistances in series with the supplies. The bipolar-transistor current sources are then in saturation, adding resistances equal to  $r_{sat}$  plus 10 ohms, and the FET's are not yet in pinchoff, so they each add a resistance of  $r_{on}$ . Provided these small resistances are bypassed, they have little effect on performance. When the supply currents reach the predetermined operating levels of the current sources, the transistors start to operate in their constant-current mode—with very high output resistances. Only a small additional current is then needed to develop large voltage drops across the current sources and reduce the supply voltage.

A somewhat simpler external current limit is provided if a single current source is added in series with the output. This simplicity stems from the ability of an FET to operate in an inverted mode, so that only one FET is necessary

FIG 4—PRECISE SELECTABLE CURRENT LIMITING results when current sources are added in series with the power supplies as shown in a and b. To limit both current polarities, an FET current source in series with the output may be added as shown in c.

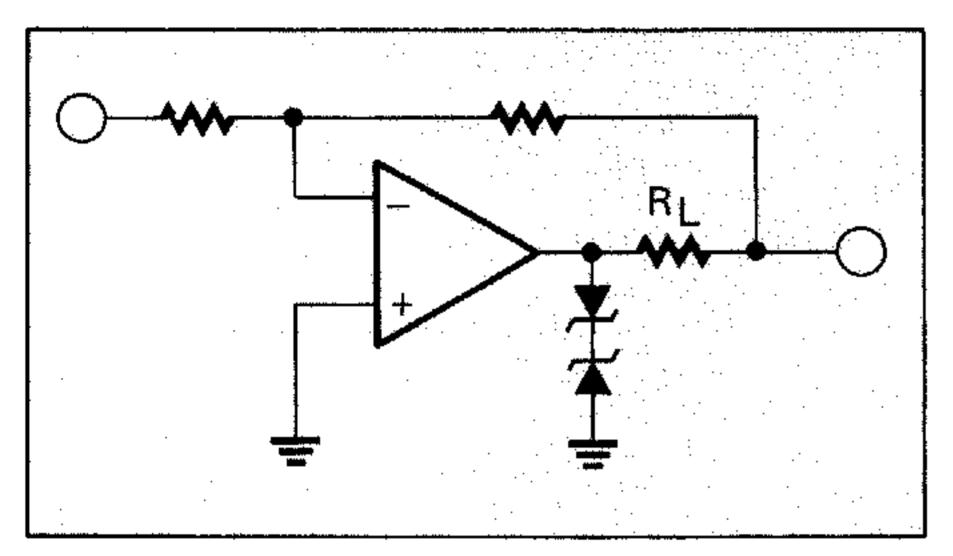

FIG. 5—PROTECTION FROM EXCESSIVE VOLTAGES that may be connected accidentally to the output is provided by Zener-diode clamps.

(Fig. 4-c). For currents flowing into the output terminal, D2 is reverse-biased, and the voltage on the FET produces gate-drain leakage current that is conducted by D1. For this low diode current, the voltage D1 is too low to forward-bias the gate-source junction, but the diode does connect the gate to the source. As before, the FET operates as a current source.

Once again, the series resistance added by the FET is low  $(r_{on})$  until limiting occurs at  $I_{DSS}$ . Since this resistance is inside the amplifier feedback loop, its effect is divided by the loop gain. When the output current reverses and flows out of the output terminal, D1 turns off and D2

conducts the leakage current. In this way the gate is connected to the drain for an inverted FET current source. Thus, the circuit works for both polarities of output current.

If an output short circuit or an inductive load causes the output voltage to exceed one of the power-supply levels, the output stage can be damaged by voltage breakdown. Protection against such an overload can be provided by Zener clamps (Fig. 5).

With the Zener diodes, the op-amp output terminal cannot be pulled beyond selectable voltage levels, and the excess voltage is absorbed by  $R_L$ . The current-limiting resistor,  $R_L$ , should be made large enough to protect the Zener diodes, but not so large as to develop a swing-limiting voltage in normal operation. Since  $R_L$  is in the feedback loop, its contribution to output impedance is diminished by the loop gain.

Note that a high voltage on the output terminal also raises the voltage on the inverting amplifier input through the voltage divider formed by the feedback resistors. While this voltage is reduced by the divider, it can sometimes break down the input stage. If this is a possibility, input protection should be used.

R-E

#### References:

- 1. Tobey, G., Graeme, J., Huelsman, L., Operational Amplifiers; Design and Applications, McGraw-Hill, New York (1971).

- 2. Accardi, L., "Modified 710 Maintains Accuracy at High Input Voltages," EEE, October (1970).