# TECHNOLOGICAL RESEARCH AND DEVELOPMENT AUTHORITY (TRDA)

1277-112114

1111

SUMMARY REPORT: NASA COOPERATIVE AGREEMENT NO. <u>NCC10-0008</u>

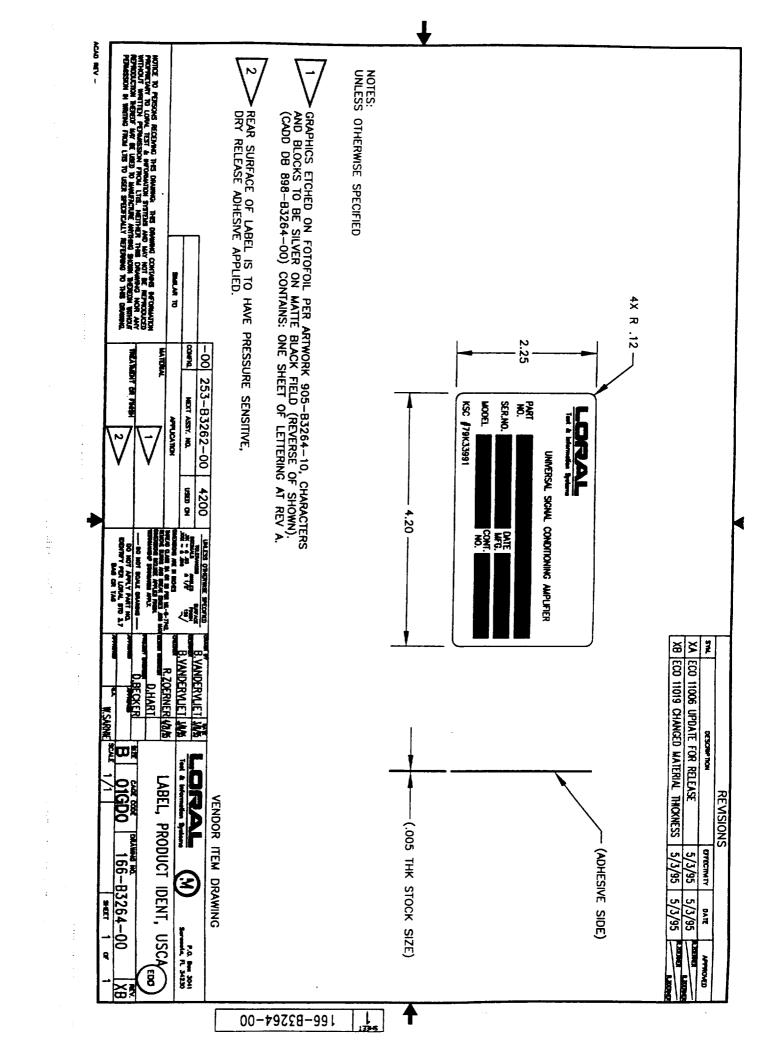

**"UNIVERSAL SIGNAL CONDITIONING AMPLIFIER"**

TECHNOLOGICAL RESEARCH AND DEVELOPMENT AUTHORITY STATE OF FLORIDA 6750 S. HIGHWAY U. S. 1 TITUSVILLE, FLORIDA 32780

# **PERFORMANCE REPORT**

1

7

Τ

Г

\_\_\_\_\_

$\neg$

Under

# NASA COOPERATIVE AGREEMENT NO.: NCC10-0008

Entitled

"Universal Signal Conditioning Amplifier"

Principal Investigator: Report Period: Frank Kinney 3/15/94 – 12/31/96

April 1997

# **TABLE OF CONTENTS**

I. INTRODUCTION

\_

\_

٦

٦

1

Π

\_

------

i

.

- II. PERFORMANCE

- III. TRDA PARTNERSHIP TASKS

- IV. SUMMARY

- V. ATTACHMENTS

#### I. INTRODUCTION

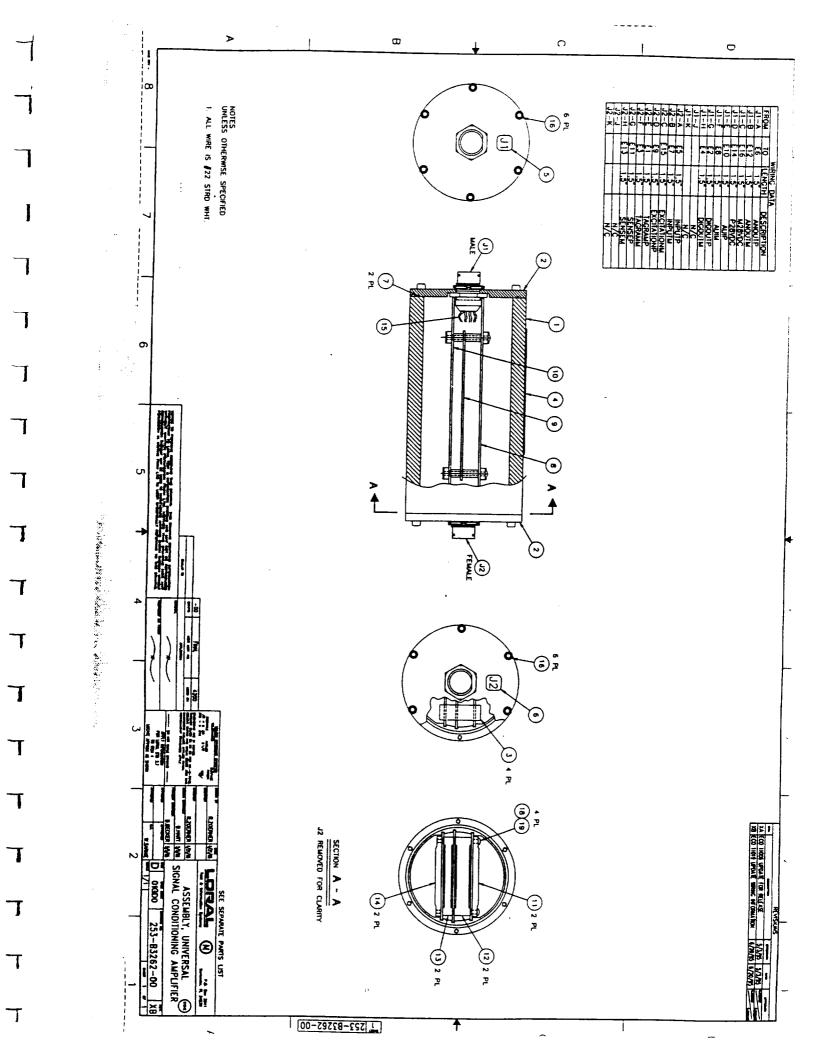

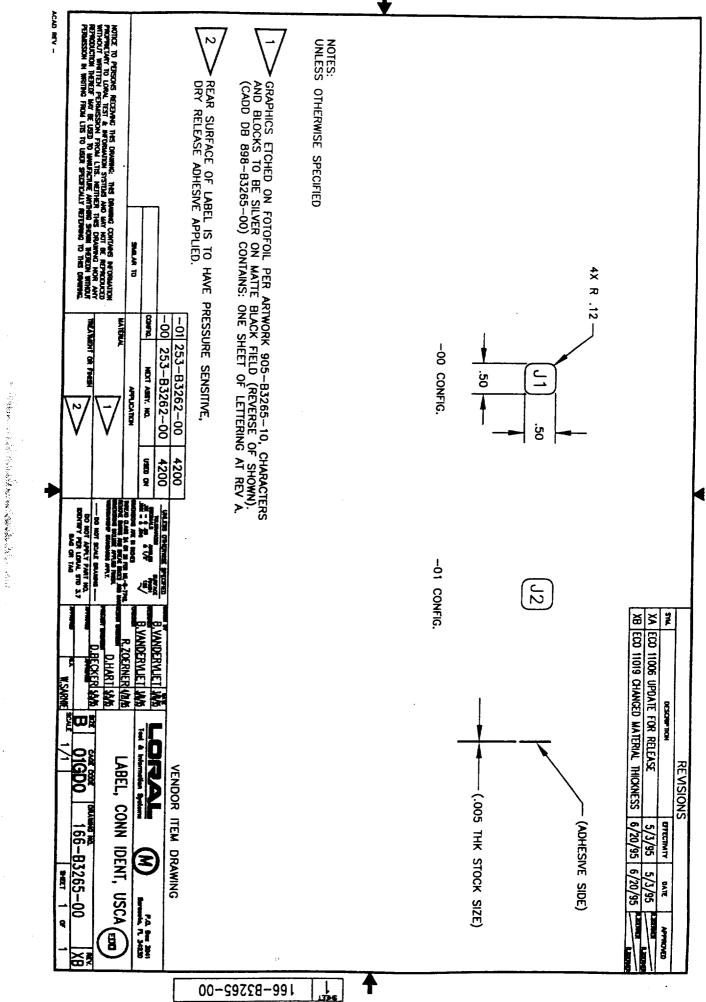

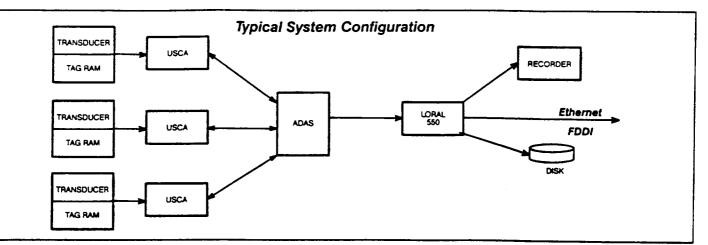

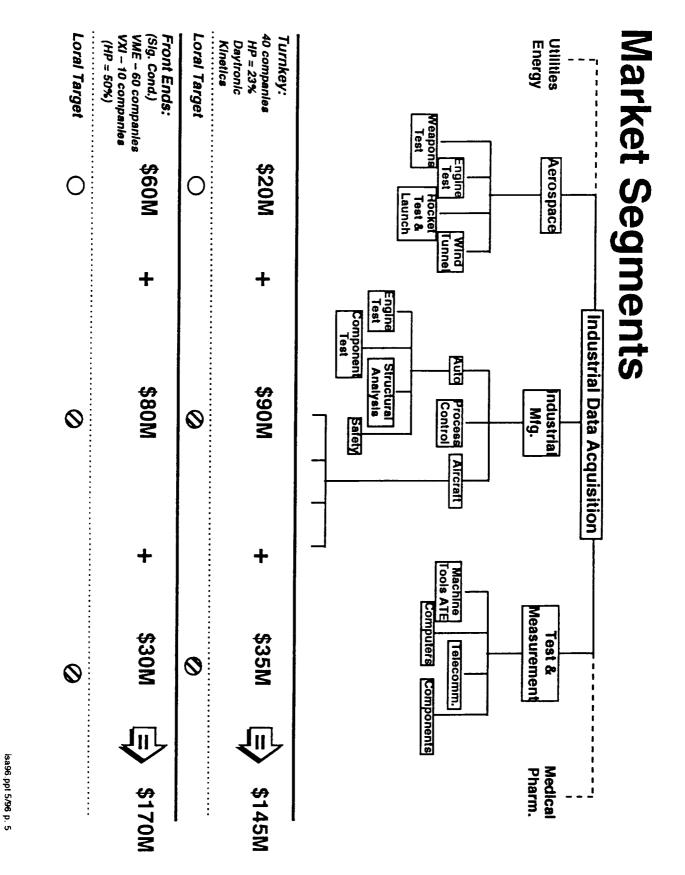

The Technological Research and Development Authority (TRDA) and NASA-KSC entered into a Cooperative Agreement in March of 1994 to achieve the utilization and commercialization of a technology development for benefiting both the Space Program and U. S. industry on a "dual-use basis". The technology involved in this transfer is a new, unique Universal Signal Conditioning Amplifier (USCA) used in connection with various types of transducers. The project was initiated in partnership with I-Net Corporation, Lockheed Martin Telemetry & Instrumentation (formerly Loral Test and Information Systems), and Brevard Community College.

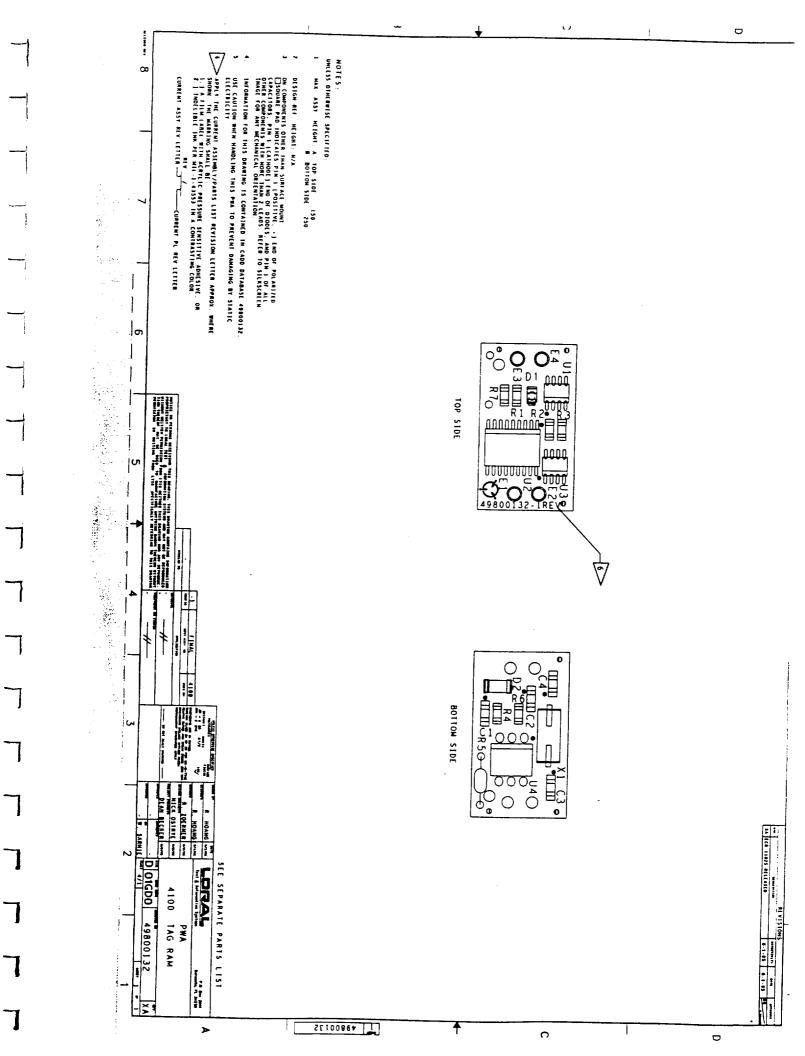

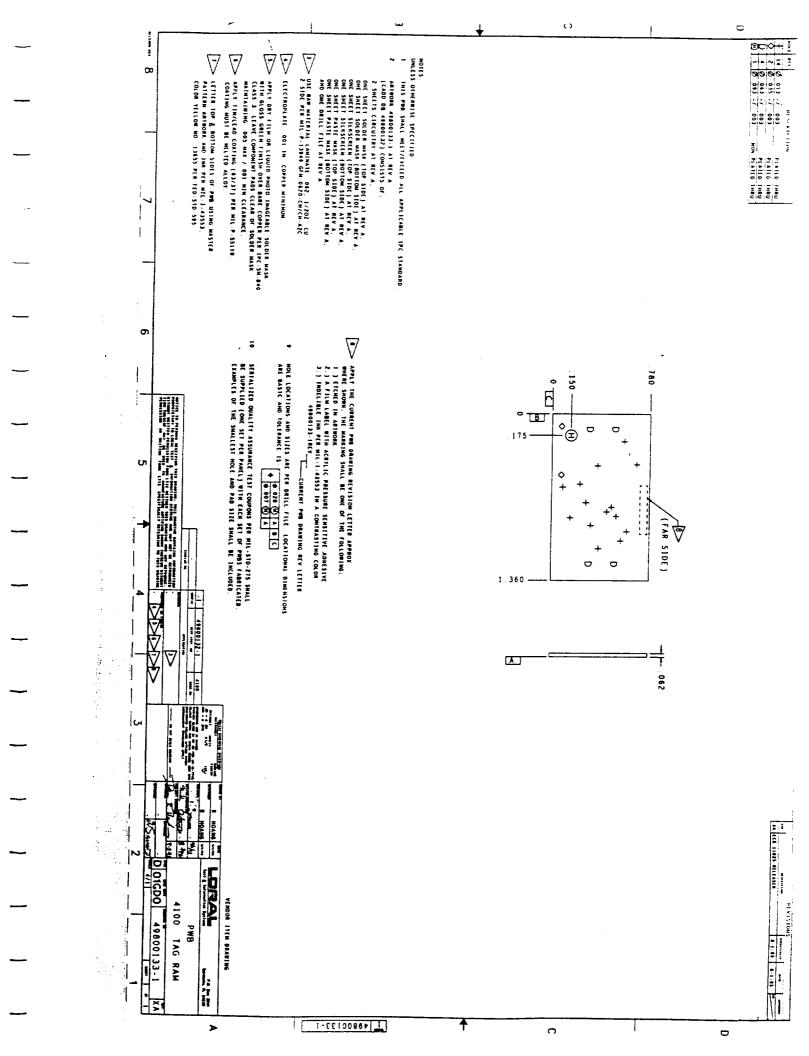

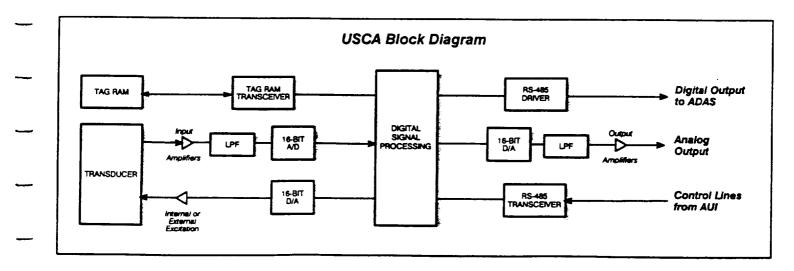

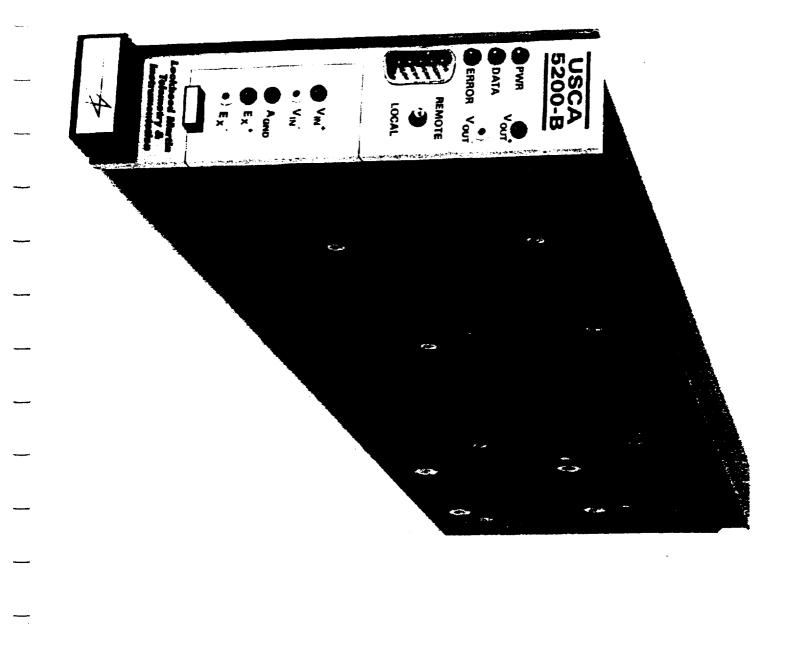

The project consists of designing, miniaturizing, manufacturing, and testing an existing prototype of USCA that was developed for NASA-KSC by the I-Net Corporation. The USCA is a rugged and field-installable self (or remotely) - programmable amplifier that works in combination with a tag random access memory (RAM) attached to various types of transducers.

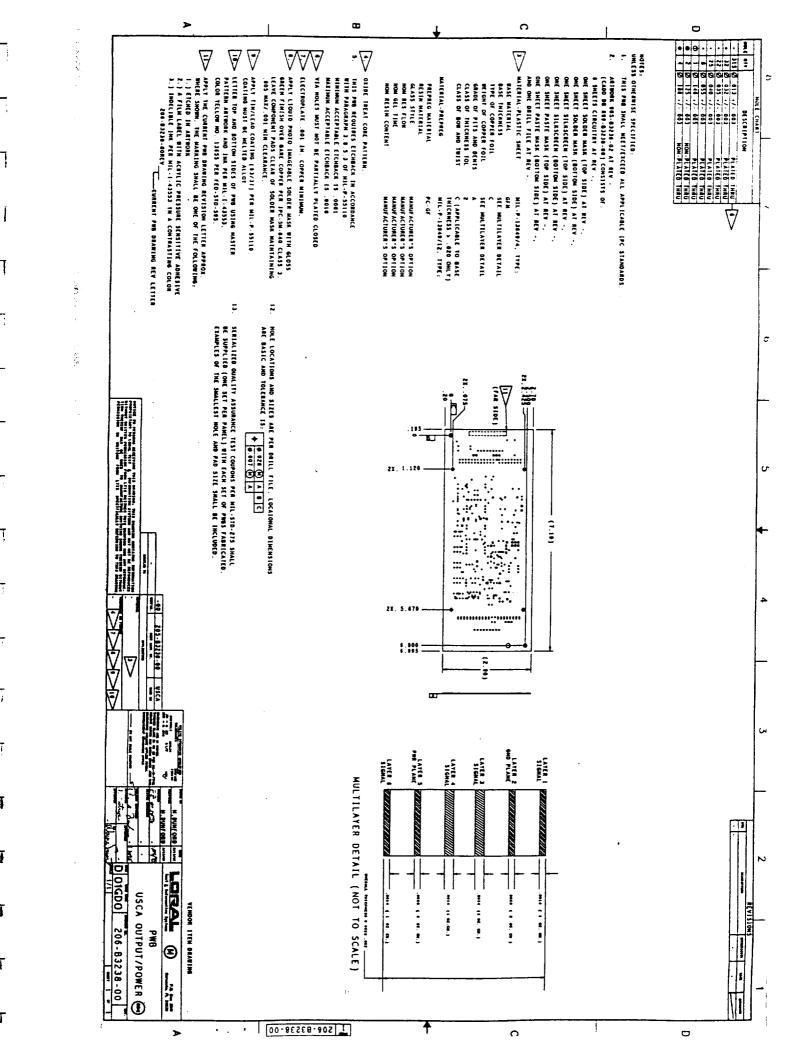

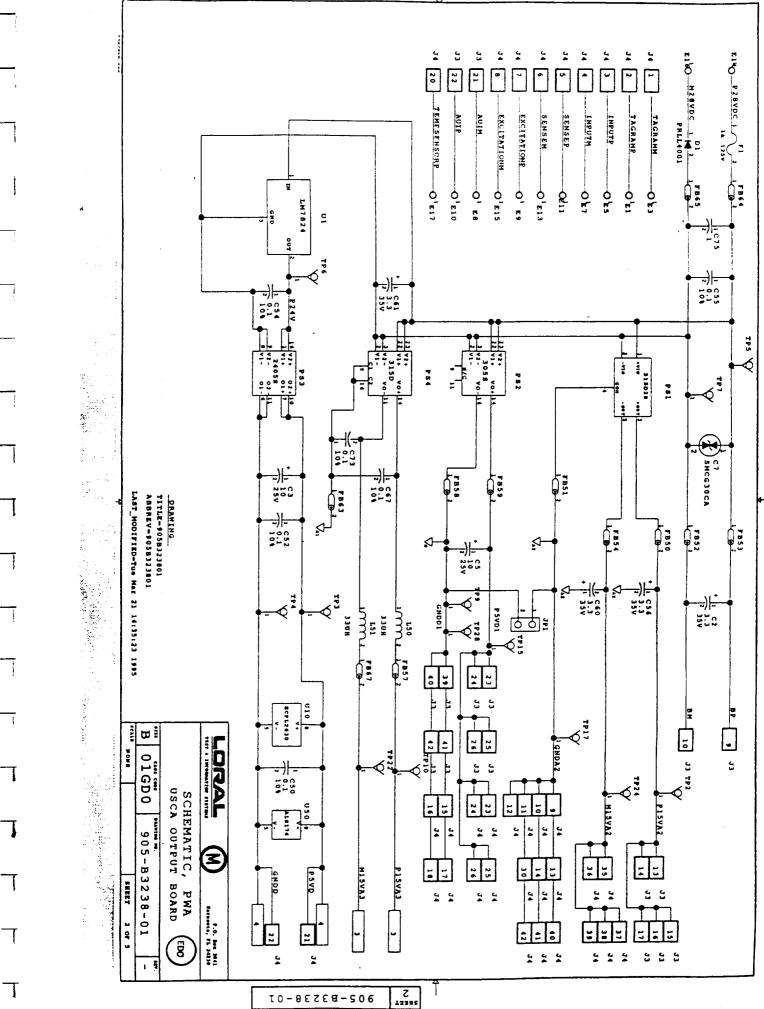

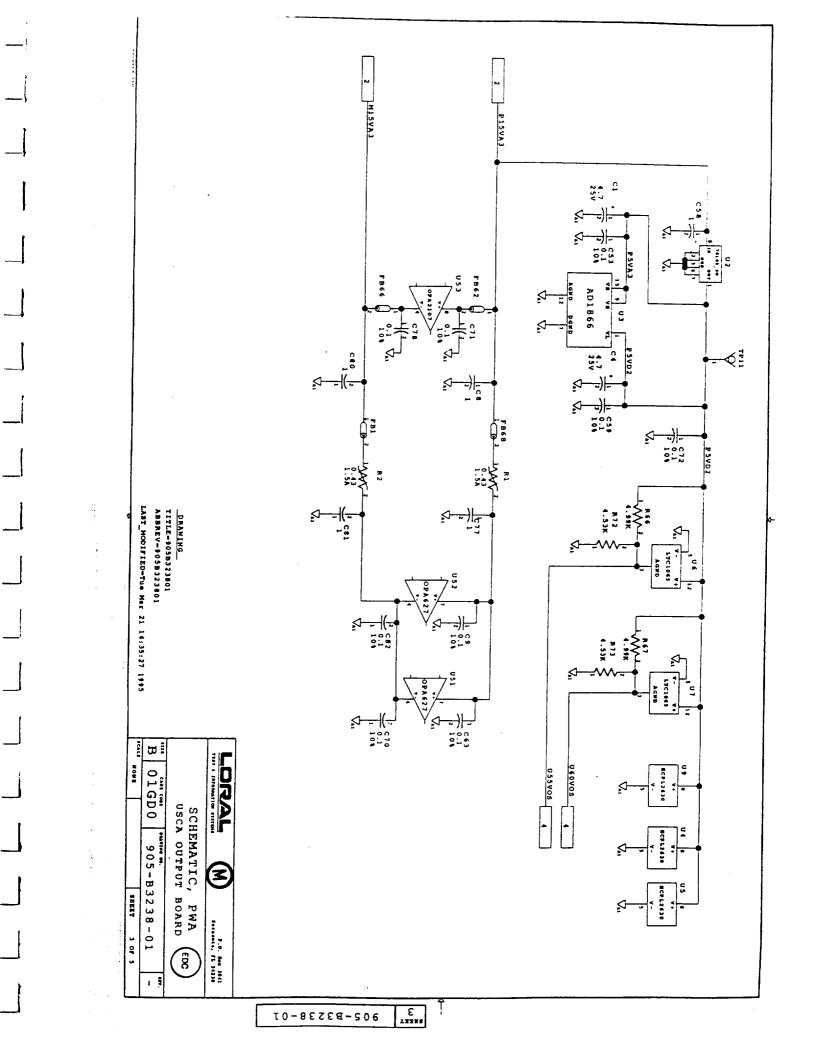

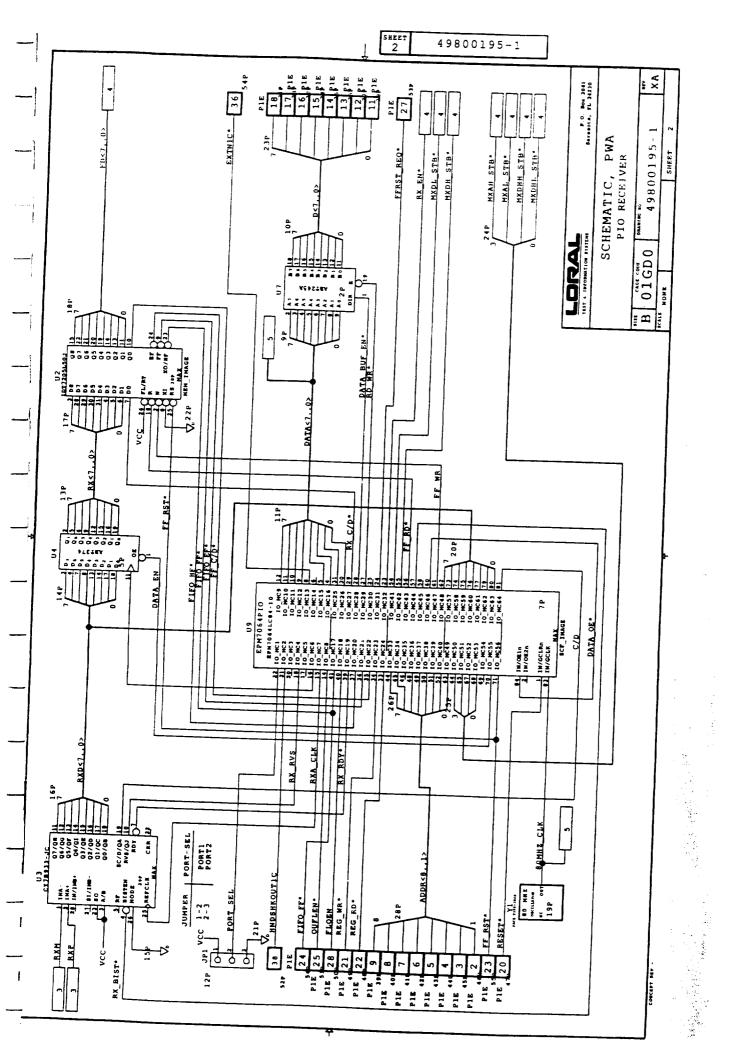

In September of 1994, the project was modified and extended to also include the development of the Advanced Data Acquisition System (ADAS). The new products developed as part of ADAS includes a USCA Controller/Input card, an ADAS Output card, and the operation software for the ADAS. The ADAS project completes and complements the USCA commercialization project.

Under this co-funded partnership, Loral/Lockheed Martin provided final design assistance to I-Net to assure compatibility with standard manufacturing processes, manufacture both government and non-government (commercial) versions of USCA and ADAS, provide the government version to TRDA for NASA-KSC testing, and place the commercial versions on the open commercial market.

#### II. PERFORMANCE

1

Project performance was tracked by attainment of established Milestones. The Milestones were adjusted several times through agreement of all partners. Changes to the Milestone schedule were necessitated by various design changes incorporated along the way in an effort to enhance the project. The final Milestone Schedules for both the USCA and the ADAS development are included as Attachment "A".

As of October 1996, all USCA and ADAS Milestones have been completed. TRDA had numerous conversations/meetings with Lockheed Martin and I-Net participants to confirm attainment of milestones. TRDA requested a final written project status report from Lockheed Martin, and received this report in March '97. This final report and the other written progress/milestone reports are provided in Attachment "B" of this report.

### Ш. TRDA PARTNERSHIP TASKS

1

The tasks performed by TRDA under this partnership arrangement are summarized below-

- (1) TRDA provided co-funding of the project in an amount equal to the co-funding provided by NASA-KSC.

- (2) TRDA provided the services of staff and professional consultants to provide for the proper implementation and business and technical management of the project Executive Director Frank Kinney and Business Manager Matthew La Vigne provided oversight and direct interface with all project partners. Associated clerical/secretarial support was also provided. Regular contact was maintained with all partners both via telephone and visits/meetings. Additionally, TRDA retained qualified technical support (via contractual relationship with Mr. Tom Davis) to assure the technical components of the project were being sufficiently managed.

- (3) In March of 1994, TRDA negotiated and contracted with Brevard Community College (BCC) to provide required assistance. BCC assisted in the administration of subcontracts and in the hiring of qualified college co-op students to support the project. Students from Florida Tech, the University of Central Florida, and Bethune-Cookman College were hired through BCC to assist project engineers in USCA and ADAS development.

- (4) TRDA served as the main interface and point of contact for all partners. Periodic site visits to Lockheed Martin's (Loral's) Sarasota facility took place, as well as numerous meetings in the local area. Regular contact is maintained with project engineers, managers, and contract personnel, as well as project management personnel at BCC and lead technical personnel at KSC.

- (5) Progress reviews took two forms: formal and informal. Formal reviews were made in conjunction with the submission of established Milestone Reports. On an informal basis, regular contact with project personnel enabled us to keep abreast of the work being performed on a continual basis.

- (6) Performance schedules take the form of agreed upon Milestone Schedules. These schedules have been mutually established by all partners. The Milestone Schedules were modified several times to meet expected performance. TRDA oversaw the schedules and confirmed that changes were both reasonable and required.

- (7) TRDA acquired reports as per the Milestone Schedules. These amounted to reporting requirements in excess of quarterly reports, however, we felt they were necessary to assure and track performance. These reports, as well as other appropriate documentation, were submitted to NASA in our required Performance and Summary Reports.

(8) TRDA submitted the required cash transaction reports to NASA to provide for their agreed to funding of the project, and have maintained appropriate records/files in connection with this project.

#### IV. SUMMARY

Although the USCA/ADAS dual-use project took longer and was more expensive than originally planned, we should all be extremely pleased with the results. Lockheed Martin Telemetry & Instrumentation (LMTI) believed in the potential of the NASA technology from the outset and therefore invested heavily in the project to ensure its success.

Through the partnership, NASA-KSC and LMTI have successfully completed a transfer of NASA technology to a commercial manufacturing environment. Commercial products are now being produced and delivered to NASA by LMTI, and the products have been introduced to the commercial marketplace. While the product launch is still in its infancy, marketplace reaction is very encouraging.

This project was a true example of partnership. The cooperation between all parties was been exceptional. KSC participants have expressed their pleasure with the cooperation they have received from LMTI concerning all elements of the project, from design, to testing, to manufacturing. Likewise, LMTI has stated that they have never participated in a project with the level of cooperation and teamwork that they experienced with the USCA/ADAS project. All partners should be commended for their efforts and participation in this project.

TRDA wishes to express our appreciation to NASA-KSC for their tremendous cooperation and support in this successful dual-use commercialization.

# **ATTACHMENT "A"**

\_\_\_\_

\_\_\_\_

\_

\_\_\_\_\_

<u>ب</u> ډ

\_\_\_\_;

<u>\\_\_</u>

USCA MILESTONES ADAS MILESTONES

# USCA COMMERCIALIZATION PROJECT (TRDA #405) MILESTONES FOR PAYMENT

۹

| •                                                                                                                                                                                            |                                                  | •                                                                                                                                                  | •                                                                                                                                                                                                                      | •                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Complete final design package for Loral Commercial Version of USCA. This<br>Loral Commercial Version of USCA will be a Loral Standard Component and will<br>be available as a procured item. | Complete design of Commercial Version 1 of USCA. | Release final Version 3 USCA design package. This version will be released as a Loral Standard Component, and will be available as a catalog item. | Complete manufacturing and deliver to TRDA five copies of design Version 3 USCA's. These Version 3 USCA's will be manufactured according to the final approved Version 3 design contained within the Loral CAD system. | Complete the incorporation of the final Version 2 USCA design package, released by NASA on April 29, into the Loral CAD system. Provide CAD design package to TRDA. | Deliver to TRDA electrical and mechanical components inputs for final<br>Version 2 design of USCA. Provide this information with component<br>descriptions, part numbers, etc. necessary for NASA to complete Version<br>2 design package. This information of electrical and mechanical components<br>will be focused on improving the manufacturability of USCA and reduce the<br>product cost. | ACTIVITY COMPLETED/DELIVERABLES |

| 20%                                                                                                                                                                                          |                                                  | 20%                                                                                                                                                | 20%                                                                                                                                                                                                                    | 15%                                                                                                                                                                 | 25%                                                                                                                                                                                                                                                                                                                                                                                               | % OF BUDGET TO BE PAID          |

- ī

# ADAS COMMERCIALIZATION PROJECT (TRDA #410) MILESTONES FOR PAYMENT

•

|   | ACTIVITY COMPLETED/DELIVERABLES                                                                                    | % OF BUDGET TO BE PAID |

|---|--------------------------------------------------------------------------------------------------------------------|------------------------|

| • | Complete the ordering of the materials for the Input Card manufacturing and testing Input design package to Loral. | 25%                    |

| • | Complete the CAD Schematic Design of the Output Card                                                               | 15%                    |

| ٠ | Complete Output Card PC Board fabrication.                                                                         | 15%                    |

| • | Complete the CAD Schematic Design of the Input Card.                                                               | 15%                    |

| ٠ | Complete the Input Card PC Board fabrication.                                                                      | 10%                    |

| • | ADAS System test. In conjunction with NASA-KSC, complete final design,                                             | şn, 20%                |

٠

•

.

testing, and acceptance of the total ADAS.

-

-7

Т

T

T

Т

Т

Т

# ATTACHMENT "B"

# **MILESTONE/PROGRESS REPORTS**

-

1

-

·····

Fr: Dean R. Becker Re: USCA milestone 1

1

Т

T

LDS has delivered inputs on the electrical, mechanical, and component elements of the NASA USCA design. We have provided information with component descriptions, part numbers, etc. necessary for NASA to complete the version 2 design. We have also assisted with the overall design of the USCA as well as the system with which it operates. See the attachment A. Included is an updated project schedule for the USCA development. See Attachment B. Tasks to be accomplished with NASA **Discuss and identify actual specifications Electrical operational specifications** Analog I/O Digital I/O MTBF Construction Power Frequency response Isolation EMI **Discuss circuit design** Block diagram hiarchial level System I/O definition First level internal Details of first level blocks Identify schematic to these details Discuss certain schematic details Detailed parts list (with full part numbers) Identify questionable part descriptions Surface mount versions **Discuss certain component selection** Mechanical relays **Potentiometers** Monostable multivibrators **Temperature sensors** Crystal **Power** supplies Fuses Special hybrid IC PALs? Gaps? Discuss firmware program flow Tag RAM format definition Tag RAM programmer definition Micro controller Firmware **DSP** Firmware **Discuss setup sequence and defaults Discuss mechanical design** Boards Number Placement Interconnects Components Ferrite beads

Connectors Shock and vibration damping Shielding Shape Material **Discuss current and future testing** Written test procedures EMI/RFI Environmental **Discuss cost and schedule Re-draw** schematics Enter parts definitions into Cadence Possible new parts libraries Worst case simulation? Analog **Digital** Plans and expectations for the prototype under development NASA built Plans and expectations for final prototype Loral built Final unit cost Discuss the rolls of NASA and Loral NASA Electrical design Mechanical design Test definition Fabrication of prototypes Loral Transfer of all design information Integration of this information into development system Integration into manufacturing system Last prototype fabrication Production fabrication

Definition of commercialized product

Design and fabrication of commercialized product

I.version 1

-1

-1

Т

T

T

Т

1

- A. generate true set of specs

- 1. (3.3.2)MTBF

- 2. (3.5.1)Power 100 mA

- 3. (3.5.8)Frequency Response 150 Hz

- 4. (3.5.15)driving 100000 ohm output

- 5. (3.5.16)Isolation 100 Megaohms

- 6. (3.5.18)Insulation 100 Megaohms for connectors

- 7. (3.5.23)Cable Length

- 8. (3.5.24)Common Mode Rejection (still Valid)

- 9. (3.6.3)EMI Spec

- B. address multichip module

- C. walk thru design with I-Net

- D. PDR/CDR on version 1 todays version versus specs

- E. Testing on todays version

- 1. Preliminary Electrical Requirements Testing

- 2. Preliminary EMI

- 3. Preliminary Vibration analysis

- 4. Component Analysis availability- reference Multichip module

- 5. Temperature Analysis

- II. Identify SAMS info

- III. Generate USCA working environment for support

- A. compiler

- B. DSP stuff

- C. Analog Library

## IV. Generate buildable set of

- A. Schematics

- 1. New Bodies

- B. Board Layout

- C. Block Diagrams

- D. Parts list

- E. Parts Description

- F. released Software

- 1. uprocessor

- 2. DSP

- 3. SAMS

- 4. Tag Ram Programmer

- V. MTBF analysis

VI. System Level Interface and Documentation

VII.version 2

- A. Liason work on USCA

- 1. Mechanical Design (includes form factor)

- 2. Electrical Designs

- 3. Components

- B. Version 2 testing

- 1. Electrical Testing

- 2. Mechanical Testing

- 3. EMI Testing

- 4. Vibration Testing

#### VIII. Version 3 (nasa final version)

- A. Liason work on USCA

- 1. Mechanical Design

- 2. Electrical Designs

- 3. Components

- 4. Cost

- **B.** Version 3 testing

- 1. Electrical Testing

- 2. Mechanical Testing

- 3. EMI Testing

- 4. Vibration Testing

- IX. Loral's Commercial Version

- A. generate specifications

- 1. Form factor

- 2. cost

- **B. Preliminary Design**

- C. Design Review

- **D.** Prototype Build

- E. Prototype test

- F. Design Modifications

- G. Critical Design Review

- H. Final Version Build

- I. Final Version Test

- J. Release

T

T

Т

T

T

1

T

# **USCA PDR TOPICS**

T

**Specifications Electrical specifications** Analog I/O Input signal level Voltage: -10V to +10V Current: Max: Typ: Bandwidth: DC to 10kHz Output signal level Voltage mode: 0 to +5 VDC Current: Max: Typ: Bandwidth: Voltage mode: -5 to +5 VDC Current: Max: Typ: Bandwidth: Voltage mode: 0 to +10 VDC Current: Max: Typ: Bandwidth: Voltage mode: -10 to +10 VDC Current: Max: Typ: Bandwidth: Current mode: 4 to 20 mA Voltage: Max: Bandwidth: Excitation signal level Voltage mode: Current: Max: Current mode: Voltage: Max: **Digital I/O** Tag RAM Input Voltage: **Current:** Bit rate: Tag RAM Output Voltage: **Current:** Bit rate: SAMS Input Voltage: Current: Bit rate: SAMS Output Voltage: **Current:** Bit rate: Output signal Voltage: Current: Bit rate:

Other specifications **Detailed parts list** Surface mount For temperature sensors For gaps For ferrite beads Specific areas of concern Potentiometers: change to EEpots Monostables to be eliminated Mechanical relays: changed to optical Smaller power supplies Parts description book Detailed data sheets for each part used Schematics, latest version Tag RAM format Tag RAM programmer Hierarchical block diagram for hardware System I/O definition First level internal **Details of first level blocks** Identify schematic to these details **Discuss certain schematic details** Hierarchical block diagram for software Microprocessor flow diagram Top level **Detailed level** Initialization flow and defaults: State diagram **Digital output definition** Bit rate Structure Number of bits per word: Header: Error detection/correction: Test procedures Electrical Environmental EMI Discussion SAMS Identify assembler/compiler for microprocessor Identify DSP software package Walk through design from block diagram through schematics Mechanical considerations **PCBs**

Enclosure Mounting Diagnostics Power up Continuous Integration path into Loral manufacturing Schematics PCB layout Parts placement for auto insertion Mechanical drawings and fabrication

--|

- |

-1

----

-

7

Universal Signal Conditioning Amplifier System Universal Signal Conditioning Amplifier - USCA Self Awareness Measurement System - SAMS Advanced Data Acquisition System - ADAS Tag RAM Programmer - TRP Pro 550 interface

PDR Meeting with NASA, I-NET, TRDA - Feb. 15, '94

For this meeting I brought along the following list of things to be covered: USCA PDR TOPICS

**Specifications**

Electrical specifications - Specifications are still in work, some details of the digital and analog I/O are available.

Analog I/O Digital I/O

Other specifications

**Detailed parts list**

Surface mount

For temperature sensors - Temperature sensors are to be eliminated inside the USCA.

For gaps - These do not exist but the thought is to have this part of the circuitry on a separate round PCB at the output end of the USCA and to have the other PCBs plug into it.

For ferrite beads - These exist and I have given some data sheets to Pedro on this.

Specific areas of concern

Potentiometers: change to EEpots - These will be eliminated with the new calibration scheme.

Monostables to be eliminated - They will not be used.

Mechanical relays: changed to optical - All have been changed or are being changed to optical.

Smaller power supplies - Pedro is looking into this to see what the actual circuit power requirements are.

Parts description book

Detailed data sheets for each part used - This is in work for the USCA version 2.

<u>Schematics, latest version - Pedro has given me the latest schematics.</u> <u>Tag RAM format - This was given to me during the SAMS discussion</u> <u>with Carl.</u> Tag RAM programmer - Still to be defined, this will probably be a good co-op job to do.

<u>Hierarchical block diagram for hardware - Pedro has given this to me</u> <u>along with the detailed discussion of the USCA hardware.</u>

System I/O definition

First level internal

Details of first level blocks

Identify schematic to these details

Discuss certain schematic details

<u>Hierarchical block diagram for software - James has given this to me</u> <u>along with the detailed discussion of the USCA firmware.</u>

Microprocessor flow diagram

Top level

**Detailed level**

Initialization flow and defaults: State diagram

Digital output definition - Curtis of NASA is assigned to this task, this is still in work.

Bit rate

~7

-1

-7

Structure

Number of bits per word:

Header:

**Error detection/correction:**

<u>Test procedures - Formal procedures are down the road with USCA</u> <u>version 2, however preliminary procedures exist for electrical and for</u> <u>environmental. The procedure for EMI will be done by another group at</u> <u>NASA.</u>

Electrical

Environmental

EMI

**Discussion**

SAMS - Discussed details with Carl, System level concepts to be discussed with Bill Larson.

Identify assembler/compiler for microprocessor - Done Identify DSP software package - Done

Walk through design from block diagram through schematics - Done

Mechanical considerations - *I discussed my findings with LDS manufacturing.*

PCBs - Consider three rectangular boards, surface mount on both sides, plugging into each other, and plugging into a common round mother board at one end with lightning protection at that end. (This is of course for version 2.)

Enclosure - Plan for a stainless steel enclosure slightly larger than the example we had at LDS for the temperature bulb. Mounting - Consider a direct connect of the mother board to the MS connector at that end and an internal connector for the MS connector at the other end to avoid internal cables.

# Diagnostics

Power up - Pedro and I will discuss this. Continuous - This will be accomplished with the continuous calibration technique to be used.

Integration path into Loral manufacturing

Schematics - These will have to be re drawn into the LDS system. A discussion with Mike Nastanski confirmed that this is the most efficient way based on his previous experiences. We do not intend to do circuit simulation.

PCB layout - PCBs will be laid out by NASA / I-NET for the version 2 USCA. Placement for parts and critical circuits will be entered by hand at LDS and non-critical digital circuits will be auto routed. Net lists will come from the re done schematics. Parts placement for auto insertion - Since we are entering the PCBs into the LDS system this will follow normally. Mechanical drawings and fabrication - NASA will supply LDS with basic mechanical drawings which LDS will have to redraw to LDS standards.

# The following are points which came out of the meeting:

The qualifications of the part time students needs to be defined. SAMS and the TRP are an integral part of the program and need to be brought in as an addendum to the contract.

The ADAS and APME (APME is part of the ADAS but its funding is separate)

ADAS funding is for FY '94

APME funding is for FY '94 & FY '95

Meetings are needed to discuss the following:

Mux bus extender / 550 interface

USCA digital output format

Discussion of:

-

System overview concepts

Lightning protection actually needed

Power supply specs - max.

SAMS format description needs to be defined.

Tag RAM Programmer schematics and software need definition. This needs to be coordinated with the Calibration facility Need to do cable testing at the pad for long cable runs between

USCA and the pad collection point. This is to find out how the present cables which are used to monitor the analog voltages

from sensors will work with the digital output signal the USCA will eventually send.

Software used for USCA

Monarch DSP - 904 371 2567 (\$349) Dallas semiconductor DS5000TK V3.1 evaluation kit 8051 ASM Archimedies V2.02 C51 Compiler V4.23B Xlink V4.43

Following this meeting I discussed the details of the USCA software design with the NASA designer (who I only know at this point as James).

The following day I went with several of their engineers to Pad A to do testing on one of the long cable runs between USCA and the collection point. We focused on a cable from the liquid oxygen pumps to the pad. Since the cable was originally intended for the transmission of low frequency analog signals its characteristics for carrying the digital USCA output were unknown. Definition of the USCA output depended on the cables characteristics as they are not to be replaced. We found that the frequency response exhibited a standard LC roll off starting around 600 kHz. We also rigged up a TDR to look for impedance anomalies in the overall cable run. This testing took up the entire morning.

Following this I discussed the details of the SAMS design with Carl Hallberg of I-NET.

Next I discussed design details of the USCA hardware with Pedro Medelius. We also discussed a new self calibration approach and USCA diagnostics. Software documentation for USCA, SAMS, etc. - Two different students could document the software for the USCA and possibly expand on the software for the SAMS.

**Development** of units

<u>SAMS</u> - Once SAMS is a well defined system a student could help with prototyping and documentation.

<u>Tag RAM Programmer - This would be a very good student</u> project for both hardware and software.

Basically co-op students will be needed with the following backgrounds:

<u>Mechanical design, possibly with Auto CAD</u> <u>Electrical design with microprocessor</u> software hardware

The new method of calibrating the USCA automatically using the A / B channel method will be implemented in the version 2 USCA as discussed with Pedro previously.

An expanded list of possible SAMS commands for USCA needs to be established. - *James will do this by March 1, '94.* An expanded definition for Tag RAM utilization needs to be

developed. - To be done in 2 weeks.

Diagnostics internal to the USCA

Feed output voltage back to input - This presents a special problem in the USCA due to the galvanic isolation required between the input and output. The output voltage cannot be monitored by the input of the USCA, however the excitation voltage can be used to test the input. The excitation voltage will be controlled by the DSP in the version 2 USCA and by this creates an easily controlled situation for testing the input. The output voltage of the USCA will need to be checked in the lab but will not be self correcting while in use. This is not a major concern as the digital output will be replacing the analog output in the future.

Self calibration - A dual input path will be used where one path is switched to a standard voltage while the other is in use. The two will flip flop in time thereby maintaining calibration for any gain or offset adjustments.

Excitation voltage / current to input - This will be used as just described.

SAMS / Tag RAM Interface - This will not have a special test. If the SAMS cannot communicate then this interface has a problem indicating that the particular USCA needs to be repaired. Multiple frequency sinusoidal waveform for DDF testing - This can now be done using the excitation voltage. These frequencies need to be defined. Control test - A power up test can be done to give credibility to the operation of the micro controller.

Digital output test - This could be feed back into the DSP using optical isolation and a test pattern. The utility of this is somewhat questionable.

USCA digital output definition - This is being worked on by Pedro and Curtis.

The Tag RAM device is a sole source chip made by Dallas semiconductor. The entire system evolving out of the USCA is revolving around the Tag RAM and its unique format and control. I feel that with the dependence on this part being so critical an alternate approach should be explored should Dallas decide by their whim not to make this part in the future. - Yoseph will look into this.

The Tag RAM only uses one fourth of its memory space. The other areas have different access requirements but need to be used as well. The current one forth of the device is already full based on current information definition. - *This will be done.* What results have been found from the temperature and EMI tests. - *The results from the temperature tests are good. Due to the results of this other DC to DC converters will need to found.* No other problems surfaced. EMI testing has not been done. This is controlled by another NASA lab and must be time phased to meet their needs.

A project plan needs to be developed for: - This is recognized and is TBD.

SAMS TRP

ADAS

Т

Bring the serial interface from the micro controller out of the USCA for diagnostics and setup. - *Pedro and I discussed the possibility of bringing this out on two 'unused' pins on the MS output connector.*

Use of the Dallas 5000 micro controller vs. an 8751

The 5000 requires software to be loaded into its battery backed up RAM after manufacture.

This chip is not available in surface mount and is very tall.

The 5000 costs much more than the 8751

The 8751 will work in this application with no need to rewrite the basic functional software.

Pedro agrees with these points and is looking into using the 8751 or an equivalent.

What is the status of the Tag RAM board layout and component selection? - This is in work as the mechanical relay needs to be replaced with an optical relay.

Universal Signal Conditioning Amplifier System Universal Signal Conditioning Amplifier - USCA Self Awareness Measurement System - SAMS Advanced Data Acquisition System - ADAS Tag RAM Programmer - TRP Pro 550 interface

-

T

T

<u>Meeting with NASA, I-NET, Grumman - Feb. 23, '94</u> <u>No major problems were uncovered, however the following points were</u> <u>discussed:</u>

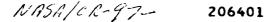

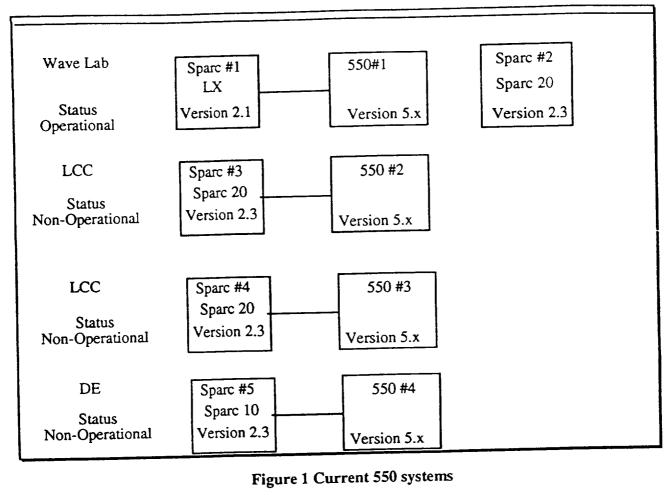

Considering up to 12 Bit Sync / Decoms in the PRO550 at LCC (Launch Control Center). These would have fiber optic links as inputs.

Fiber optic link bandwidth is 2 MHz now but is apparently only limited by the transmitters / receivers now being used. The fiber optic link output will be coming from the individual ADAS units. USCA linearization was only up to 5th order at maximum input sample rate. This has been increased to 7th order.

Grumman expressed concern over the possible effects of the DDF FIR filter coefficients windowing. This is a 512 tap filter and the coefficients are being computed by an algorithm such as Parks - McCleilan so the window effects are not likely to be a concern. Pedro is going to run an example to show that the effects of this on the data are below the effective quantization level.

A question was raised on the jitter specification for the excitation pulses from the USCA. This needs to be specified but will likely not be a problem as the excitation voltage or current in version 2 of the USCA will be controlled by the DSP chip instead of the micro controller.

Mike Maxwell of Bionetics was also at this meeting to represent the NASA calibration facility. He was asked to give any input with respect to the Tag RAM Programmer interface and existing calibration facility equipment.

Following this meeting I discussed some other concerns with Bill Larson. Pedro was called in for parts of this. For this meeting I brought along the following list of things to be covered:

Capabilities and requirements for the student co - ops Mechanical - A student working at NASA could document with drawings the version 2 USCA enclosure. What are the specifications for the filters being defined for the DDF? - Pedro will supply this.

The LDS proposal has been received by NASA and is in their accounting department.

NASA can have their mechanical drawings done in Auto CAD. We need to see if we can take this directly into our system. We need to supply them with example drawings of our standards. This could be done by a co-op student at NASA.

I explained to Bill Larson the operation of the CMUX and how it could be used for the ADAS. He seemed very interested and requested documentation be sent immediately for Curtis to read. I will be gathering together the cost of parts as they can best be defined at this point to come up with an estimate of cost for the USCA.

I was given a schedule on the development of the SAMS. The current prototype is being built and considering several facets of the project this is just as well. This will test out the driver circuitry for the follow on which may be a significantly different over all design. The system philosophy needs to be discussed further.

LDS needs to get contractually involved with the entire system surrounding the USCA.

-

Т

T

T

LDS has approval to use the USCA as a paper for conferences.

# From: Dean Becker Telecon with Bill Larson on March 10, '94

Environmental testing is progressing on the version 1 USCA Temperature testing -20 to +50 degrees C.

Unity gain and 10X gives accuracy of 15.5 bits

Tag RAM

An alternate chip has been found for this critical purpose Less cost

Board layout of equal size

SAMS PCBs have gone out for fabrication

They will be stuffed next Friday

There will be an in house (@NASA) design review for the SAMS on the 21st of March

The USCA contract

Scheduled for completion on Monday March 14

Should be released to TRDA the next day

There was an internal design review for the TRP (Tag RAM Programmer)

It is planned to be a black box with a serial interface

Can be used by any computer system

**Tag RAM Partitioning**

T

Т

There are 4 sections to be used

The first part will contain Calibration lab information such as coefficients and calibration due date

The next part will contain information such as desired filter information

The rest is still undefined but this leaves plenty of room for expansion.

The Digital output section definition is still in work The Specifications are in work and on schedule From Dean Becker March 11, '94 USCA Status

> First milestone is April 4,'94 LDS is to provide NASA with component selection advice <u>NASA has been given some information already</u> Alternative for Tag RAM <u>System critical single source item</u> 8751 substitute for DS5000 <u>Less expensive, surface mount, low profile</u> Help with Digital output definition <u>Cable testing, technical discussions, component selection</u> Help with diagnostic methodology Help to identify and eliminate one shots, pots, mechanical relays, etc. <u>A list of surface mount parts and prices is being generated at</u> LDS based on the version 1 USCA to be given to NASA

> > We have also helped them with suggestions on physical and mechanical mounting and placement.

We understand all details of the USCA schematics and the flow of the internal control firmware. We have also gone through the preliminary specification in detail.

We need to be involved in all of the system aspects that surround the USCA.

USCA

This is well defined as per the contract and the schedule.

SAMS

We will need a SAMS for our customers for the commercialized version. This is for the NASA version 3 type.

Probably best to guide this design then use as is.

- ADAS Some funding in FY '94 then follow on in FY '95

- We have suggested to NASA that this be a CMUX. A new input card would need to be developed. We need to convince NASA that LDS should do this design.

- TRP

We will need this for any commercialized version. Likely that this will be done with the co-op help Best to use this design as is with our inputs on the way

550

1

T

T

We need to work with NASA and provide help on this as required.

The integration path into LDS manufacture has been identified.

Schematic entry will be redone at LDS Board layout will copy NASA boards and auto route as possible <u>We are working up a per unit price for the USCA</u> <u>The USCA contract should be released to TRDA March 15, '94</u>

-7

-7

-7

-1

From Dean Becker

March 22 and 23 meeting with NASA

USCA Notes:

We will need to create a test facility for the individual boards of the USCA for the time when we go into production.

NASA has done environmental testing.

Temperature testing: -30 to +50 degrees C.

Operational analog output with 1X and 10X gains.

An accuracy of 15.5 bits was obtained.

EMI testing not done.

To be done on the Version 2 USCA.

There will be no temperature compensation on the USCA.

With the dual calibration path it is not needed.

Sensors are not corrected for temperature by the USCA.

The Burr Brown D/A used for the excitation voltage is running too hot. It is being changed out for one that is smaller and costs less.

**Digital output:**

Curtis has breadboarded the design

It will be asynchronous with:

<u>1 start bit</u>

16 data bits

2 parity bits

1.5 stop bits

It will be implemented with the Phillips 87CE558 microprocessor or with a PAL by April 10.

I received a fax from Curtis regarding the design plan and direction.

Multi-chip module (MCM).

There is currently about a 50% reduction in the size of the circuitry using surface mount technology. Due to this the use of the MCM is questionable. The MCM requires a \$10k NRE.

Test procedures are 15% complete.

Environmental

Electrical

The Mechanical drawings are to be done later than indicated on the schedule. The schedule indicated completion at CDR. Releasing them 2 to 3 weeks later will not impact Lorals ability to fabricate version 3.

The replacement for the DS5000 will be the Phillips 87CE558.

Based on the Intel 8751

Has 32k of flash EPROM

The second source for the tag RAM is a chip set.

Cost is less than current tag RAM.

May use this instead of the current tag RAM.

Available from more than one source.

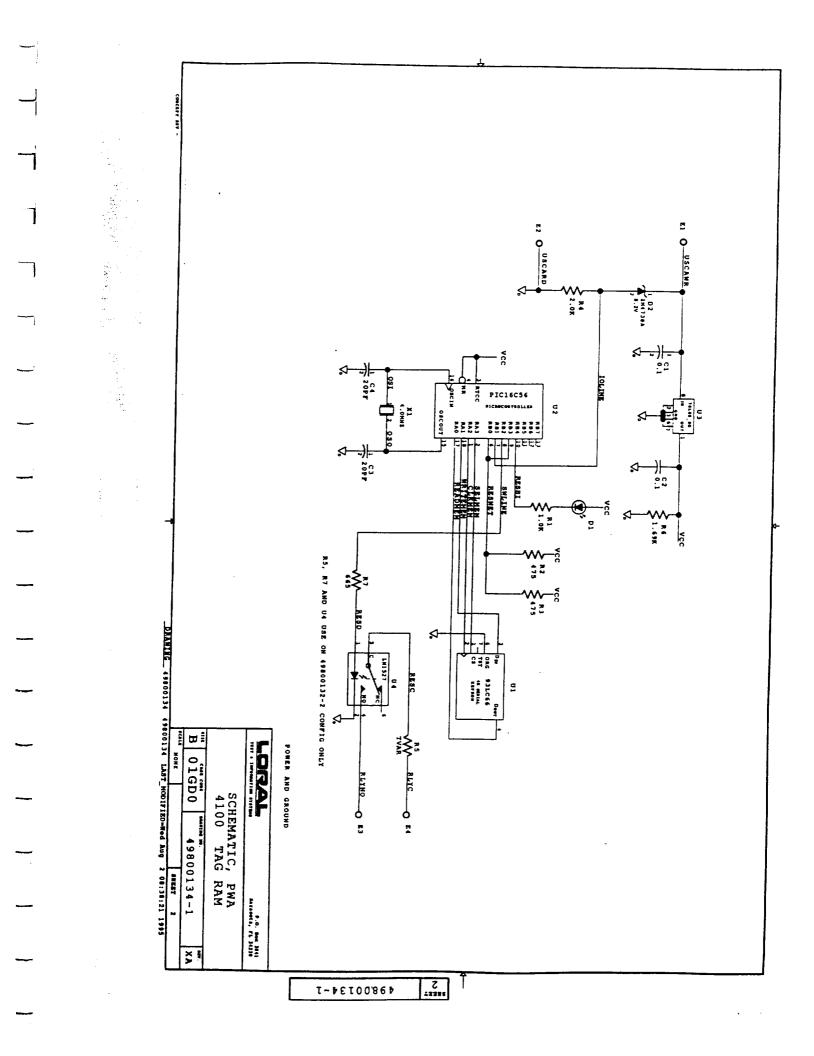

Microchip technology PIC16C56 8 bit RISC microcontroller.

<u>1K x 12 program EPROM</u>

<u>32 X 8 data RAM</u>

<u>12 I/O lines</u>

Microchip technology 93AA56 (256 X 8) CMOS EEPROM.

<u>SAMS notes:</u>

Ĩ

Í

T

T

T

NASA Discussed block diagrams (2 enclosed) for the SAMS. 3 SAMS PCBs are in at NASA as of March 18.

NASA will build one.

We will receive one.

We will procure the parts.

We will build for our future use.

NASA will test it for us.

It is to be put into an enclosure for marketing demos.

We are to receive the parts list by fax ASAP.

<u>Grumman gave a detailed description of the NASA sensor data</u> <u>acquisition, collection and distribution system.</u>

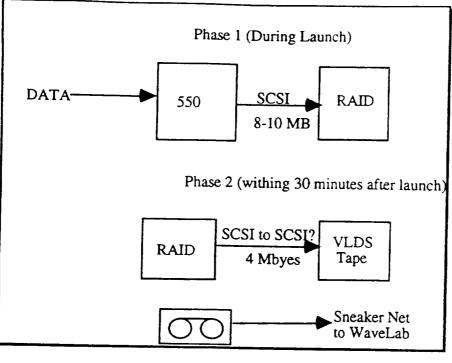

NASA KSC/PMS diagrams (2 enclosed) are the present system. Transducer data collection and distribution diagram (1 enclosed) is the future system.

NASA discussed three approaches to the Advanced Data Acquisition System (ADAS).

A NASA developed VME chassis at the pad

A 550 approach at the pad

A CMUX approach at the pad with data to the 550 at LCC

Each approach includes input cards for the USCA digital output signal. These cards would have 40 (TBD) channels of input each.

Considering Loral's recent experience in this area, NASA is inclined to go with a Loral design.

NASA wants a prototype by this October.

We will prepare a proposal within the next two weeks.

David Payne and I will visit NASA on April 6th and 7th

I will be interfacing with NASA for the electrical and mechanical design issues of the USCA.

We will be presenting NASA with a proposal for the ADAS.

# From Dean Becker April 6 - 8 meetings with NASA/I-NET

**USCA**

Received latest schematics and parts list Discussed areas which have changed

Input amplifier chain is now broken into 3 cascaded amplifiers instead of one. This allows calibration without the amplifier offsets becoming a significant part of the reading.

Input multiplexer now has the following inputs:

Input signal (differential)

Analog output signal (single ended)

+ Excitation (single ended)

- Excitation (single ended)

<u>Temperature (single ended)</u>

6.8 V Reference (single ended)

0.68 V Reference (single ended)

0.0 V Reference (single ended)

Microcontroller

<u>Currently using only EEPROM for program and external</u> storage.

Suggested using separate EPROM for program memory and EEPROM for external storage,

EEPROM could become altered in program space. USCA would not function

EEPROM would need to be unsoldered to reprogram. In this case the EEPROM could be a smaller memory size.

The EPROM is not an expensive or large item.

I-NET has tentatively agreed to this.

Combinational logic circuits could be replaced by PALs.

Reduced circuit size.

Flexibility for change and debug.

Mechanical design - Schematics are now organized by potential physical layout.

Four PCBs.

<u>I/O Protection</u> <u>Input Analog</u> <u>Output Analog</u>

Digital / Processor

LDS will look into possible surface mount connectors for interboard connections.

LDS will look into possible 2 bit parity code schemes for the digital output word.

#### SAMs

T

Ī

T

NASA has given LDS one set of the latest SAMS PCBs.

We will procure the parts and assemble the boards.

NASA/I-NET will modify to the current configuration and debug the boards.

We will use them for test and demonstration.

We also have 25 Tag RAM boards which may be assembled for test and demonstration.

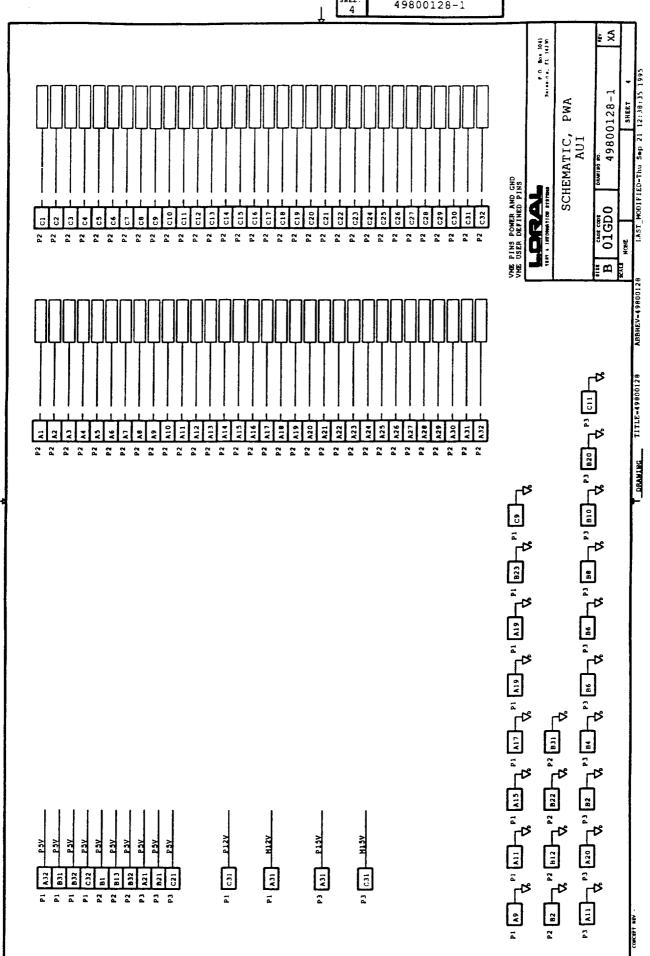

# Advanced Data Acquisition System (ADAS)

Three possible implementations proposed.

NASA preferred having a CMUX at the pad with data to a 550 at the LCC.

NASA requests a prototype by October '94 and production units by January '94.

Data decimation was discussed.

Decimation will be performed at the USCA

Data rate is expected to be 2 Megasamples / Second.

MLP requirements (there are 3 MLPs).

200 sensors.

Complete redundancy to the ADAS box level. (i.e. 1 USCA feeds 2 ADAS input channels.)

Pad requirements (there are 2 pads).

80 sensors.

Complete redundancy to the ADAS box level. (i.e. 1 USCA feeds 2 ADAS input channels.)

This is a total of 10 ADAS units

54 input cards (assuming 32 channels each)

10 bridge / time code cards

10 output cards

10 CPU cards

10 24 bit decoder cards (for the 550)

Design of the input card will be done by NASA engineering.

The design will use the standard CMUX interface for input cards.

VME interface.

PDB interface.

Simulator and associated circuitry.

The rest of the design is to be done by NASA engineering

LDS will assist with design details and documentation for:

Standard CMUX circuitry

Xilinx design advice

Requirements

Block level design

Design can be done on paper by NASA then input into the LDS Cadence system by LDS.

Simulation would require NASA travel, however this can be minimized by simulation definition and preplanning.

PCB layout will be done at LDS.

LDS action items Preliminary functional block diagram and description for <u>Overall system</u> <u>ADAS</u> Hardware Data flow Software Preliminary schedule and budget Received USCA video tape.

1

7

1

Ţ

1

STATUS : 02-10-94

Fage 1 of 4

]

]

T

T

7

٦

Π

Л

]

|                                 |                                                                                             | ·                                                             |                                                   | 1                                                  | 1                                                         | , I                 | 1.2                | -                       | 1.0            | ĕ.                                                                                          | Item             | ۲ <u>۹</u> : |

|---------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|---------------------|--------------------|-------------------------|----------------|---------------------------------------------------------------------------------------------|------------------|--------------|

| Inputs from Loral<br>Mechanical | 30% Specification - (MASA,<br>I-MET, Loral)<br>Preliminary Demign Review                    | VERSION 2 DESIGN<br>Mult1-chip/Rybrid Module<br>Investigation | Finish Version 1 testing<br>Digital Output Design | EHI - SUBCEPTABLILLY (MASA)<br>WILL NOT BE DONG ON | EHI - Andiaced (HASA)<br>WILL NOT BE DONE ON<br>UEGSION 1 | Temperature (I-NET) | Environmental Test | Electrical Test (I-MET) | VERSION 1 TEST | ACCIVICION                                                                                  |                  | DAS          |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | Status                                                                                      |                  |              |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | •                                                                                           | Proj             |              |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | -                                                                                           | •<br>T           |              |

| 5                               |                                                                                             |                                                               | ~                                                 | <u>    []     </u>                                 | -<br>[]                                                   | Ĩ                   |                    | - <b>-</b>              |                | Jan Peb                                                                                     |                  |              |

|                                 |                                                                                             |                                                               |                                                   | <u> </u>                                           |                                                           |                     |                    |                         |                |                                                                                             |                  | PROJECT      |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | A<br>A                                                                                      | 2                |              |

|                                 | (Schematics, tag ram format, µP flow diagram, hierarchimi block diagram for h/w & s/v, stat |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | Ŧ                                                                                           | Flocal Tonr 1994 | SCHEDULE     |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    | ·                       |                | L L                                                                                         | 7 1994           | ULE          |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | Inr<br>1661                                                                                 |                  |              |

| •   •                           | low dlag                                                                                    |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | -                                                                                           |                  |              |

|                                 | gram,                                                                                       |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | Sepe                                                                                        |                  | ATT          |

|                                 |                                                                                             |                                                               |                                                   | •                                                  |                                                           |                     |                    |                         |                | 000                                                                                         |                  | ACHIN        |

|                                 | •                                                                                           |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                |                                                                                             |                  | ATTACKNENT   |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                |                                                                                             | <b>Fise</b>      | 4            |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                |                                                                                             | Flacal Tear 1995 | 4            |

|                                 |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         | [              | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | 3                | 4-13-94      |

| <u> </u>                        |                                                                                             |                                                               |                                                   |                                                    |                                                           |                     |                    |                         |                | -                                                                                           |                  | -94          |

LAR: DAS

TITLE: HIWIATURIZED UNIVERSAL SIGNAL CONDITIONING AMPLIFIER

TITLE: MINIATURIZED UNIVERSAL SIGNAL CONDITIONING AMPLIFIER

. ·

,

PROJECT SCHEDULE

| CTATIIC. | 4.2            | 4.1                   |                                           | 3.0<br>R                         | 2.11                             | 2.10              |                |                | 2<br>.9               | 2.8                  | 3.7                       | N. 6       | 2.5               | <b>-</b> .             |            | ð         | 1                |

|----------|----------------|-----------------------|-------------------------------------------|----------------------------------|----------------------------------|-------------------|----------------|----------------|-----------------------|----------------------|---------------------------|------------|-------------------|------------------------|------------|-----------|------------------|

|          | Test Version 2 | Build 5 Units (I-NET) | VERSION 2 DESIGN, BUILD & TEST -<br>I-Net | RELEASE VERSION 2 DESIGN PACKAGE | Version 2 Critical Design Review | 60% Specification | Environmental  | Electrical     | Write Test Procedures | Create S/W Documents | Create Hechanical Drawing | Revise PCB | Revise Schematics | I-NET Review of Inputs | Components |           | ACE!V1E100       |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           |            |                   |                        |            |           | Statum Proji     |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           |            |                   |                        |            | 1 Compli— | Proji 1          |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           |            |                   |                        |            | 511       |                  |

|          |                |                       |                                           |                                  |                                  | •                 | =              | -              |                       | 5                    |                           | -          | -                 |                        |            | 3         |                  |

| _        |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           |            |                   | -                      |            | H         |                  |

|          |                | <u>=</u> [            |                                           | ٥٣                               | 3 <sup>0</sup> 33                | []                |                |                |                       | []<br>               | []<br>[]                  | []<br>     | ן<br>ב            | Ĩ                      |            | Apr       | [iee             |

| •        |                | ั <sup>บ</sup> ะ      |                                           |                                  |                                  |                   | บ <sub>ะ</sub> | Ш <sub>Е</sub> |                       |                      |                           |            |                   |                        |            | Hay       | Flocal Vear 1994 |

|          |                |                       |                                           |                                  |                                  |                   | ·              |                |                       |                      |                           |            |                   |                        |            | 5         |                  |

|          |                |                       |                                           |                                  |                                  |                   | • • • • • •    |                |                       | · <b>-</b>           |                           |            |                   | <b></b> .              |            | Jul A     |                  |

|          |                | · · ·                 |                                           |                                  |                                  |                   |                | •···•          |                       | · <b>-</b>           |                           |            | <b>.</b>          |                        |            | Aug Sept  |                  |

|          |                | <b></b>               |                                           |                                  | •                                |                   | ·              |                |                       | x =                  |                           |            |                   |                        |            | pt Oct    |                  |

|          |                |                       |                                           |                                  | <b></b> .                        |                   |                |                | ·                     |                      |                           |            |                   |                        |            | C Nov     |                  |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           | ·          |                   |                        |            | - Dec     | <b>Flace</b>     |

|          |                |                       |                                           |                                  |                                  | • • ·             |                |                |                       |                      |                           |            |                   |                        |            |           | Flacal Year 1995 |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           | -          |                   |                        |            | · feb     |                  |

|          |                |                       |                                           |                                  |                                  |                   |                |                |                       |                      |                           |            |                   |                        | •••• ••    | H#7       |                  |

-

----

Ⅎ

-

-

7

7

٦

| LAB: | TITLE:                                                |

|------|-------------------------------------------------------|

| DAS  | " MINIATURIZED UNIVERSAL SIGNAL CONDITIONING AMPLIFIC |

|      | UNIVERSAL                                             |

|      | SIGNAL                                                |

|      | CONDITIONING                                          |

|      | ANPLIFIC                                              |

ł

PROJECT SCHEDULE

(

| Trea a           |            | 9.1 Build | 8.2 Test | 8. ] Revise | 8.4<br>Release |       |        |   |                                       |      |      |      |   |

|------------------|------------|-----------|----------|-------------|----------------|-------|--------|---|---------------------------------------|------|------|------|---|

| Activitie.       |            |           |          |             |                |       |        |   |                                       |      |      |      |   |

| 35. CU           |            |           |          |             |                |       |        |   |                                       |      |      |      |   |

|                  | •  comp1 - |           |          |             |                |       | -      | · |                                       |      |      |      | · |

|                  | Jan   1.6  |           |          |             |                |       | -      |   |                                       |      |      |      |   |

|                  | · * ***    |           |          |             |                |       |        |   |                                       | <br> |      |      |   |

| Flackl Year 1994 | Apr Hay    |           |          |             |                |       |        |   | · · · · · · · · · · · · · · · · · · · |      |      |      |   |

| 16               | 1994       |           |          |             |                | _     |        |   |                                       |      |      |      |   |

|                  | Jul . Aug  | -         |          |             |                | . –   |        |   |                                       | <br> | <br> | <br> |   |

|                  | Sept       |           | ···      | ·           |                |       |        |   | ······                                | <br> | <br> | <br> |   |

|                  | Oct Nev    |           |          | =           |                |       | • -•·· |   |                                       | <br> | <br> |      |   |

|                  |            |           | ••• †•   |             |                | -[-   |        |   |                                       | <br> |      |      |   |

| Flocal Year 1989 | 0ea        |           | U        |             | <u>ة</u><br> ] | <br>' |        |   |                                       | <br> | <br> | <br> |   |

Page 4 of 4

STATUS: 02-10-94

----

-

$\dashv$

$\dashv$

-

.

٦

\_\_\_\_\_

7

7

TITLE: MINIATURIZED UNIVERSAL SIGNAL CONDITIONING AMPLIFIER Lab: DAS

l

l

PROJECT SCHEDULE

| (LOFBI)<br>1.4 Revise VERSION 3 (I-NET, LOFBI)<br>1.5 90% Specification<br>1.5 90% Specification<br>1.6 PRIEASE VERSION 3 DESIGN PACEAGE<br>1.0 RELEASE VERSION 3 DESIGN PACEAGE<br>1.0 RELEASE VERSION 3 DESIGN PACEAGE<br>1.1 Build 5 Units (LOFBI)<br>5.1 Build 5 Units (LOFBI)<br>5.2 Test<br>Electrical (I-NET)<br>Electrical (I-NET)<br>Electrical (I-NET)<br>Electrical (I-NET)<br>5.3 Revise LOFBI Package<br>(I-NET, LOFBI)<br>5.4 100% Specification<br>5.0 COMMERCIAL PACEAGE<br>5.0 COMMERCIAL PACEAGE<br>5.0 COMMERCIAL PACEAGE | Enectical (1-MET)<br>Environmental (EMT, Temp.,<br>Vibraton, etc.) MASA<br>Enter Version 2 Design Package | Statud bio                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           | Jon 1 Feb 1 Mag                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -<br>                                                                                                     | Flocal Year 1994                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ╌┝─║╺┼╴║╺<br>╧╎──╶╴                                                                                       | r 1994<br>  Jun   Jul                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                                     | - Aug Sept                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           | <br>Oct                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           | Flacel Yeer 1995<br>Hov Dec <sup>1</sup> Jen |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           | Jan 7eb                                      |

l

-

-

-'

7

1

7

7

٦

٦

7

7

Ĺ

Fr: Dean R. Becker Re: USCA milestone 2

7

٦

٦

ł

LTIS has input all USCA schematics and parts lists and has delivered the current package with questions to NASA. We have also assisted with the overall design of the USCA as well as the system with which it operates (ADAS). See the attachment A. Included is an updated project schedule for the USCA development. See Attachment B.

761 MAJ :

## From Dean Becker April 25 - 27 meetings with NASA/I-NET

**USCA** Design review

Distribution

USCA specifications

Updated schedule

Hardware documentation

Software documentation

Due to recent cost estimates for the USCA, numerous tradeoffs are being considered. This affects the specifications. It also affects the USCA schedule.

Possible changes being considered to reduce the price of the USCA.

Use components with commercial temperature range (0 to 70 degrees C).

This needs to be checked with respect to internal heating in the USCA and actual requirements for case temperature range.

Use single input channel as opposed to the A/B channel calibration scheme.

This reduces overall gain and offset calibration over

temperature. This could be compatible with a system requiring only 10 or 12 bits of accuracy.

Use DSP chip only and remove the other microprocessor and its support chips.

This only requires new firmware to be written for the DSP chip.

Two EPROMS will need to be added to the DSP circuitry.

Replace 16 bit A/D with 12 bit A/D.

The 12 bit A/D is half the price of the 16 bit. Accuracy is compromised.

Remove the DDF chip.

Filtering up to 2 kHz can be done in the DSP chip. This compromises use with certain vibration sensors. A 60 Hz analog notch filter will need to be added. Extra code needs to be added to the DSP chip.